项目场景:

Create a 100-bit binary ripple-carry adder by instantiating 100 full adders. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out. To encourage you to actually instantiate full adders, also output the carry-out from each full adder in the ripple-carry adder. cout[99] is the final carry-out from the last full adder, and is the carry-out you usually see.`

Module Declaration

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

问题描述

通过实例化100个满加法器来创建一个100位二进制波纹进位加法器。加法器将两个100位的数和一个进进数相加,产生一个100位的和并执行。为了鼓励您实际实例化完整的加法器,还需要在波纹进位加法器中输出每个完整加法器的进位。Cout[99]是最后一个完整加法器的最终执行,也是你通常看到的执行。

@Override

public void run() {

bytes = mmInStream.read(buffer);

mHandler.obtainMessage(READ_DATA, bytes, -1, buffer).sendToTarget();

}

原因分析:

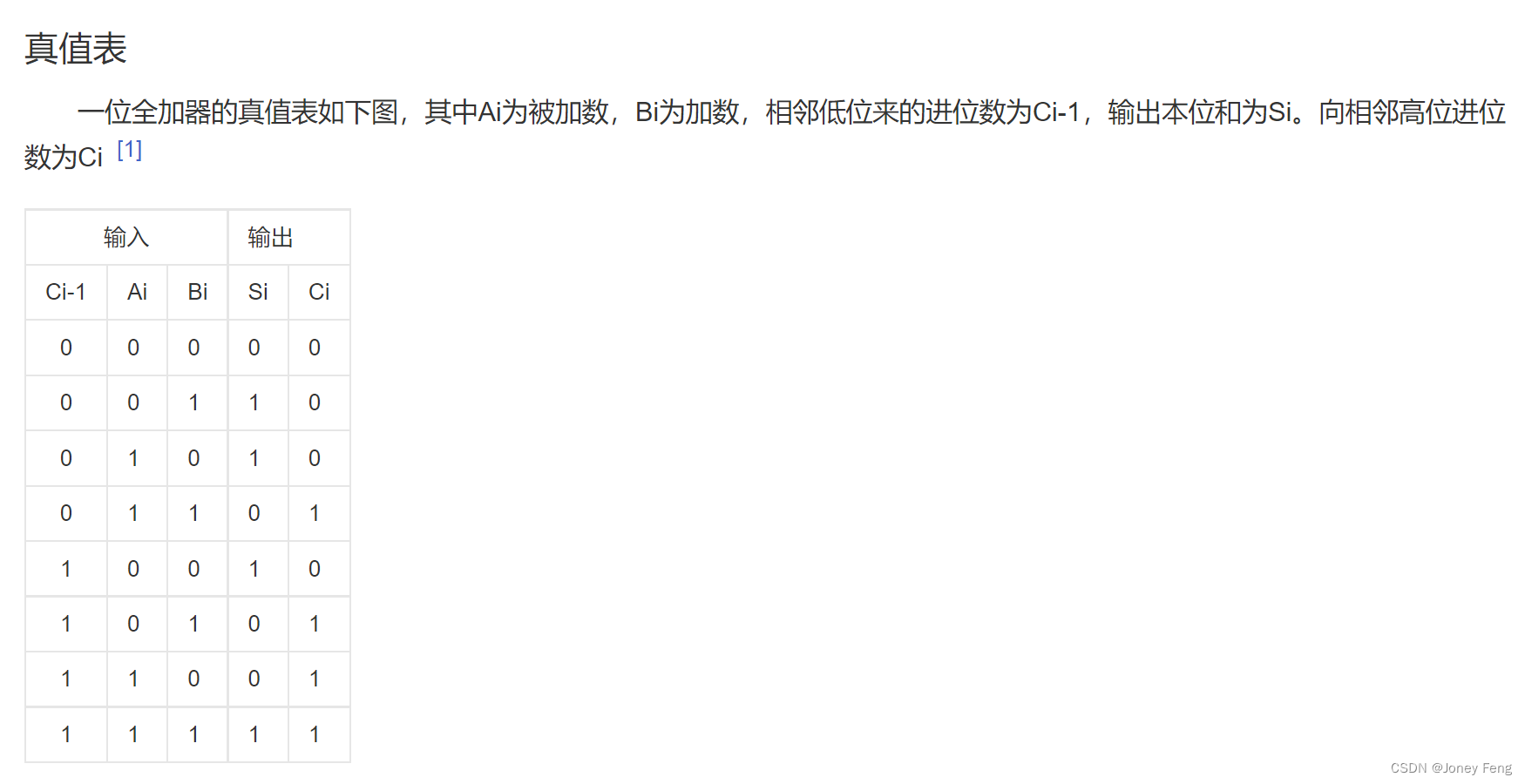

(Figure 2: Source from Baidu Baike)

Si=Ai ^ Bi ^ Ci-1;

Ci = (Ai&&Bi) || (Ci-1&&(Ai || Bi));

Ci = (Ai&&Bi) || (Ci-1&&(Ai ^ Bi));

{cout,sum} = a + b + cin;

解决方案:

方法一:使用generate函数,实例化fuu_adder100次即可

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

genvar i;

generate

for(i=0;i<100;i=i+1)

begin

:Adder100i

if(i==0)

full_adder full_adder_inst1

(

.a(a[0]),

.b(b[0]),

.cin(cin),

.cout(cout[0]),

.sum(sum[0])

);

else

full_adder tfull_adder_inst2

(

.a(a[i]),

.b(b[i]),

.cin(cout[i-1]),

.cout(cout[i]),

.sum(sum[i])

);

end

endgenerate

endmodule

module full_adder(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

本文介绍如何通过实例化100个满加法器创建100位二进制波纹进位加法器,并详细解释了模块声明、原因分析及解决方案。文中还提供了具体的Verilog代码实现。

本文介绍如何通过实例化100个满加法器创建100位二进制波纹进位加法器,并详细解释了模块声明、原因分析及解决方案。文中还提供了具体的Verilog代码实现。

172万+

172万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?