一种用于可靠且低功耗的静态随机存取存储器设计的电荷回收辅助技术

摘要

本文提出了一种新型电荷回收SRAM辅助电路,用于降低SRAM辅助技术的动态功耗。通过协同结合读辅助和写入协助技术,传统读辅助电路中的浪费的电荷可以在写入协助技术中得到有效回收。为了在相同最小工作电压(VMIN)条件下比较动态功耗,使用14纳米FinFET技术模型进行了最可能失效点(MPFP)仿真。与传统的辅助方案相比,得益于电荷回收,采用所提出的SRAM辅助电路可实现41%的节能以及2.3%的面积缩减。

索引术语

辅助技术,电容耦合,电荷回收,读取稳定性,静态随机存取存储器,变异,写入能力。

一、引言

现代微处理器和片上系统(SoC)为了满足系统性能需求,对嵌入式存储器的需求日益增加,导致静态随机存取存储器所占的芯片面积急剧上升[1]。这一趋势促使SRAM设计人员致力于实现更高的集成密度以及更低的功耗。在纳米级CMOS技术中,由于积极的面积缩放,片上SRAM存储器对工艺变异变得极为敏感,尤其是在低电压运行模式下。当采用FinFET工艺时,这种情况更加严重,因为FinFET的宽度量子化限制了其精细调节以获得最佳位元尺寸的能力。此外,晶体管P/N比率的降低由于传输门NMOS(PG)与上拉PMOS(PU)之间的竞争加剧而使内在写入限度退化[2]。由全耗尽鱼鱼引起的体偏置效应减弱也使得可靠SRAM设计的一种解决方案失效[2]。

为了克服设计挑战,已有若干研究致力于SRAM辅助技术。作为写入协助技术,瞬态电压裱落(TVC)[3],[4],字线过驱动(WLOD)[5],[6]和负位线(NBL)[7],[8]此前已被提出。在这些方法中,通过暂时减少PG和PU晶体管之间的写入竞争,可显著提高静态随机存取存储器的写入能力。类似地,可通过缓解PG与下拉(PD)晶体管之间的读竞争来辅助静态随机存取存储器的读操作。这些读辅助操作可通过电源电压提升( VBS)[9],、字线欠驱动(WLUD)[3],[8]和/或抑制位线(SBL)[10],[11]方法实现。

为了实现SRAM辅助技术[3]–[11],,需要专用电路,例如分压器和电荷泵,或外部电压源。尽管这些电路已经以成本效益较高的方式被设计来降低 VMIN,但由于辅助电路带来的开销,功耗部分的增加仍然相当可观。为了降低写入协助技术的功耗,文献[12],中提出了一种选择性 NBL写辅助方法,该方法通过在位线(BL)对中使用写入失败检测器,仅在写入失败列中执行写入辅助。在[13],中提出了一种电荷共享TVC,以消除静态偏置电流。通过将选定列中的单元供电电压(VCS)连接到预放电电容节点,可以在没有静态偏置电流的情况下生成塌陷电压。在设计低功耗SRAM辅助技术时遇到的一个困难是,目前尚无针对各种辅助技术[3]–[11]的全面功耗分析或设计指南。

尽管基于静态噪声容限(SNM)[14],、基于最可能失效点(MPFP)[15]–[17],以及基于硅片数据[18]的SRAM功能失效分析已经比较了各种辅助技术的有效性,但在先进CMOS工艺下,关于辅助持续时间、ISO‐VMIN条件下的功耗等方面的详细功耗与性能分析,对于低功耗和可靠SRAM设计而言仍十分必要。

本文中,我们基于MPFP估计对读/写SRAM辅助技术进行了广泛的分析,以研究各种技术对SRAM功耗的影响。首先,在14纳米FinFET技术[19]下应用多种辅助配置,以获得SRAM辅助技术的 VMINs。基于该分析,提出了一种新型的电荷回收SRAM辅助电路,以降低辅助技术的动态功耗。在所提出的电荷回收方法中,通过结合读取和写入辅助方案,传统SBL技术中浪费的电荷可以在不增加显著面积开销的情况下有效地在NBL中回收。此外,还给出了不同SRAM辅助技术的ISO‐VMIN 功耗结果,以展示所提出的电荷回收SRAM辅助技术的优越性。

二、传统SRAM辅助技术的设计考虑

A. 传统SRAM辅助技术

表I展示了传统SRAM辅助技术的总结性硬件成本及其缺点。用于辅助技术的专用电路也在表中列出。在 TVC电路[4],中,部分上拉器件(PB[2: 0])和下拉器件(NWR)同时导通以拉低V CS ,从而产生静态偏置电流。尽管这种面积高效的方法有助于简化TVC技术的实现,但静态偏置电流可能导致功耗显著增加。作为一种字线调制方法,WLOD方案[5]可用作写入协助技术。通过使用本地集成的电荷泵和电平移位器,可提高写入能力以及读取性能。

在读解耦8T(RD‐8T)SRAM[5]中,性能得到了提升。然而,列交错式SRAM中半选单元的读干扰可能会限制其适用性。作为一种替代的写入辅助技术,可在写驱动器中采用NBL方案[8]。在此专用电路中,使能信号(EN_NBL)的下降沿通过电容耦合产生负耦合电压(NVSS)[8]。与字线过驱动方法类似,为了产生升压电压, NBL在耦合电容充放电过程中会消耗大量功率。

作为一种读辅助技术,VBS方案[9]通过提高单元供电电压(VCS)来缓解读干扰。由于在写操作期间半选单元也需要读辅助(读:所有列,写:未选中的列),因此很难通过片上电荷泵改变 VCS电平。出于这一原因,在依赖双电源供电的先前实现中,本地 VCS线通过基于列的多路复用器连接到两个全局电源(VCS.Hi、 VCS.Lo)之一。

在WLUD方法[8],中,为了生成欠驱电压,当上拉 PMOS器件导通时,使用控制信号(TRIM)对下拉 PMOS器件进行偏置。尽管欠驱的字线电压减轻了读干扰,但所选单元的读电流和写电流降低,导致在最差工艺角[8]下发生操作失败。此外,类似于TVC,生成欠驱电压的静态偏置电流可能引起显著的功耗开销。在SBL方案[11],中,在完成位线预充电后,干扰噪声抑制(DNR)信号被启用以放电位线对。与TVC和WLUD方案不同,SBL在上拉器件关闭的同时导通下拉器件,从而形成调整电压。由于在读操作期间无需将辅助电压恢复至 V DD,因此在激活期间可以避免静态偏置电流。然而,降低的位线电压电平会导致预充电操作的功耗增加。过大的被抑制的位线电压还会因放电存储节点中保持“1”的电荷而导致稳定性丧失。

B. 最大概率失效点仿真的框架

在对静态随机存取存储器辅助技术进行全面分析之前,本节首先介绍了最大概率失效点仿真的详细框架。基于这一基础,下一节将研究依赖于各种静态随机存取存储器辅助特性的 VMIN值。由于静态随机存取存储器的VMIN和功耗在很大程度上取决于辅助电压水平和脉冲宽度,因此我们还预先定义了特定的辅助配置。

图1展示了最大概率失效点仿真的基本框架。为了考虑三栅晶体管对静态随机存取存储器可靠性的影响,采用预测技术模型(PTM)[19]的14纳米FinFET来构建一个传统的六晶体管静态随机存取存储器单元。详细的工艺参数如图1(b)所示。对于PU、PG和PD晶体管的鳍片数量,在高密度结构(HDC)下采用1:1:1 (PU: PG : PD) 的配置。与之前的MPFP方法[15]–[17],相同,假设每个晶体管具有独立的阈值电压(VTH)变异,其服从均值为零、标准差为30 mV的正态分布。在下文中, VMIN指的是在任何工作条件下满足10−9位错误率(BER)的最小工作电压。这可在1‐MB SRAM数组上实现90%的成品率。字线(WL)脉冲宽度和位线电容分别采用放大4倍(50 FO4)延迟(0.8 V时为 ≈415ps)和15 fF(128个单元)。此处,为了避免使用 WLUD技术时频繁出现感知失败,选择50 FO4延迟作为字线脉冲宽度,该延迟在正常字线激活期间刚好能够产生全幅比特线电压。

此外,图2还展示了多种静态随机存取存储器失效机制的主导(最坏情况) ΔV TH方向[15]以及特定的静态随机存取存储器辅助配置。对于操作失败的主导ΔV TH 方向,假设图1中所示的Q和Qb初始分别存储“1”和“0”。各个失效机制的主导 ΔV TH 方向可解释如下:当图1(a)中所示的PUL和PDR晶体管由于工艺变化而变强时,所存储的值(Q=“1”和 Qb=“0”)

SRAM操作中几种失效机制的主要 ΔVTH方向。(b) 传统 SRAM辅助技术上的具体配置。)

SRAM操作中几种失效机制的主要 ΔVTH方向。(b) 传统 SRAM辅助技术上的具体配置。)

在交叉耦合反相器中被牢牢保持。此外,图1(a)中较弱的传输门晶体管PGL和PGR降低了可访问性。PUR和PDL 的高VTH使其难以导通,而在写入数据时,Q节点电压下降,Qb节点电压上升。在此器件条件下,最常发生写入失效。这在图2(a)中进行了总结,其中正号表示较弱的器件(较高的 VTH),负号表示较强的器件(较低的VTH)。

另一方面,当使用TVC和NBL技术作为写入辅助时,选定列中的半选单元容易发生保持失效。在这些情况下(采用 TVC的半选(H/S)单元和采用NBL的半选(H/S)单元),导致保持失效的主要ΔVTH方向与写操作的方向相反,因为在此情况下存储节点(Q和Qb)更容易翻转。

导致读取干扰发生的主要 ΔV TH方向可以以类似方式获得。考虑到数据保持,在读操作期间,具有TVC的半选单元和具有NBL的半选单元对数据保持有正面影响,而较弱的PGL由于使位线和Q节点被充至相同的 V DD 电平,从而恶化了数据保持。因此,在读操作情况下,PGL器件在图2(a)中显示为正号。对于读取失效

C. 基于各种辅助技术的 VMIN比较

本节介绍了基于MPFP动态稳定性估计的各种辅助技术的VMIN比较。通过考虑辅助配置(辅助电压水平和脉冲宽度)对 VMIN的影响,本节研究了ISO‐VMIN条件。这些ISO‐VMIN条件将在第四节中用于验证所提出的静态随机存取存储器辅助技术的有效性。

通过针对各种辅助配置的仿真(ΔVASST :10% ∼ 50%,ΔTASST :对于20 FO4字线脉冲宽度为4 FO4 ∼ 16 FO4,对于50 FO4字线脉冲宽度为10 FO4 ∼ 40 FO4),研究了V MIN 值,仿真结果如图3和图4所示。图3(a)显示了写入‐VMIN(浅色标记)随TVC的 ΔVASST从10%变化到50%的情况。图3(a)还显示了保持‐VMIN(深色标记)随HS_TVC( ΔVASST)从30%变化到50%的情况。在具有短(20 FO4字线脉冲宽度)和长(50 FO4字线脉冲宽度)字线脉冲宽度的TVC中,当塌陷单元的供电电压(VCS)接近PU器件的阈值电压[时,图3(a)中TVC 20%的写入‐VMIN显著低于TVC 10%的情况。由于当TVC降至 VCS= 0.5 V或以下时,PU器件进入亚阈值区(选定列中单元的内部节点变为浮空状态)[4],,交叉耦合反相器的数据保持能力减弱,导致写入‐VMIN显著降低。然而,当TVC的 ΔVASST超过 VDD的20%时,写入‐VMINs稳定在约0.5 V附近。根据基于N曲线的SRAM稳定性度量[20], ,上拉 PMOS晶体管对写入失效的贡献小于传输门NMOS晶体管。塌陷的 VCS在大多数VTH偏斜条件下也位于静态数据保持电压[4]之下,采用TVC 20%配置时。基于这些原因,即使施加足够的 ΔVASST,TVC的效果也可视为已达到饱和。考虑到字线脉冲宽度对TVC写入‐VMINs的影响,较短的辅助持续时间(在20 FO4字线脉冲宽度下为4 FO4或8 FO4)不足以有效辅助写操作。对于图3(a)中以HS_TVC表示的TVC保持‐VMINs,半选单元的数据保持限制在约0.2 V[,对应于图3(a)中保持‐VMIN ≈ 0.4 V和HS_TVC 50%的点]。当辅助持续时间受限于短字线脉冲宽度 (20 FO4)时,与长字线脉冲宽度(50 FO4)下的 TVC写操作相比,观察到相对更小的保持‐VMINs。

如图3(b)所示,WLOD在短和长字线脉冲宽度下均能有效降低写入‐VMIN。然而,在大多数辅助配置中,半选中单元的写入能力和可靠性可能不平衡,除非 ΔVASST和 ΔTASST分别设置为VDD的10%(WLOD 10%)和 40 FO4,且字线脉冲宽度为50 FO4 WL脉冲宽度。尽管当ΔTASST1增加[时,WLOD的伪读取‐VMIN可进一步降低,如图2(b)所示,但其最小值受限于读取‐VMIN。与 TVC类似,NBL情况下ΔTASST的影响可以忽略不计,如图3(c)[所示,这意味着VMIN不随变化的 ΔTASST而改变。考虑到写入协助技术中的 VMIN降低,ΔTASST的变化仅在静态随机存取存储器操作依赖于位线电压时才有效,如图3(b)中的情况所示(HS_WLOD曲线)。另一方面,写入‐VMIN、保持‐VMIN以及伪读取‐VMIN随着 ΔV ASST的变化而显著变化,如图3所示。

图4还展示了在采用不同 ΔVASST 和 ΔTASST 的各种辅助技术时,读取‐VMIN 的仿真结果。首先,图4(a)说明了使用体偏置(VBS)对读取‐VMIN 的改善效果。如20 FO4字线脉冲宽度以及50 FO4字线脉冲宽度下10 FO4的 ΔTASST 情况所示,当V CS 过早恢复到 V DD 时,体偏置(VBS)对V MIN改善的效果未能达到饱和。在这种情况下,由于 V CS 在产生足够的电压差之前就已恢复在位线对中进行读取时,较短的辅助持续时间会导致更严重的读取‐VMIN 。对于WLUD [图4(b)],,当ΔVASST超过 VDD的20%(WLUD 20%)时,无论是在短字线还是长字线情况下,该辅助技术的有效性都会降低。由于位线电压差不足在MPFP仿真中也可被视为读取失效,过大的 ΔVASST会增加基于WLUD的读取‐VMIN。此外,由于 WLUD导致读取电流(IREAD)减小,与基于VBS的读操作相比,读取‐VMIN对位线的依赖持续时间更长。对于 SBL [图4(c)],,当 ΔVASST达到30%时,使用20 FO4字线脉冲宽度下的读取‐VMIN得到改善。在50 FO4字线脉冲宽度的情况下,读取‐VMIN在ΔVASST达到40%之前均有改善。由于过度抑制的位线电压会放电存储“1”值的内部节点,从而威胁读操作,因此可用的 ΔVASST被限制在这些数值范围内。此处,SBL 40%表示传输门NMOS 的漏源电压低于SBL 30%的情况,可在长字线脉冲宽度下产生足够的位线差值,这明显表明最佳辅助强度会随字线脉冲宽度的变化而发生偏移。从图4所示结果可以看出,为了确定最佳读取辅助配置,必须同时考虑读辅助的 ΔVASST和ΔTASST。

D. SRAM辅助技术与ISO-VMIN配置组合的影响

在本小节中,重新考虑了针对读和写操作的SRAM辅助技术。基于列交错式SRAM,还研究了最优辅助组合中的ISO‐VMIN配置。需要注意的是,位交错方案由于伪读取和列多路复用器会引入额外的功耗和延迟,在低级缓存 (如L0或L1)的情况下可能并非必要。另一方面,由于列交错允许单元I/O和多位错误保护的布局约束更少,大多数SRAM设计采用列交错[21]。

表II展示了可能的读写辅助技术组合及其辅助组合方式。如图5(a)所示,考虑到列交错的六晶体管静态随机存取存储器结构,在读操作期间,读写辅助组合之间不存在冲突。然而,在写操作情况下[图5(b)],,由于写操作涉及半选列中的伪读操作,因此需要同时进行写辅助和读辅助。因此,当使用字线调制(字线过驱动或字线欠驱动)作为辅助技术时,读辅助与写辅助之间不可避免地发生重叠,导致辅助技术性能退化。这些辅助组合的方式在表II中进行了总结。为了简化对读写辅助技术组合的V MIN分析,体偏置被排除在考虑之外,因为体偏置需要显著的功耗开销来提升多条 V CS 线路,如图5所示。因此,字线过驱动方法也不予考虑,因为它会显著劣化伪读‐V MIN 。在写操作期间,当使用字线欠驱动来防止半选单元中的读干扰时,写入能力

| 表II | 读写辅助组合的影响 |

|---|---|

受TVC或NBL辅助的被选单元由于字线电压降低而受到损害。根据最大概率失效点仿真(ΔVASST:10% ∼ 50%, ΔTASST:10 FO4 ∼ 40 FO4),研究了静态随机存取存储器操作的 VMIN边界,以获得辅助技术的设计指南。图6展示了读写辅助组合(WLUD + TVC、WLUD + NBL 和 WLUD + SBL)的数值结果。在此图中,当TVC的辅助配置由弱变强(ΔV ASST:10%,ΔT ASST:10 FO4→ΔV ASST :50%,ΔT ASST :40 FO4)时,写入‐V MIN 边界从0.63 V变为0.47 V(标记为TVC的黑色框)。另一方面,保持‐VMIN 边界从0.30 V变为0.40 V(使用 “HS_”作为前缀表示)。类似地,在NBL情况下,当NBL辅助配置由弱变强时,写入‐VMIN 从0.64 V变为0.30 V,而保持‐VMIN 则向相反方向变化

表III ISO‐VMIN(0.5 V)的可用的SRAM辅助配置

0.30 V 至 0.48 V。然而,由于写入‐VMIN边界(NBL)与保持‐VMIN边界(HS_NBL)之间的重叠面积(图6),NBL 配置必须确定为同时满足写入‐VMIN和保持‐VMIN的要求。当使用WLUD进行读辅助时,由TVC或NBL提供的写入能力会退化,因此也需考察其与WLUD的组合效果。在弱WLUD条件下(ΔVASST:10%,ΔTASST:10 FO4),WLUD与TVC和WLUD与NBL的组合分别观察到 66 mV和57 mV的写‐VMIN低边界增加。尽管通过增加字线脉冲宽度和写辅助持续时间可以缓解WLUD引起的写‐VMIN退化,但这可能导致性能损失和额外功耗。对于 WLOD,由于伪读‐VMINs位于写‐VMIN之上(大于写‐VMIN),因此WLOD技术仅可用于非列交错式SRAM。与写入协助技术相比,读辅助技术表现出较窄的 VMIN边界,除非采用VBS。为了实现更激进的VMIN降低,可在读操作中同时使用WLUD和SBL。在我们的仿真中,通过结合 WLUD和SBL,可实现43 mV更低的读‐VMIN。

根据图6所示的SRAM辅助组合的V MIN 结果,最优的辅助组合和配置可总结如下:当目标应用需要较高性能(超‐VTH 操作 ≥ 0.55 V)时,仅采用写入辅助即可确保可靠的SRAM操作。当低功耗应用需要激进的电压缩放时(用于低于或接近‐VTH操作 ≤ 0.55 V的情况),可以以成本效益较高的方式同时采用写和读辅助技术。获得极低 VMIN(∼0.4 V)的唯一方法是选择VBS与NBL的组合。然而,如第II‐C节所述,VBS带来的较大功耗可能会掩盖降低 VMIN效应所带来的优势。为了找到最佳的辅助组合,应从 VMIN、性能和辅助开销等方面对各种辅助组合进行研究。由于许多高能效应用都考虑了接近‐VTH的操作[22]– [24],我们将静态随机存取存储器的工作电压目标设定为 0.5 V。在此ISO‐VMIN下的可用辅助配置汇总于表III中。在下一节中,所提出的电荷回收静态随机存取存储器辅助技术将与表III中所示的信息进行比较。

一种用于可靠且低功耗的静态随机存取存储器设计的电荷回收辅助技术(续)

三、提出的串联助力技术

A. 电荷回收SRAM辅助技术

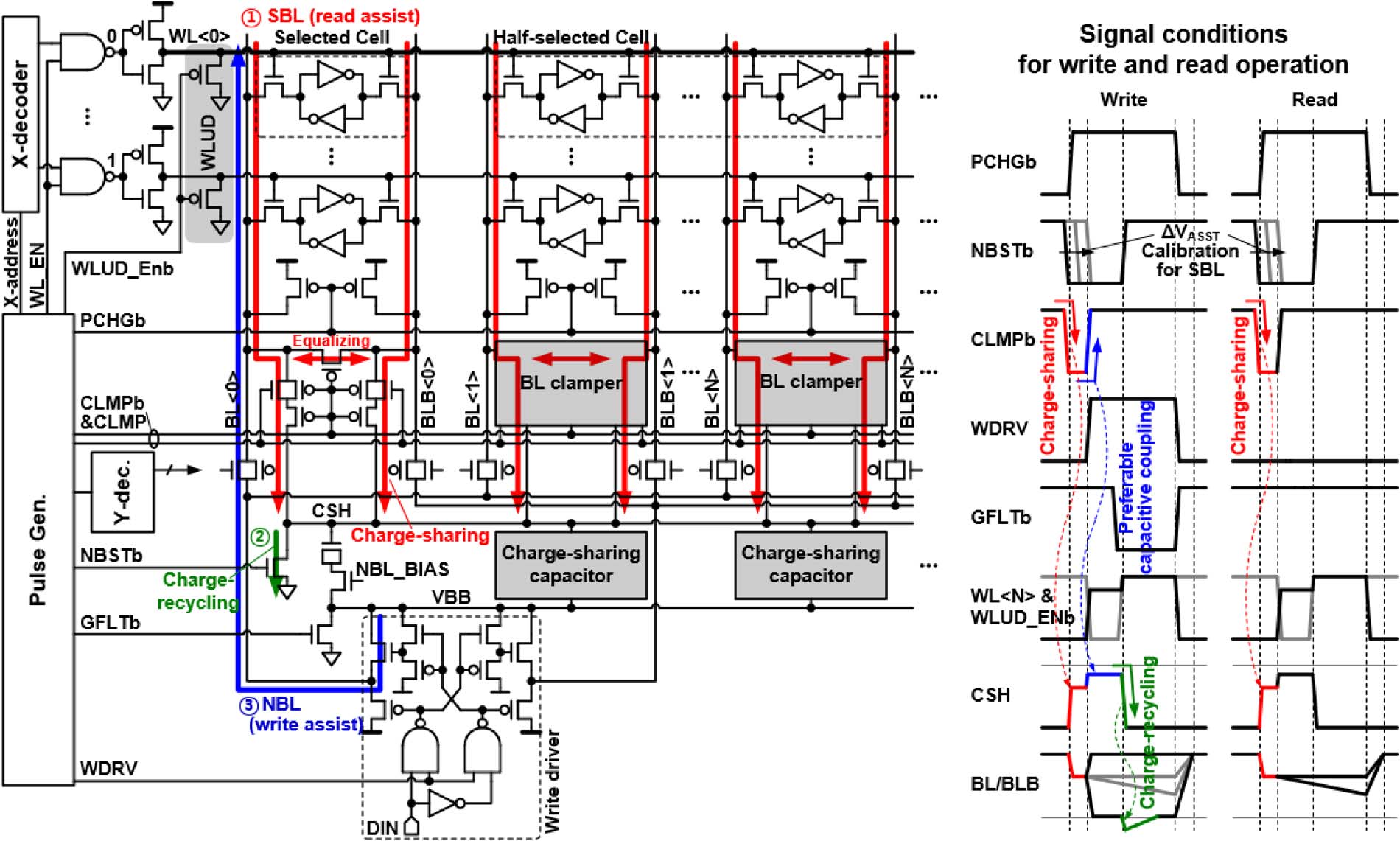

图7展示了所提出的电荷回收SRAM辅助技术的原理图和时序图。其基本思想是,预充电位线上存储的电荷在传统的SBL中直接耗散,而该技术可将其重新用于NBL技术,从而降低辅助功耗。如图7所示,除了传统的列外围电路(预充电电路、列交错多路复用器和写驱动器)外,所提出的电荷回收SRAM辅助电路还增加了位线钳位器和电荷共享电容。具体操作如下:在写操作和读操作之前,位于位线钳位器与电荷共享电容之间的电荷共享节点(CSH)被预放电至0 V(VSS)。此时,位线对预充电至 VDD。当写入或读取操作开始时,位线钳位器由钳位使能(CLMP)信号激活。随后,位线对中存储的电荷流入电荷共享电容(初始为 VSS),直到位线对和CSH节点的电压电平相等。根据位线对与CSH节点之间的电容比,可确定该被抑制的位线电压电平。

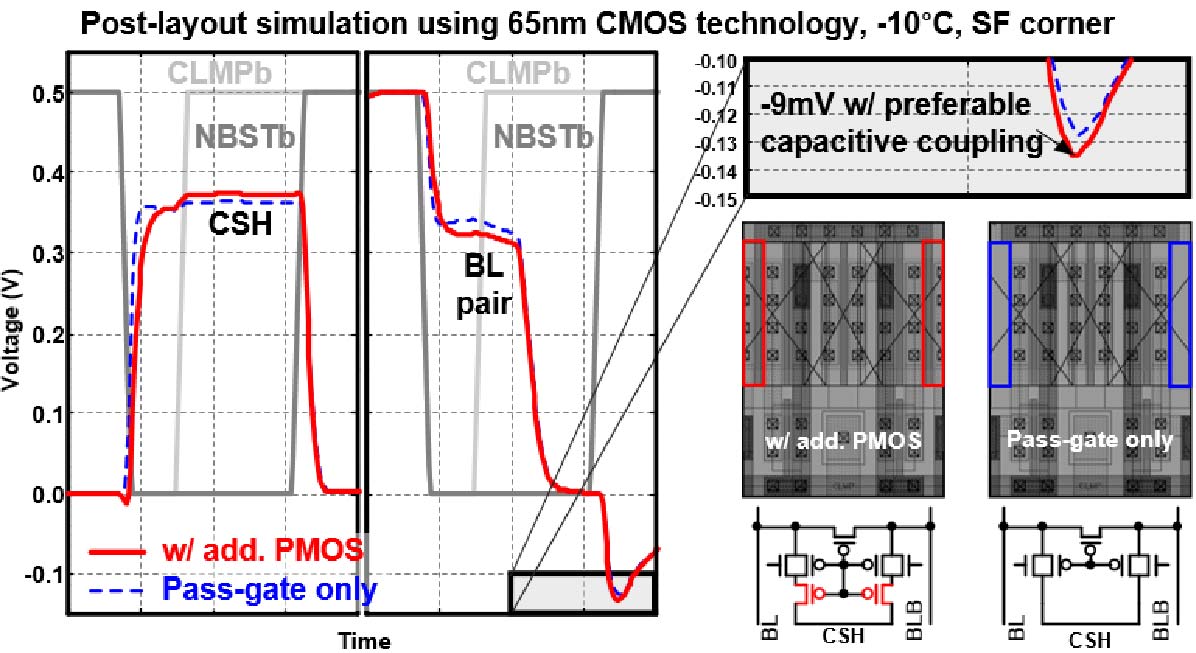

对于写入辅助,负电压通过回收CSH节点中存储的电荷来产生。在位线钳位器中的电荷共享之后,写驱动器使能信号(WDRV)被激活以执行写操作。此时,如图7所示,CLMPb信号的上升沿会提高CSH节点电压。由于 CLMP与CLMPb信号极性相反,直接连接到位线的传输门可减轻电容耦合对位线的影响。在此,为了在NBL写入辅助中产生足够高的升压电压,这种电容耦合是有效的,因为升压电压与初始CSH节点电压成正比。已在65纳米 CMOS技术下通过后布局仿真研究了位线钳位器中附加 PMOS晶体管对NBL电压的影响,结果如图8所示。如图所示,相对于仅使用传输门的位线钳位器,基于优选电容耦合的操作可产生低9 mV的负位线电压。当位线被偏置到所写入的数据时,接地浮动信号(GFLTb)被激活,使CSH节点处于浮空状态。随后,由负升压(NBSTb)信号控制的CSH节点下降沿会在虚拟地(VBB)节点产生负电压。这种基于电荷回收的升压方案可有效降低所提出辅助技术的动态功耗。

B. 所提出的SRAM辅助技术中的被抑制的位线和负位线

通过假设在电荷共享前后,位线和CSH节点(如图7 所示)上的总电荷量保持不变,可以推导出被抑制的位线电压。当位线预充电至 VDD且CSH节点预放电至 VSS时,被抑制的位线电压(VEQ)可表示为

$$

2 \cdot V_{DD} \cdot C_{BL} = 2 \cdot V_{EQ} \cdot C_{BL} + V_{EQ} \cdot C_{CSH}

$$

$$

V_{EQ} = \frac{2C_{BL}}{2C_{BL} + C_{CSH}} \cdot V_{DD}. \quad (1)

$$

这里, $C_{BL}$和 $C_{CSH}$分别表示位线和CSH节点的电容 (归一化到单列的分数,因为仅考虑该列的位线电容)。在CLMPb与CSH节点之间具有耦合电容($C_{CP}$)的情况下,由CLMPb信号的上升沿产生的升压电压($V_{PBST}$) 可表示如下:

$$

V_{EQ} \cdot (C_{CSH} + C_{CP}) = (V_{PBST} - V_{DD}) \cdot C_{CP} + V_{PBST} \cdot C_{CSH}

$$

$$

V_{PBST} = V_{EQ} + V_{DD} \cdot \frac{C_{CP}}{C_{CP} + C_{CSH}}. \quad (2)

$$

最后,由(2)式可知,NBL辅助的负升压电压($V_{BB}$)与共享列多路复用器(YMUX)和VBB节点电容的交错列数 ($N$)相关。

$$

V_{PBST} \cdot N \cdot C_{CSH} = -V_{BB} \cdot (N \cdot C_{CSH} + C_{VBB})

$$

$$

V_{BB} = -V_{PBST} \cdot \frac{N \cdot C_{CSH}}{N \cdot C_{CSH} + C_{VBB}}. \quad (3)

$$

如(1)和(3)所示,NBL($V_{BB}$)的可实现$\Delta V_{ASST}$ 取决于SBL的$\Delta V_{ASST}$ ($V_{EQ}$ 在 $V_{PBST}$ 中)。尽管可以通过调节 $C_{CSH}$ 和/或 $N$来处理这些电压对($V_{EQ}$ 和 $V_{BB}$),但仍需要独立控制以

电荷共享电容大小对所提出方案中SBL和NBL电压的影响如图9所示。如(1)和图9(a)所示,当电荷共享电容的尺寸增大时,由于 $C_{CSH}$增加,SBL电压降低。在后布局仿真中,由于$C_{BL}$包含寄生电容,式(1)中的 $C_{CSH}$项影响减弱,导致SBL电压相比前布局仿真结果更高。电荷共享电容对NBL电压的影响可解释如下:在(2)中,当 $C_{CSH} \gg C_{CP}$时, $V_{PBST}$可简化为 $V_{EQ}$,因此产生的 $V_{BB}$(NBL电压)主要依赖于SBL电压,如(3)所示。因此, 如图9(b)的前布局仿真结果所示,随着电荷共享电容增大 导致SBL电压降低,从而引起NBL电压升高。然而,由于 位线寄生电容使式(3)中的 $C_{VBB}$相对更大,因此在后布 局仿真中,当电荷共享电容较小时(1X和2X),观察到 的NBL电压高于前布局仿真结果。

为了研究子阵列大小对提出的电荷回收SRAM辅助技术的影响,在固定电荷共享电容尺寸(如图9中2X尺寸)连接到单列的情况下,针对不同的阵列配置对SBL和 NBL电压进行了仿真。当每个位线上的存储单元数量增加导致子阵列大小增大时,位线电容自然也随之增加。在这种情况下,如(1)和图10(a)所示,由电荷共享产生的SBL 电压电平也会上升。另一方面,如(2)、(3)和图10(b)所示, 由于 $V_{PBST}$的增加,NBL电压也在增大。当连接到 YMUX的列数增加(即YMUX数量增加)时,用于产生 负电压的可回收电荷量也随之增加。因此,随着YMUX数量的增加,NBL电压变得更大。另一方面,由于位线与电荷共享节点(CSH,归一化至单列)之间的电容比保持不变,因此SBL电压不受YMUX数量的影响,如图10(a)所示。从图10所示的结果可以看出,在0.5 V ISO‐VMIN 辅助配置下采用2X电荷共享电容时,所提出的电荷回收 SRAM辅助方案的最佳子阵列大小为

在每条位线(BL)具有128个单元的子阵列中,使用 YMUX8即可实现。对于较大规模的子阵列(每条BL超过 128个单元),可通过校准电荷共享电容的大小,以找到 最优的0.5 V ISO‐VMIN辅助配置。如图9所示,较大的电荷共享电容可在NBL电压增加的同时逐步降低SBL电压。另一方面,对于较小规模的子阵列(每条BL 64个单元), 需要较小的电荷共享电容以避免SBL电压过高。然而,较小的电荷共享电容在交叉列数量较少时会导致NBL电压不足。因此,需要较多的交叉列来支持小规模的子阵列。

图11展示了适用于所提出的SRAM辅助技术的 $\Delta V_{ASST}$标定方法。在预充电之后,激活CLMPb信号 以利用SBL技术降低已预充电的位线电压电平。此时,通过叠加NBSTb信号可进一步降低 $\Delta V_{ASST}$。当BL钳位器激活后(CLMPb信号设置为VSS),若NBSTb信号保持为 $V_{DD}$,则形成放电路径,进一步拉低位线电压电平。如图11所示,由于该操作是在预充电阶段之后执行的,因此不会产生静态偏置电流,从而在读操作期间不会带来额外功耗。另一方面,可以通过选择性地导通位于电荷共享电容与VBB节点之间的标定晶体管来调节负向升压电压电平。为了研究位线泄露对所提出的静态随机存取存储器辅助方案的影响,进行了采用65 nm的后布局仿真

NBL辅助的最差数据模式。(b) 不同温度和工艺角下BL泄露对SBL和 NBL电压电平的影响。)

在扫频温度和工艺角的情况下,对互补金属氧化物半导体 技术进行了评估。首先,考虑NBL辅助的最坏情况条件, 存储单元阵列的数据模式初始化如图12(a)所示。如图所示,当所选列中的所有单元在负位线侧保持“1”时,从单元到位线的漏电流可能会破坏负电压。对于SBL而言,由于被抑制的位线电压是所有列的平均值,因此SBL辅助的最坏数据模式可以忽略不计。图12(b)还展示了所提出的电荷回收SRAM辅助技术中SBL和NBL电压的仿真结果。如左图所示,由于高温情况下的漏电流高于低温情况,随着工作温度升高,SBL电压降低。关于工艺角,在快 NMOS角(FF和FS角)观察到更显著的被抑制的位线电压。对于NBL,三个主要因素对NBL电压有显著影响:1) 电容耦合量,取决于初始CSH节点电压(电荷共享阶段的 ≈SBL电压);2)位线钳位器中PMOS晶体管的 $V_{TH}$损耗;3)来自SRAM存储单元中存储“1”的节点的漏电流。当温度低于 50 ◦C时,位线钳位器内部PMOS晶体管的 $V_{TH}$损耗效应主要决定了NBL电压电平。另一方面,当温度高于 50 ◦C时,来自SRAM存储单元中存储“1”的节点的漏电流变大,导致在慢NMOS角下NBL电压更小。尽管传统的NBL技术仅受SRAM存储单元中存储“1”的节点漏电流的影响,但较高的初始CSH节点电压以及SF 角下的较小漏电流可使所提出的电荷回收SRAM辅助方案可行。

IV. 静态随机存取存储器辅助的硬件成本

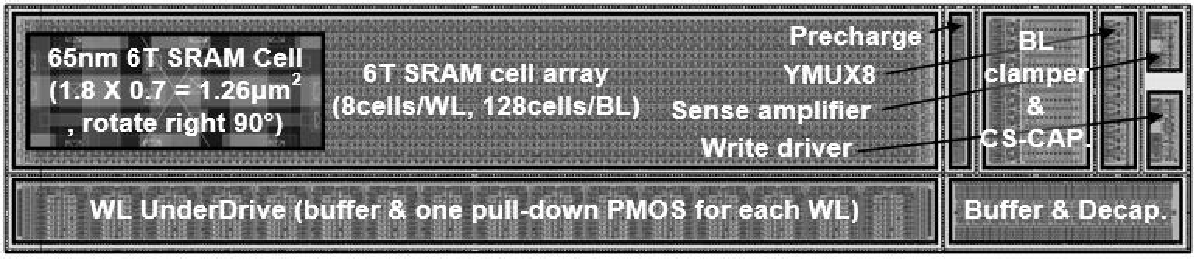

为了进行比较,如图13所示,表III中列出的辅助组合也采用65纳米CMOS技术进行了布局设计。图14显示了不同SRAM辅助配置下的功耗和面积比较结果。基于第二节和表III中介绍的ISO‐VMIN 辅助配置,设计了专用的 SRAM辅助电路(表I),以确定各种SRAM辅助技术的硬件成本。为了比较辅助电路的功耗,对辅助电路中消耗的平均电流进行了仿真。

写/读操作的辅助功耗开销。(b) 各种辅助电路的面积开销。)

使用60 FO4。由于SBL技术在预充电阶段需要额外功耗来拉升降低的位线电压电平,因此相应的预充电功耗也包含在此比较中。对于图14(b)所示的各种辅助技术的面积,使用位单元阵列的总面积(128个单元/位线和8个单元/字线)来归一化各辅助电路的面积开销。考虑到多子阵列架构有利于在两个相邻子阵列之间分摊辅助电路中的电容器,图14(b)中还研究了排除一半电容器面积后的面积开销。

如图5(b)和图14(a)所示,由于TVC[4]电路中的静态偏置电流,选项1和选项4(见表III)的辅助配置表现出相对较大的写入辅助功耗。通过使用电荷共享TVC(CS‐TVC)电路[13](在选项1’和选项4’中使用[13]),可以缓解传统TVC电路[4]的功耗开销,但代价是写辅助电路的面积增加 ∼1.66倍,如图14(b)所示。与仅使用 WLUD的读辅助配置(选项1∼3)相比,WLUD和SBL的组合在读辅助电路中显示出 ∼1.36倍更高的功耗,因为 SBL技术需要较大的功耗开销以在预充电阶段将降低的位线电压电平拉高。

如表III和图15所示,尽管基于列的SBL方案由于降低位线电压电平的前置步骤导致性能损失,但由于字线上升持续时间缩短从而确保了ISO‐VMIN,该开销得以补偿。此处,由于MPFP仿真未考虑SBL持续时间,且图3(a)和 (b)中未明确显示TVC和NBL所需的辅助持续时间,因此额外进行了统计估计(基于1万次蒙特卡洛仿真的均值+ 3 sigma),以确定详细的单元访问时间。如图15所示,与仅采用WLUD的配置相比,WLUD和SBL的组合使访问时间减少了34.7%。此外,同时访问WLUD和NBL( $V_{DD}$的35%)比顺序访问WLUD和NBL( $V_{DD}$的25%)访问时间减少了8.2%,但代价是功耗增加了20.4%,面积增加了12.6%,如图14和图15所示。与TVC相比,基于NBL的辅助配置由于TVC与NBL之间写入能力的不同,单元访问时间减少了14.9%。

考虑到整体功耗和面积开销,所提出的SRAM辅助电路显示出最低的成本。与基于传统SBL和NBL的选项5相比,所提出的辅助电路可实现41%的功耗降低和2.3%的面积减小(使用分摊电容器)。由于所提出的位线钳位器可以采用比传统SBL方案更少的晶体管和更小的PMOS堆栈来设计,读辅助电路可实现[11], 2.1%的性能提升。得益于NBL中的电荷回收,写辅助电路相较于传统的NBL可实现42.9%的节能。与WLUD和CS‐TVC组合[13],相比,由于CS‐TVC仅通过电荷共享方式减少 $V_{CS}$,在选项1’ 中引入了相当大的面积开销。因此,与选项1’相比,所提出的辅助方法在面积增加23.4%的代价下,实现了2%的功耗降低和45.1%的单元访问时间减少。

五、结论

在本研究中,为了降低传统SRAM辅助技术的功耗,提出了一种新型电荷回收SRAM辅助电路。通过协同结合读取和写入辅助方案,传统SBL电路中的浪费电荷可以被高效回收,以生成作为NBL辅助技术使用的负电压。此外,还基于MPFP动态稳定性估计进行了全面分析,以在相同辅助能力(ISO‐VMIN条件)下比较各种SRAM辅助技术的硬件成本。基于65纳米CMOS技术的对比表明,得益于电荷回收的有效性,所提出的电荷回收SRAM辅助电路相较于传统的SBL与NBL组合方案,功耗降低了41%,面积缩减了2.3%。

3930

3930

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?