目录

1、总线的基本概念

总线(Bus) 是计算机系统中多个功能部件之间传递信息的公共通道,具有共享性(多设备共用)和分时性(同一时间仅允许一对设备通信)。

1.1、计算机系统互联方式

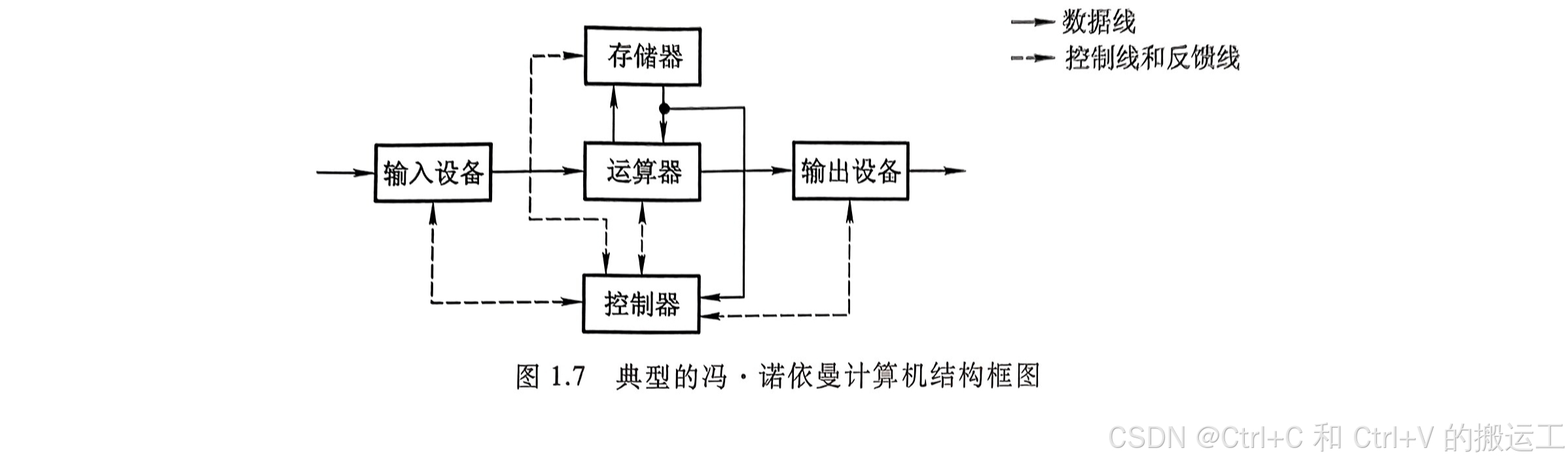

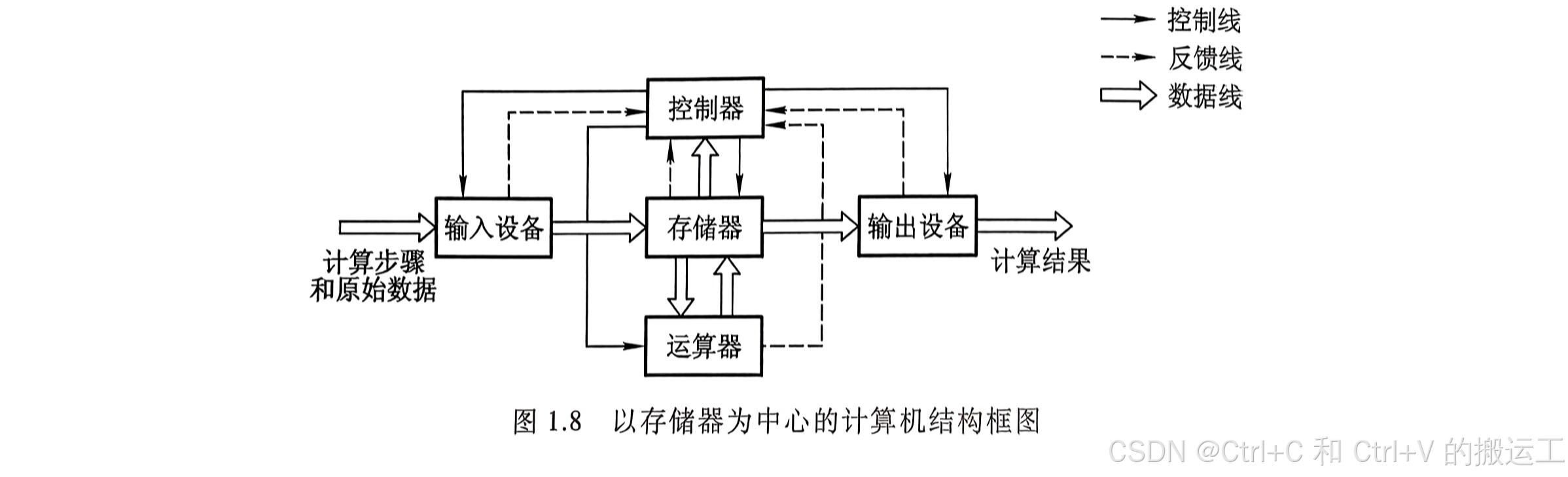

计算机五大部件(运算器、控制器、存储器、输入设备、输出设备)的互连方式分为两类:

1.1.1、分散连接

特点:各部件间通过单独连线直接通信。

缺点:

- 早期以运算器为中心:I/O设备与存储器交换数据需经过运算器,导致CPU效率低下。

改进以存储器为中心:引入中断和DMA技术,允许I/O设备直接与存储器交换数据,但仍无法解决I/O设备连接的灵活性问题(新增设备需改动硬件)。

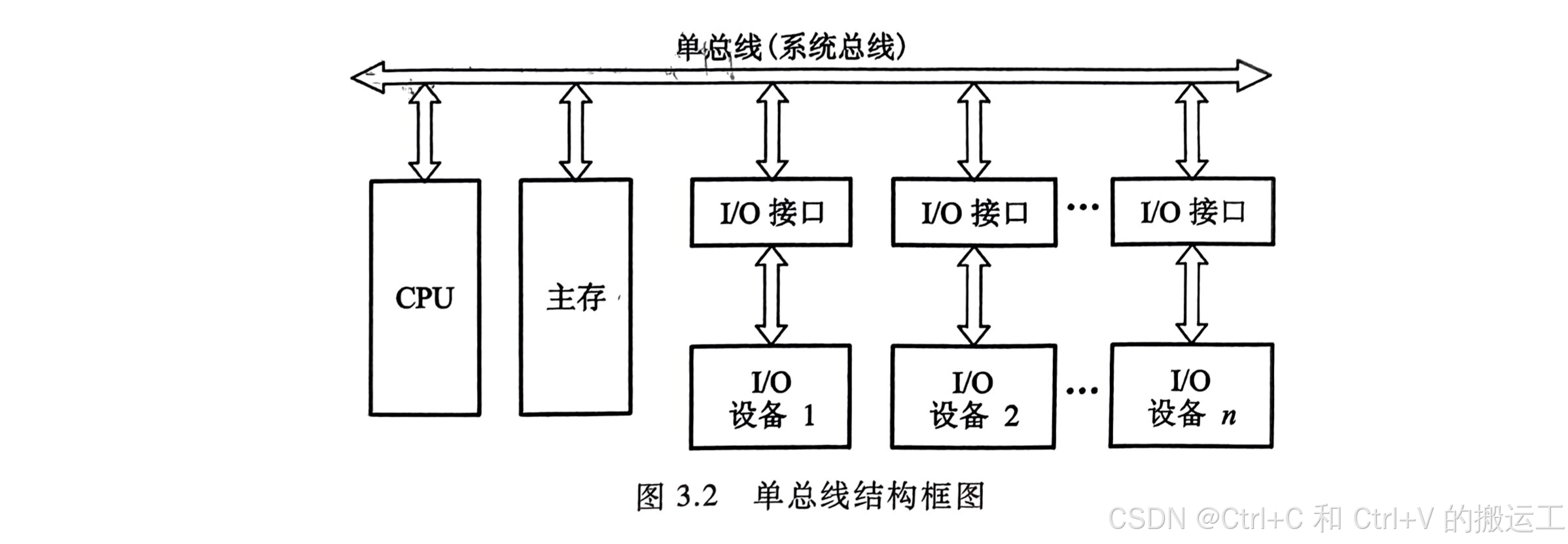

1.1.2、总线连接

定义:所有部件通过一组公共传输线(总线)连接。

核心特性:

- 共享性:多个设备共用同一总线。

- 分时性:某一时刻仅允许一个设备发送信息,但允许多个设备同时接收。

优势:

- 简化硬件设计,提高扩展性(新增设备仅需接入总线)。

- 降低连接复杂度,节省成本。

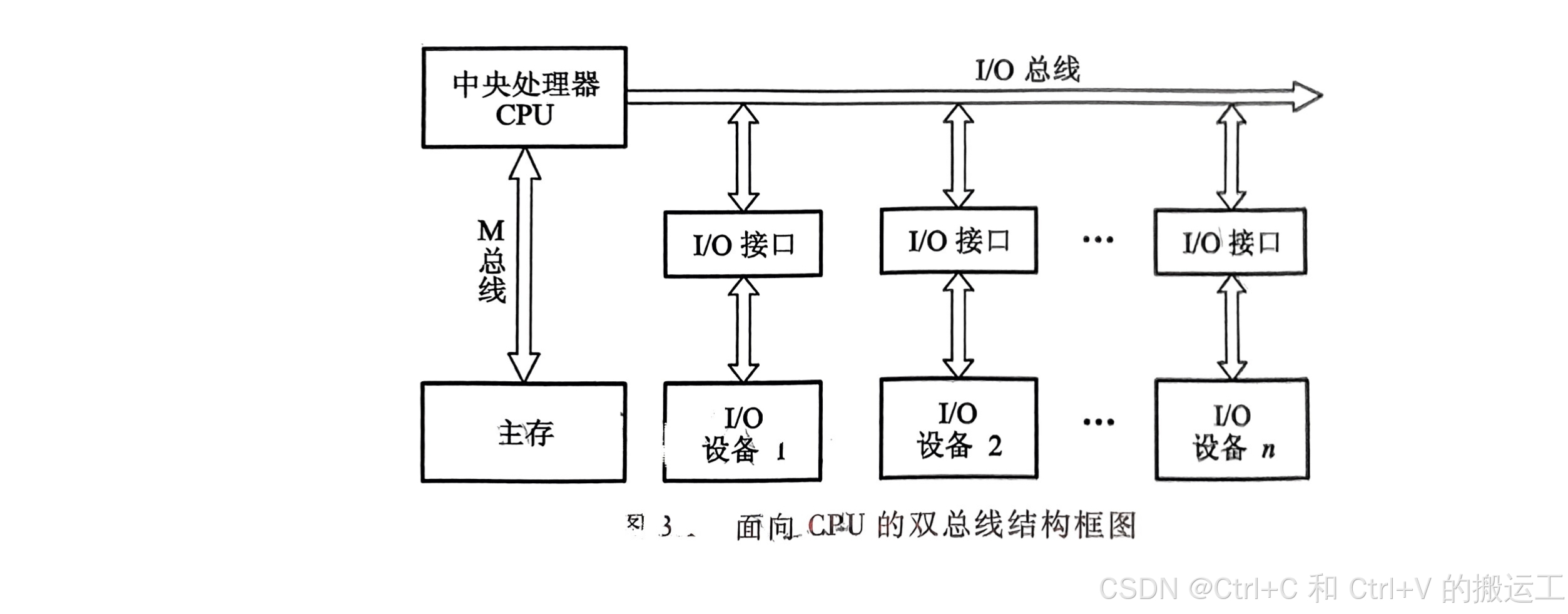

1.2、总线结构的演进

1.2.1、以CPU为中心的总线结构

设计:

- 存储总线(M总线):连接CPU与主存。

- I/O总线:连接CPU与I/O设备(通过接口)。

缺点:I/O设备与主存交换数据仍需占用CPU,效率受限。

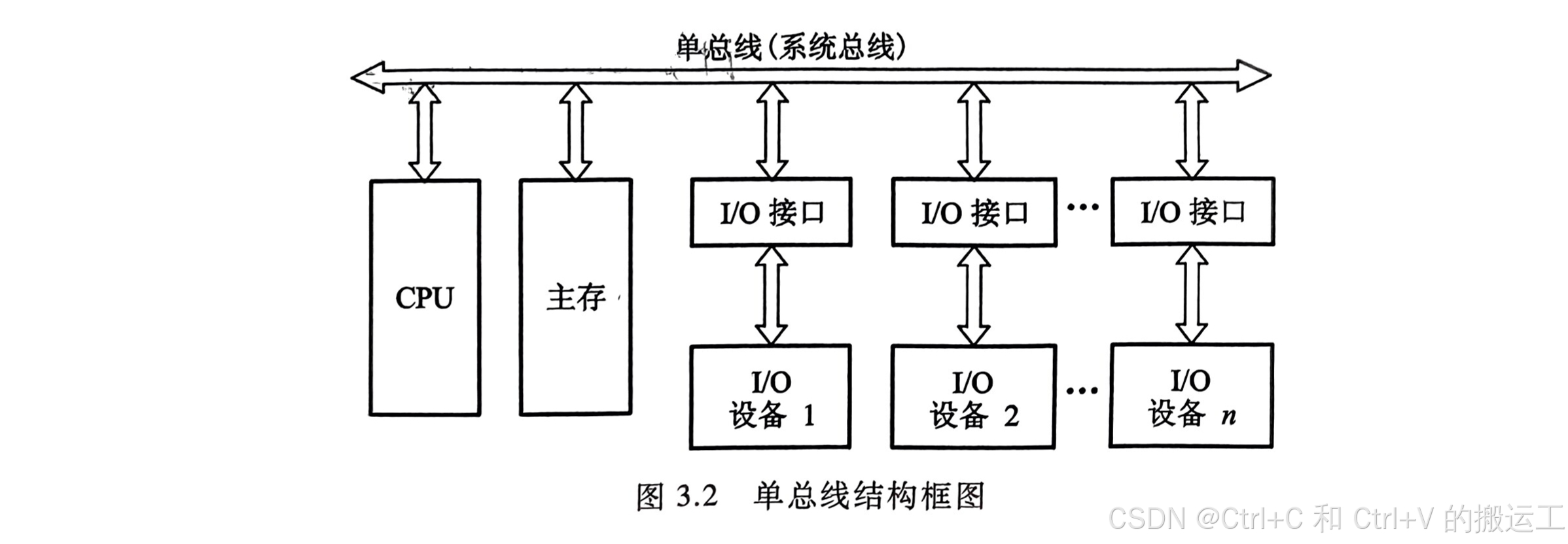

1.2.2、单总线结构

设计:所有部件(CPU、主存、I/O设备)共享一组总线。

优点:

- I/O设备与主存交换数据时,CPU可执行其他任务(通过总线判优控制)。

- 简化硬件设计(如PDP-11、DJS183机型)。

缺点:

- 总线冲突频繁,需仲裁逻辑(如优先级判定)。

- 带宽限制导致性能瓶颈。

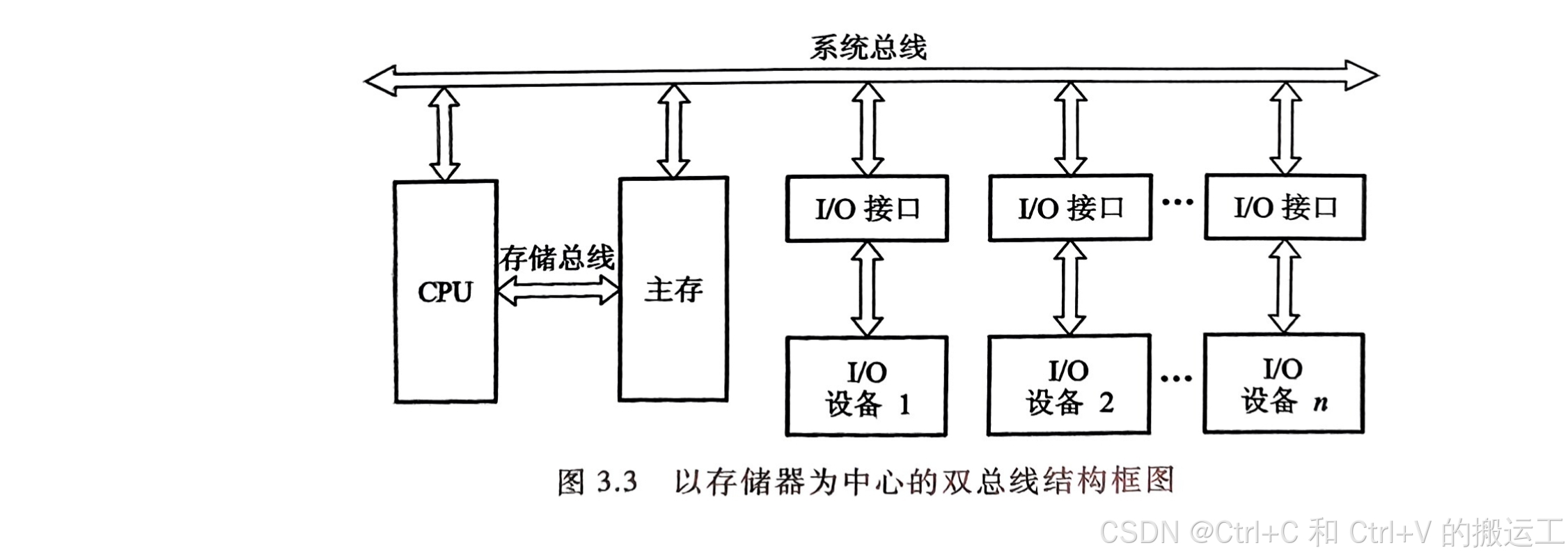

1.2.3、以存储器为中心的双总线结构

设计:

- 存储总线:专用高速通道连接CPU与主存。

- 系统总线:连接主存与I/O设备,保留I/O与主存直接通信的能力。

优势:

- 分离高速(CPU-主存)与低速(I/O)传输,减少总线竞争。

- 保留单总线结构的灵活性(如DJS184机型)。

现代应用:多级总线结构(如CPU局部总线 + PCIe总线 + SATA总线)。

2、总线的分类

2.1、 按数据传送方式

- 并行总线:多条线同时传输(如8位数据一次传完),速度快,适合短距离(如内存条)。

- 串行总线:单线逐位传输(如1字节分8次传),抗干扰强,适合远距离(如USB、网线)。

2.2、按连接部件

片内总线:芯片内部连接(如CPU内部寄存器与运算单元)。

系统总线:连接电脑主板上的核心部件(CPU、内存、硬盘),分三类:

- 数据总线:传输数据(双向),位数决定单次传输量(如64位)。

- 地址总线:指定数据位置(单向),位数决定内存大小(如32位支持4GB内存)。

- 控制总线:发送控制信号(如读/写命令、中断请求)。

2.3、通信总线

连接不同设备或系统(如电脑与打印机、手机与传感器),分两种:

- 串行通信(如USB、Wi-Fi)

- 并行通信(如老式打印机接口)。

3、总线控制

3.1、总线判优控制

多个主设备同时请求总线使用权时的仲裁机制。

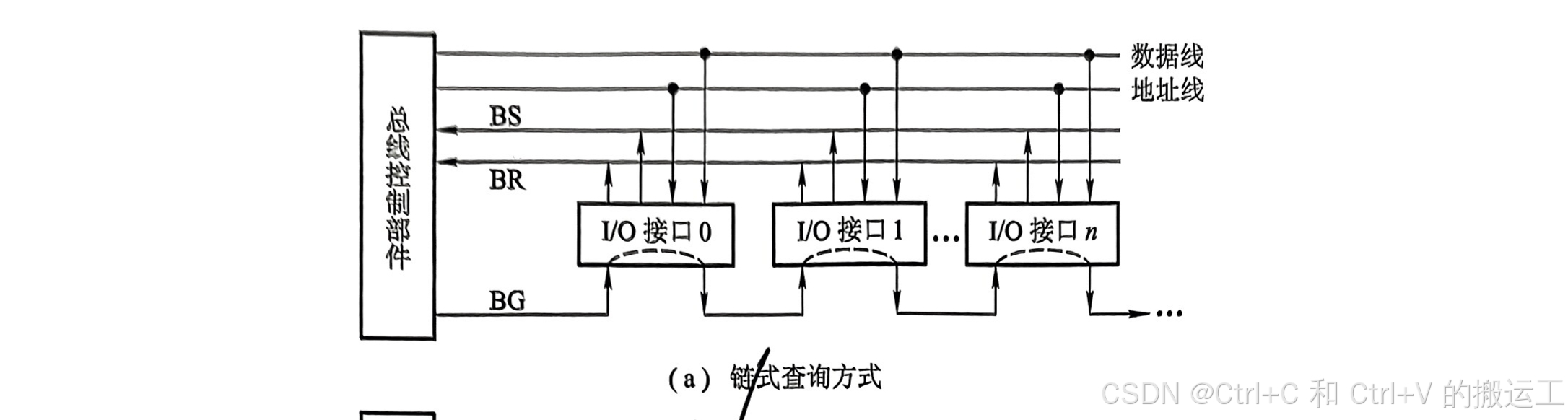

3.1.1、 链式查询

控制线:3根(BS、BR、BG)

- BS(Busy):总线忙状态信号(高电平表示总线被占用)。

- BR(Request):总线请求信号(设备拉高表示请求总线)。

- BG(Grant):总线授权信号(仲裁器发出,沿链式结构串行传递)。

工作流程:

设备需使用总线时,通过BR线向仲裁器发送请求。

仲裁器检测BS线:若总线空闲(BS=0),则通过BG线发送授权信号。

BG信号沿链式路径依次传递:

- 若某设备未请求总线,BG信号继续向下传递。

- 若某设备已请求总线,则截获BG信号,占用总线(拉高BS线),停止BG传递。

特点:

| 优点 | 缺点 |

|---|---|

| 仅需3根控制线,硬件简单 | 优先级固定(距离仲裁器越近的设备优先级越高) |

| 易于扩展设备 | 对电路故障敏感(链路中断导致后续设备无法使用总线) |

| 低延迟(无需地址译码) | 低优先级设备可能长期无法获得总线(“饿死”) |

适用场景:小型嵌入式系统(如单片机外设控制)。

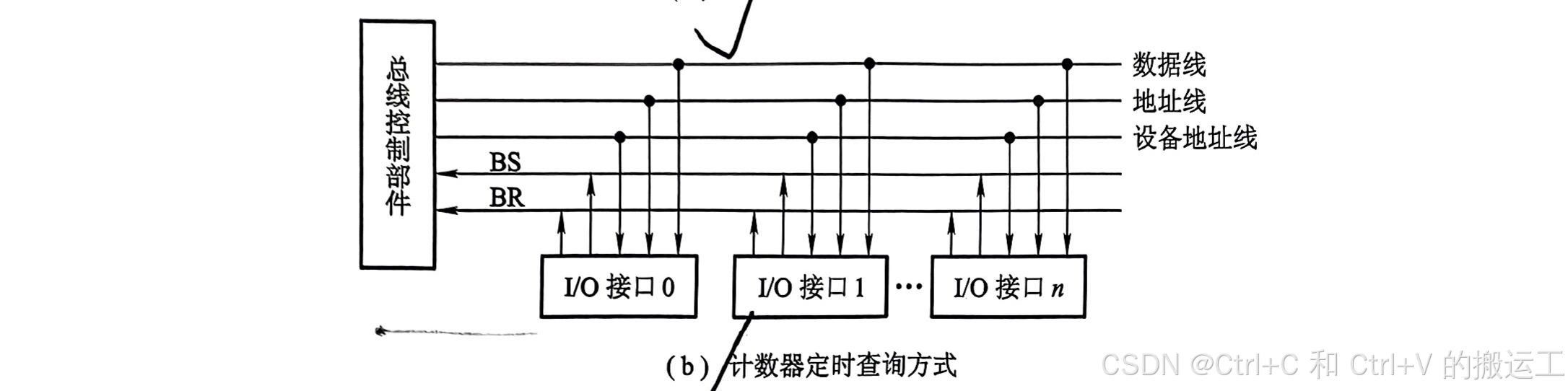

3.1.2、计数器定时查询

控制线:BR线(总线请求)、BS线(总线忙)、设备地址线(代替BG线,数量为log2Nlog2N,N为最大设备数)。

工作流程:

设备通过BR线发送请求,仲裁器检测到请求后:

- 若总线空闲(BS=0),启动计数器生成设备地址。

仲裁器通过设备地址线广播当前计数值:

- 若地址匹配的设备已请求总线,则授权其使用总线(拉高BS线),停止计数。

- 若无匹配请求,计数器递增(或按循环方式重置),继续查询。

优先级策略:

- 固定模式:计数器从0开始,设备地址固定(类似链式查询)。

- 循环模式:计数器从上一次终点开始,设备优先级动态轮转。

特点:

| 优点 | 缺点 |

|---|---|

| 优先级可动态调整(循环模式) | 需额外地址线(硬件复杂度增加) |

| 对链路故障容忍度较高 | 响应速度较慢(需逐设备查询) |

| 避免低优先级设备“饿死” | 控制逻辑复杂(需计数器与地址匹配电路) |

适用场景:中等规模实时系统(如工控设备的多传感器数据采集)。

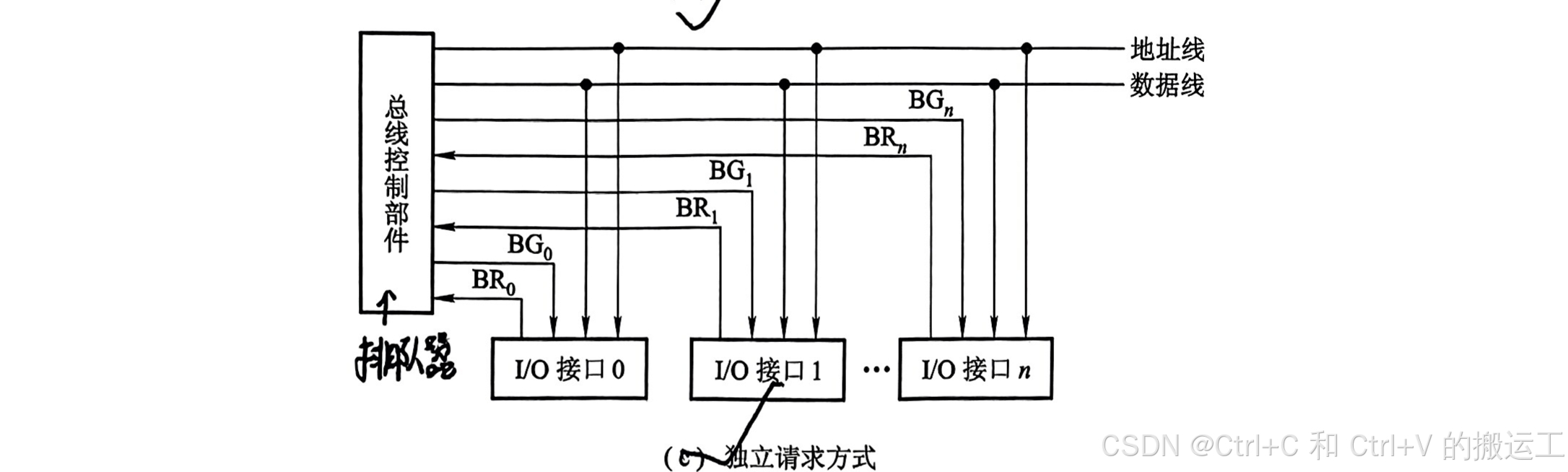

3.1.3、独立请求

控制线:每个设备独占一对请求线与授权线(共2N2N根,N为设备数)。

- BR(设备i的总线请求线)。

- BG(设备i的总线授权线)。

工作流程:

- 设备直接通过BR线向仲裁器发送请求。

- 仲裁器根据优先级策略(如固定优先级、自适应算法)对请求排序。

- 仲裁器通过BG线向最高优先级设备发送授权信号,该设备占用总线(拉高BS线)。

优先级策略示例:

- 固定优先级:预先为设备分配唯一优先级(如CPU > DMA > GPU)。

- 动态优先级:根据设备等待时间或任务紧急程度实时调整。

特点:

| 优点 | 缺点 |

|---|---|

| 响应速度最快(并行处理请求) | 控制线数量多(2N2N根) |

| 优先级控制高度灵活(可编程) | 仲裁器逻辑复杂(需排队电路或优先级编码器) |

| 无链路依赖,可靠性高 | 扩展性受限(新增设备需增加控制线) |

适用场景:高性能多核处理器、服务器(需快速响应高并发请求)。

3.1.4、三种判优控制的对比

| 判优方式 | 控制线数 | 优先级策略 | 响应速度 | 扩展性 | 典型应用 |

|---|---|---|---|---|---|

| 链式查询 | 3根 | 固定(物理位置) | 快 | 易 | 单片机、简单外设 |

| 计数器查询 | 可固定或循环 | 中等 | 中等 | 工控系统 | |

| 独立请求 | 2N根 | 灵活(可编程) | 最快 | 难 | 多核CPU、服务器 |

3.2、总线通信控制

总线通信控制的核心任务是协调多个部件对总线的使用权分配,确保数据传输的可靠性和效率。其流程分为四个阶段,并通过不同通信方式适应各类场景需求。

3.2.1、总线通信的四个阶段

想象快递员送包裹的过程:

- 申请分配阶段:快递员(主设备)向调度中心申请派送权限(总线使用权)。

- 寻址阶段:快递员确认收件人地址(从设备地址),并告知要寄送还是收取包裹(命令类型)。

- 传数阶段:快递员将包裹(数据)送到收件人手中,或从收件人处取回包裹。

- 结束阶段:快递员完成任务后,通知调度中心释放权限,其他快递员可继续使用道路(总线)。

3.2.2、四种总线通信方式.

1、同步通信

原理:所有设备严格遵循中央控制器(如CPU)发出的统一时钟信号,像做广播体操一样同步动作。

时钟信号:类似节拍器,每个动作(如发数据、收数据)必须在固定节拍内完成。

示例计算:

- 时钟频率100 MHz → 1秒内1亿次节拍,1节拍时间=1/100,000,000秒=0.01微秒。

- 每个传输周期4个节拍 → 总时间=0.01×4=0.04微秒。

- 32位数据=4字节 → 每秒传输量=4字节/0.04微秒=100MB/s。

| 优点 | 缺点 |

|---|---|

| 规则简单,设备配合容易 | 必须按最慢设备的节奏工作,效率低 |

| 适合短距离传输 | 灵活性差,设备速度差异大时容易“拖后腿” |

应用场景:单片机、内存与CPU之间(设备速度一致且距离近)。

2、异步通信

原理:主设备与从设备通过“请求-响应”信号(握手信号)协调,无需统一时钟,类似两人对话:

- 不互锁:A说完话不等B回应,直接走开(可能漏听回复)。

- 半互锁:A说完必须等B回应,但B回应后直接结束对话。

- 全互锁:A说完等B回应,B回应后等A确认,确保信息无误。

示例计算:

- 每帧数据=1起始位+7数据位+1校验位+1停止位=10位。

- 每秒传120帧 → 波特率=10位×120=1200 bps(每秒传输1200个二进制位)。

| 优点 | 缺点 |

|---|---|

| 设备速度可不同 | 控制信号增多,布线复杂 |

| 灵活性高 | 传输速度比同步通信慢 |

应用场景:U盘、打印机等外设(设备速度差异大)。

3、半同步通信

原理:在同步通信基础上增加“等待信号”(WAIT),允许慢设备申请延长操作时间。

工作流程:

- 主设备按统一时钟发指令。

- 从设备若未准备好,发WAIT信号暂停主设备,类似考试时举手请求延长时间。

| 优点 | 缺点 |

|---|---|

| 兼容不同速度设备 | 需额外控制线(WAIT信号) |

| 比纯同步更灵活 | 系统时钟不能太快 |

应用场景:工业传感器网络(设备速度差异中等)。

4、分离式通信

原理:将一次传输拆分为两个独立阶段,最大化利用总线空闲时间:

- 发指令阶段:主设备快速发送命令后立即释放总线。

- 回数据阶段:从设备准备好数据后,申请总线并返回结果。

| 优点 | 缺点 |

|---|---|

| 总线利用率极高 | 控制逻辑复杂 |

| 适合高负载场景 | 需要设备支持分段操作 |

应用场景:服务器、超级计算机(大量设备频繁请求总线)。

3.2.3、四种方式对比

| 通信方式 | 协调机制 | 速度 | 灵活性 | 适用场景 |

|---|---|---|---|---|

| 同步 | 统一时钟 | 快 | 低 | 设备速度一致 |

| 异步 | 握手信号 | 中等 | 高 | 设备速度差异大 |

| 半同步 | 时钟+等待信号 | 中等 | 中 | 中等速度差异 |

| 分离式 | 分段传输 | 最快 | 低 | 高负载复杂系统 |

3.2.4、如何选择通信方式?

- 设备速度一致 → 选同步通信(简单高效)。

- 设备速度差异大 → 选异步或半同步(平衡效率与兼容性)。

- 系统负载极高 → 选分离式通信(榨干总线性能)。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?