第二章 逻辑代数基础

2.1 逻辑代数的基本概念

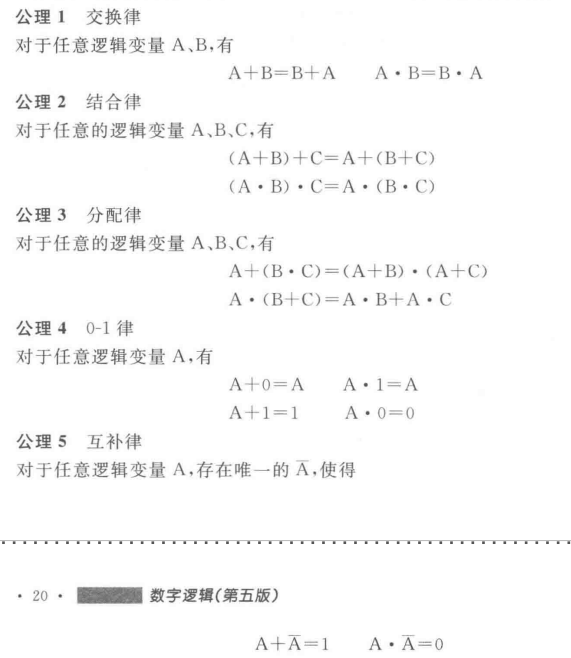

2.1.0 5个公理

2.1.1 逻辑变量及基本逻辑运算

逻辑代数中用字母表示变量,变量的取值有两种:0或1

3种基本运算:或与非

2.1.2 逻辑函数及逻辑函数间的相等(没啥用,空谈)

2.1.3 逻辑函数的表示方法

不唯一,常用的有三种:逻辑表达式、真值表、卡诺图

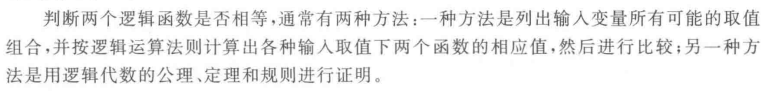

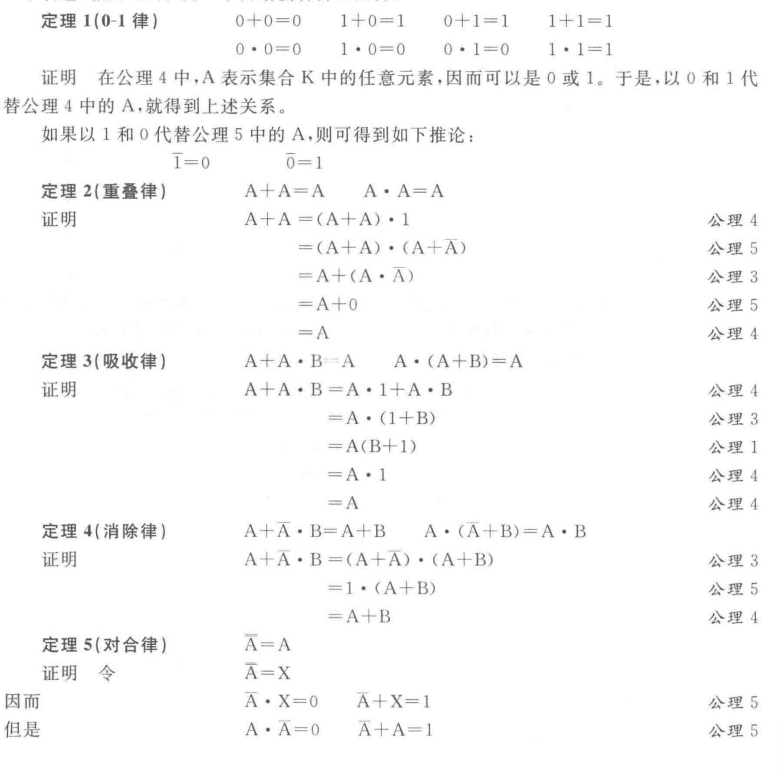

2.2逻辑代数的基本定理和规则

2.2.1基本定理

2.2.2 重要规则

逻辑代数有三种重要规则:代入规则、反演规则和对偶规则

2.2.3 复合逻辑

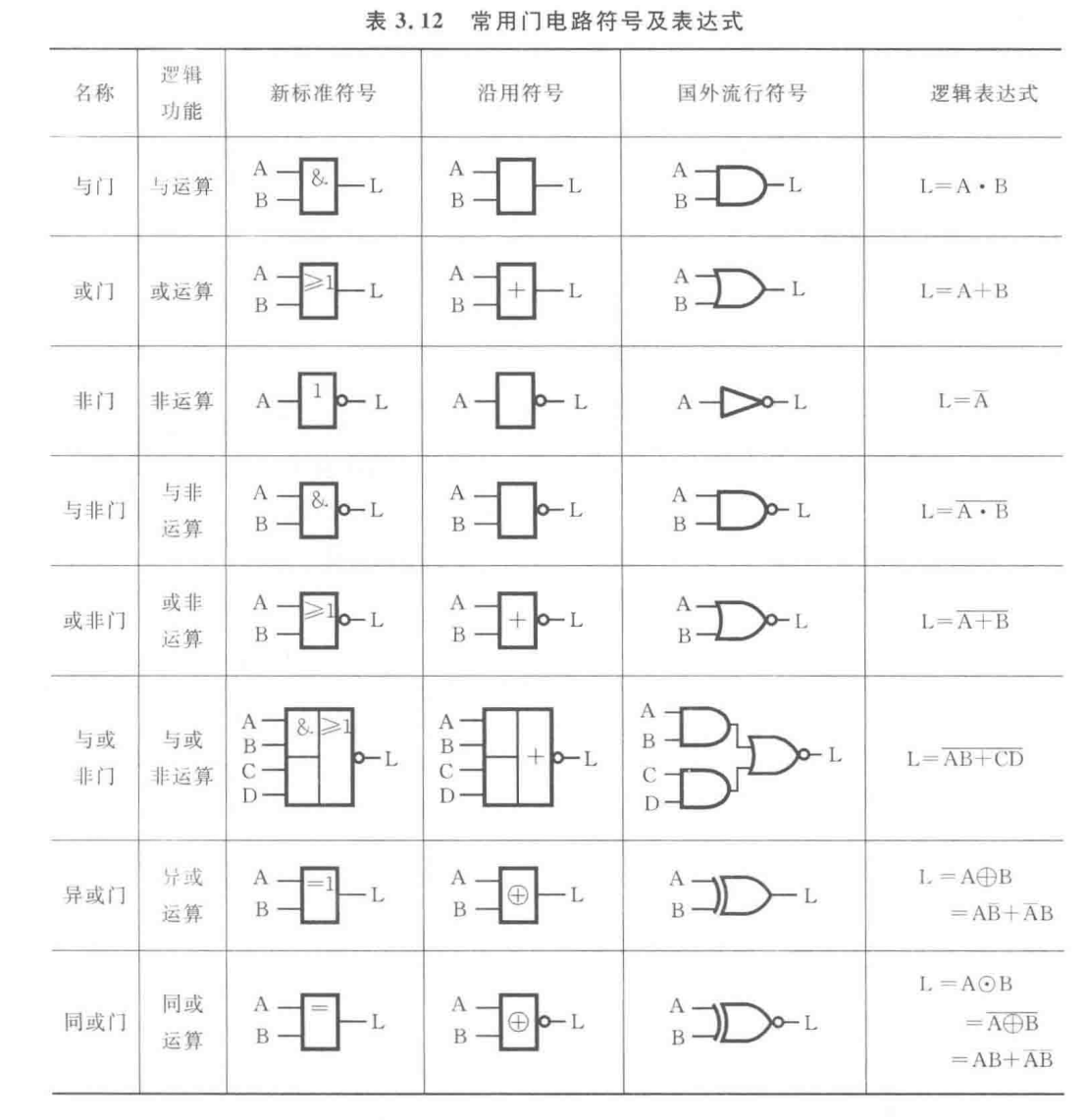

逻辑门:实现逻辑运算的逻辑电路称为逻辑门

基本逻辑门:与门、或门、非门

复合逻辑:与非、或非、与或非、异或、同或逻辑

2.3 逻辑表达式的形式与变换

2.3.1 逻辑函数表达式的基本形式

与-或表达式

或-与表达式

2.3.2 逻辑函数表达式的标准形式

2.3.3 逻辑函数表达式的转换

代数转换法,真值表转换法

2.4 逻辑函数的化简

代数化简法、卡诺图化简法和列表化简法

第三章 集成门电路与触发器

3.0 集成电路

集成电路(Integrated Circuit,IC):把实现各种逻辑功能的元器件及其连线都集中制造在同一块半导体材料基片上,并封装在一个壳体中,通过引线与外界联系,这就构成了所谓的集成电路,通常又称为集成电路芯片。

门电路:门电路是数字电路的基本组成单元,它通过对输入的电信号(通常用高电平、低电平表示 “1” 和 “0”)进行逻辑运算,输出特定的电信号。

tips:谈谈我对门电路的理解:就是深度学习中的黑匣子,加工厂

集成电路的分类(按功能):

-

模拟集成电路:处理连续变化的模拟信号(如声音、温度、电压等),常见类型包括:

- 运算放大器(用于信号放大、滤波);

- 电源管理芯片(如稳压器);

- 射频芯片(用于无线通信,如手机信号处理)。

-

数字集成电路:处理离散的数字信号(仅用 “0” 和 “1” 表示),是计算机、数字设备的核心。

-

混合集成电路:同时包含模拟和数字电路,用于需要跨域信号处理的场景(如模数转换器 ADC、数模转换器 DAC)。

3.1 数字集成电路的分类

1.按电路结构分

TTL集成门电路

CMOS集成门电路

2.根据设计方法和功能特点分

3.数字集成电路的分类(按复杂度):

-

小规模集成电路(SSI):

- 集成度低(10-100 个元件),主要实现基本逻辑门(如与非门、或非门)或简单组合电路(如触发器)。

-

中规模集成电路(MSI):

- 集成度中等(100-1000 个元件),可实现功能模块,如:

- 加法器、计数器、寄存器;

- 译码器、编码器(用于数据转换)。

- 集成度中等(100-1000 个元件),可实现功能模块,如:

-

大规模集成电路(LSI):

- 集成度较高(1000-10 万个元件),可实现完整的子系统,如早期的微处理器、存储器芯片(如 DRAM)。

-

超大规模集成电路(VLSI):

- 集成度超过 10 万个元件,典型代表包括:

- 微处理器(如 CPU、GPU);

- 复杂可编程逻辑器件(CPLD);

- 专用集成电路(ASIC,为特定场景定制)。

- 集成度超过 10 万个元件,典型代表包括:

-

特大规模集成电路(ULSI):

- 集成度超过 10 亿个元件,如现代智能手机芯片(SoC,系统级芯片),可集成 CPU、GPU、内存、通信模块等。

3.2 数字集成电路的典型应用:

- 计算机核心部件:CPU(运算与控制)、内存(DRAM、SRAM)、硬盘控制器;

- 数字设备:智能手机芯片、机顶盒、游戏机处理器;

- 逻辑控制:嵌入式芯片(如汽车电子中的 ECU、工业控制中的 PLC);

- 可编程器件:FPGA(现场可编程门阵列),可通过编程灵活定义电路功能,用于原型开发或定制化场景。

3.3 半导体器件的开关特性

和模电内容有重叠

导体

绝缘体

半导体

本征半导体:完全纯净的、结构完整的半导体晶体。

3.3.1 晶体二极管的开关特性

1.静态开关特性

2.动态开关特性

3.3.2 晶体三极管的开关特性

1.静态开关特性

2.动态开关特性

3.4 逻辑门电路

门电路是数字电路的基本组成单元,它通过对输入的电信号(通常用高电平、低电平表示 “1” 和 “0”)进行逻辑运算,输出特定的电信号。

3.4.1简单逻辑门电路

实现与、或、非3种基本逻辑运算的逻辑电路分别称为与门、或门和非门。他们是三种最基本的逻辑门。

与门

实现与逻辑功能的电路称为与门。与门有两个及以上的输入端和一个输出端。

或门

非门

3.4.2 TTL集成逻辑门电路

3.4.3 CMOS集成逻辑们电路

3.4.4 正逻辑和负逻辑

高电平和低电平:

高电平和低电平为某规定范围的电位值而非一固定值。

TTL电平:输出高电>2.4v;输出低电平<0.4v

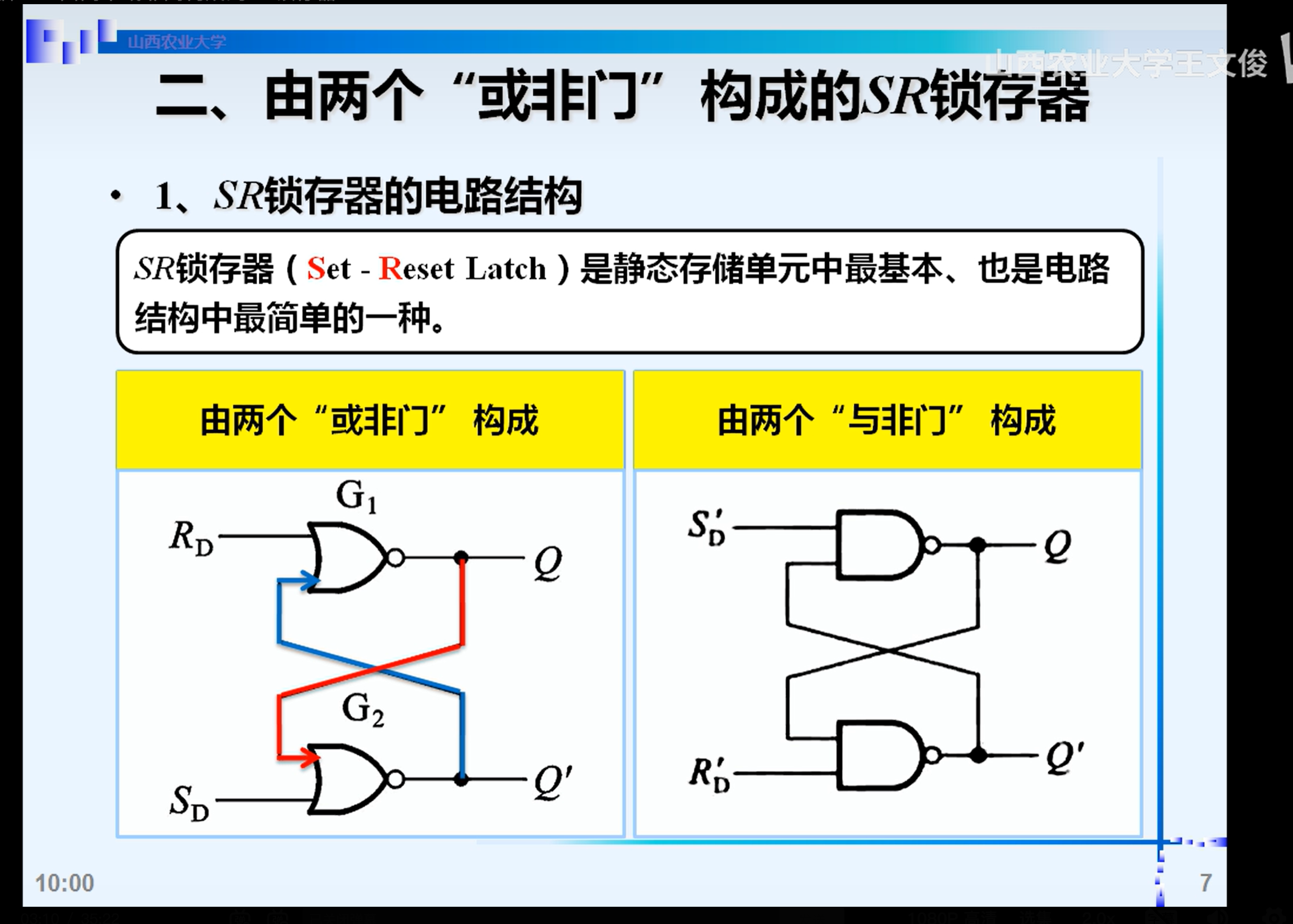

3.5 锁存器

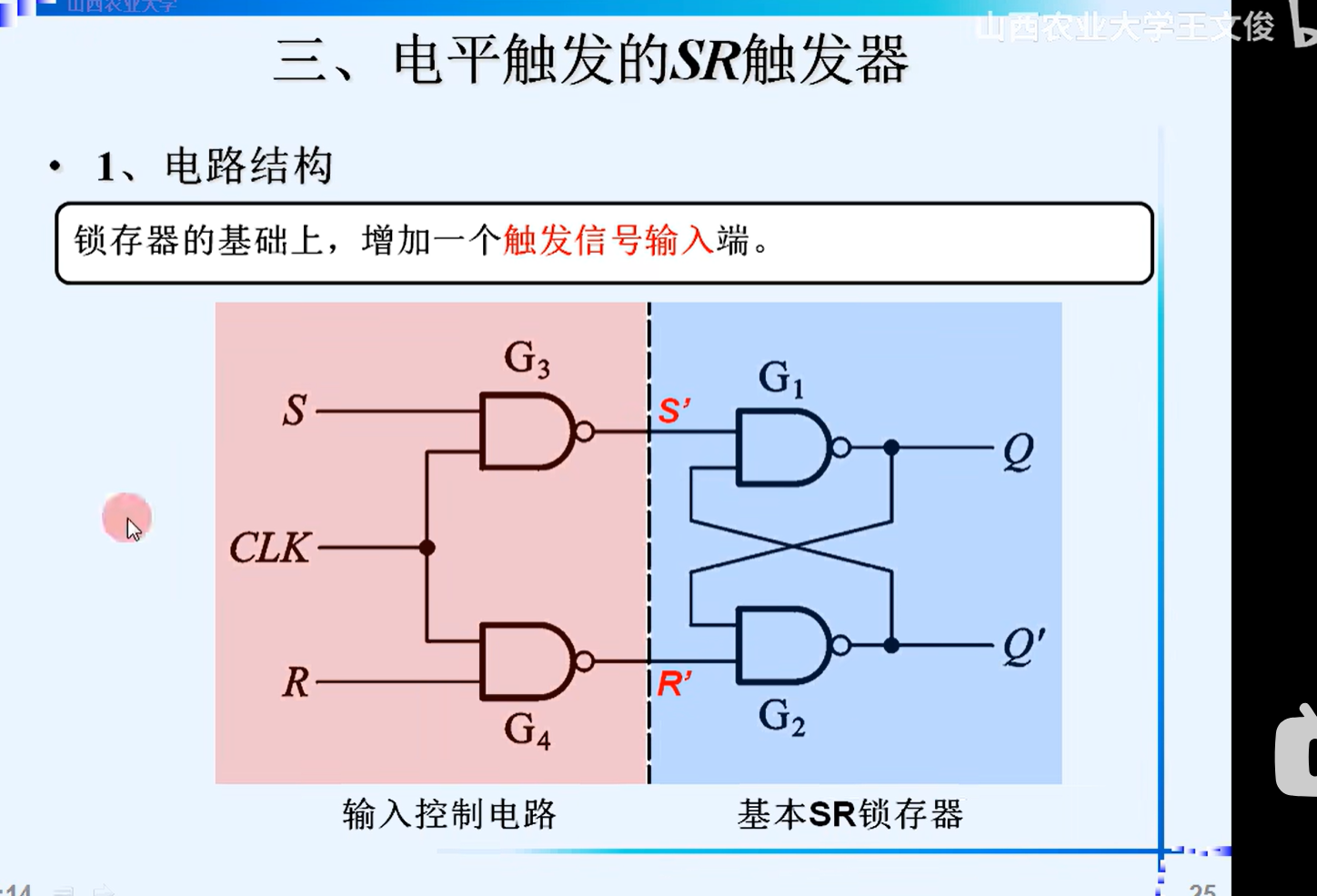

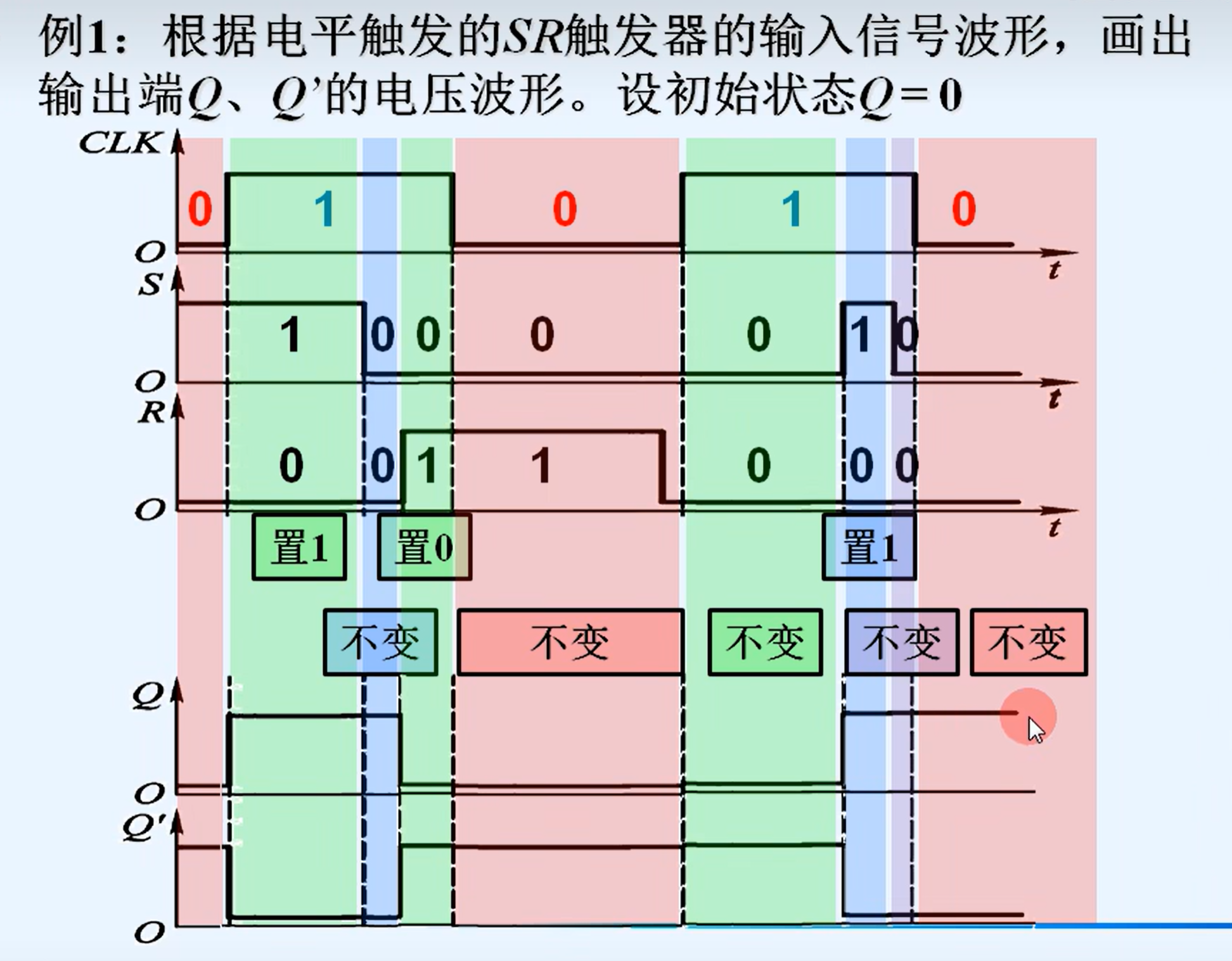

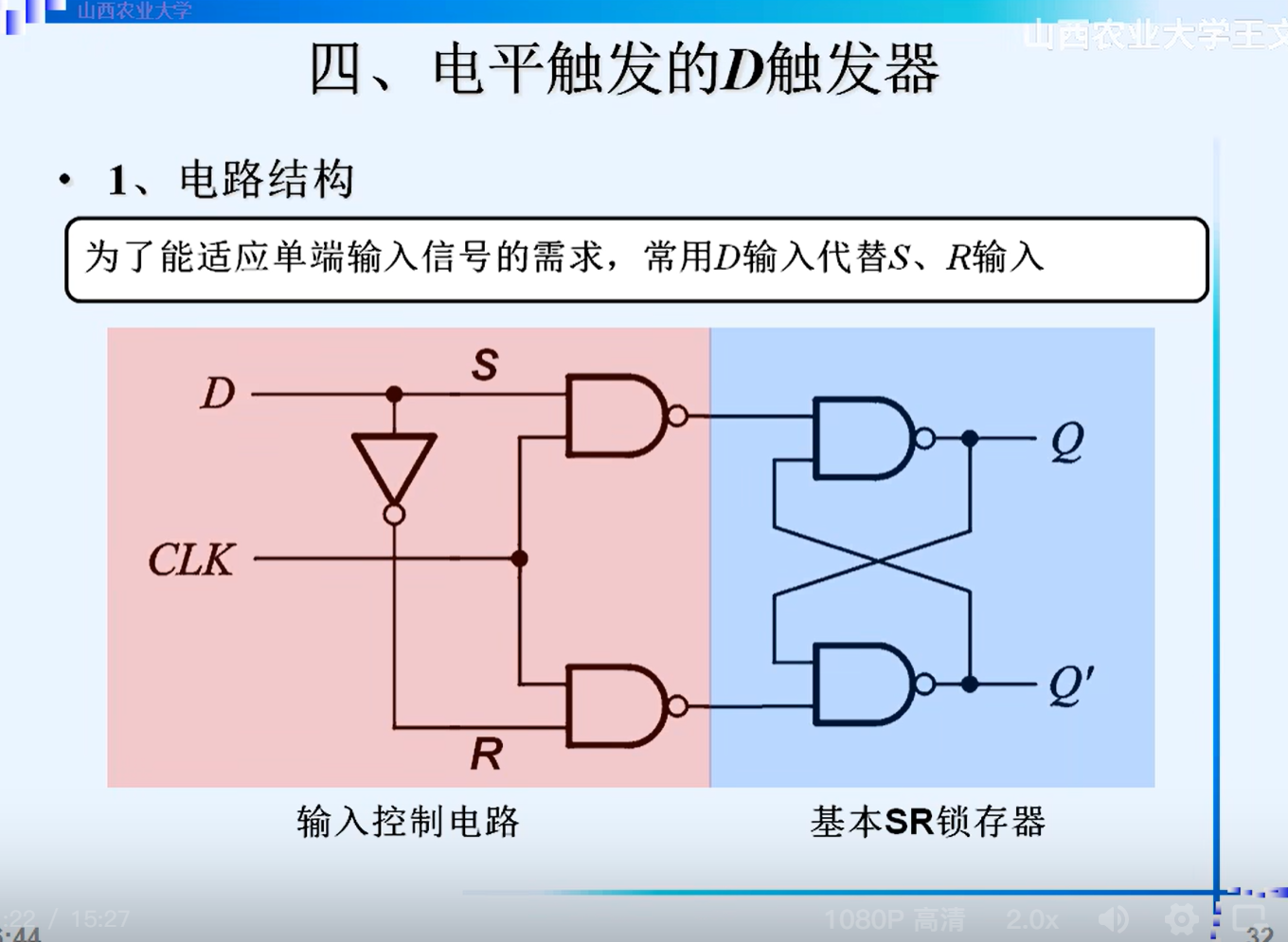

3.6 触发器

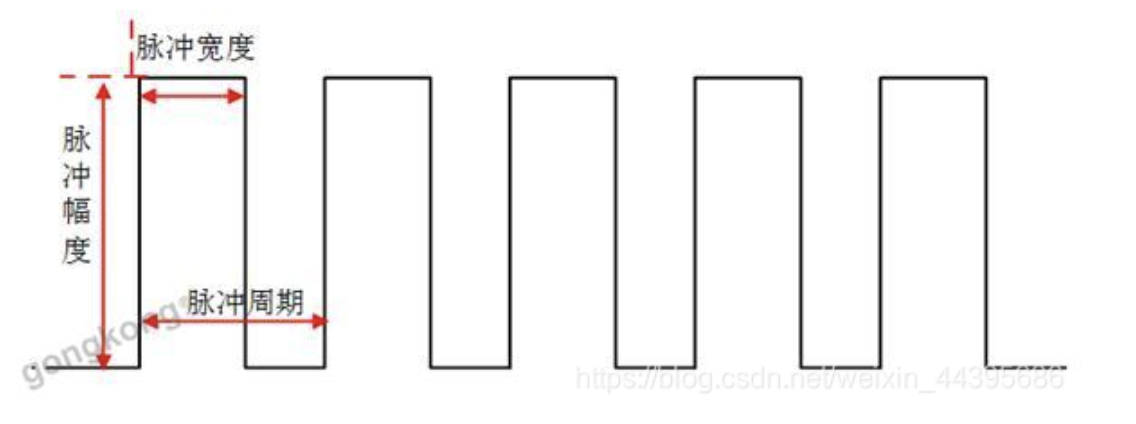

时钟信号(触发信号)CLK,Clock Sigal,是一种周期性的电信号,通常呈现为矩形波(方波),具有固定的频率和周期。它的高低电平交替变化,通过这种周期性的变化来控制数字电路中各个组件的动作时序。

脉冲(Pulse) 是指一种短暂出现、非周期性的信号变化,通常表现为在稳定状态(如零电平或恒定值)基础上,突然发生幅度变化并快速恢复的现象。它可以是电信号、光信号、机械振动等多种形式,特点:突发性、短暂性

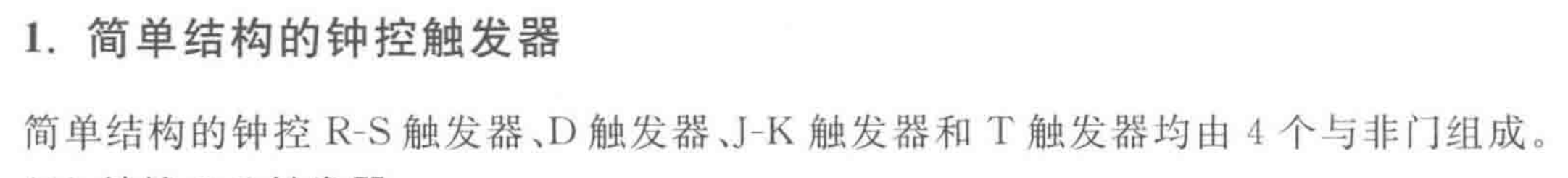

钟控触发器(时钟控制触发器,定时触发器)

CLK和CP

1. CLK(Clock)—— 时钟信号

定义:CLK 是 “时钟”(Clock)的缩写,指数字电路中用于同步各组件工作节奏的周期性电信号。它如同电路的 “心跳”,决定了电路中数据传输、运算、存储等操作的时间基准。

特点:

通常是周期性的矩形波(方波),包含高电平(逻辑 1)和低电平(逻辑 0),通过电平的交替变化触发电路动作。

频率(时钟频率)决定了电路的工作速度,频率越高,单位时间内可完成的操作越多(如 CPU 的主频就是一种 CLK 频率)。

应用场景:

广泛用于触发器、寄存器、计数器、微处理器(CPU)等数字电路,确保各部件按统一节奏协同工作,避免数据混乱。

例如,在同步时序电路中,所有触发器的状态更新都由 CLK 的特定边沿(上升沿或下降沿)触发。

2. CP(Clock Pulse)—— 时钟脉冲

定义:CP 是 “时钟脉冲”(Clock Pulse)的缩写,特指时钟信号中单个的脉冲信号,即 CLK 信号中的一个周期内的有效触发部分(通常是一个边沿或一个完整脉冲)。

特点:

强调时钟信号中的 “单个脉冲”,可理解为 CLK 信号的基本组成单元。

例如,方波时钟中,从低电平跳变到高电平的 “上升沿”、从高电平跳变到低电平的 “下降沿”,或一个完整的高低电平周期,都可称为一个 CP。

应用场景:

在描述触发器、计数器等器件的触发条件时常用,例如 “CP 上升沿触发” 表示器件在时钟脉冲的上升沿时刻执行状态更新。

有时也会将整个时钟信号简称为 CP(与 CLK 混用),但严格来说,CP 更侧重 “单个脉冲” 的概念。

对比维度 CLK(时钟信号) CP(时钟脉冲) 本质 周期性的连续信号(整体) 时钟信号中的单个脉冲或触发边沿(局部) 范围 包含多个连续的 CP 是 CLK 的基本组成单元 应用 描述电路的整体时钟源和频率 描述单个触发事件或脉冲触发条件

- 联系:CP 是 CLK 的组成部分,CLK 是多个 CP 的连续序列;两者均用于同步电路工作,在很多场景中可通用(如 “CP 频率” 即等同于 “CLK 频率”)。

- 区别:CLK 更强调 “连续的时钟信号”,CP 更强调 “单个脉冲或触发点”。

| 特性 | 锁存器 | 触发器 | 寄存器 | 存储器 | |

|---|---|---|---|---|---|

| 存储位数 | 1 位 | 1 位 | 多位(如 8/16/32 位) | 大量位(KB~TB 级) | |

| 触发方式 | 电平触发 | 时钟边沿触发 | 时钟边沿触发 | 地址和控制信号触发 | |

| 核心功能 | 锁存 1 位数据 | 同步存储 1 位数据 | 同步存储多位数据 | 大规模数据存储 | |

| 抗干扰性 | 差(易受毛刺影响) | 强(边沿触发) | 强(基于触发器) | 强(有校验机制) | |

| 典型应用 | 临时信号保持 | 时序电路基本单元 | CPU 内部高速存储 |

|

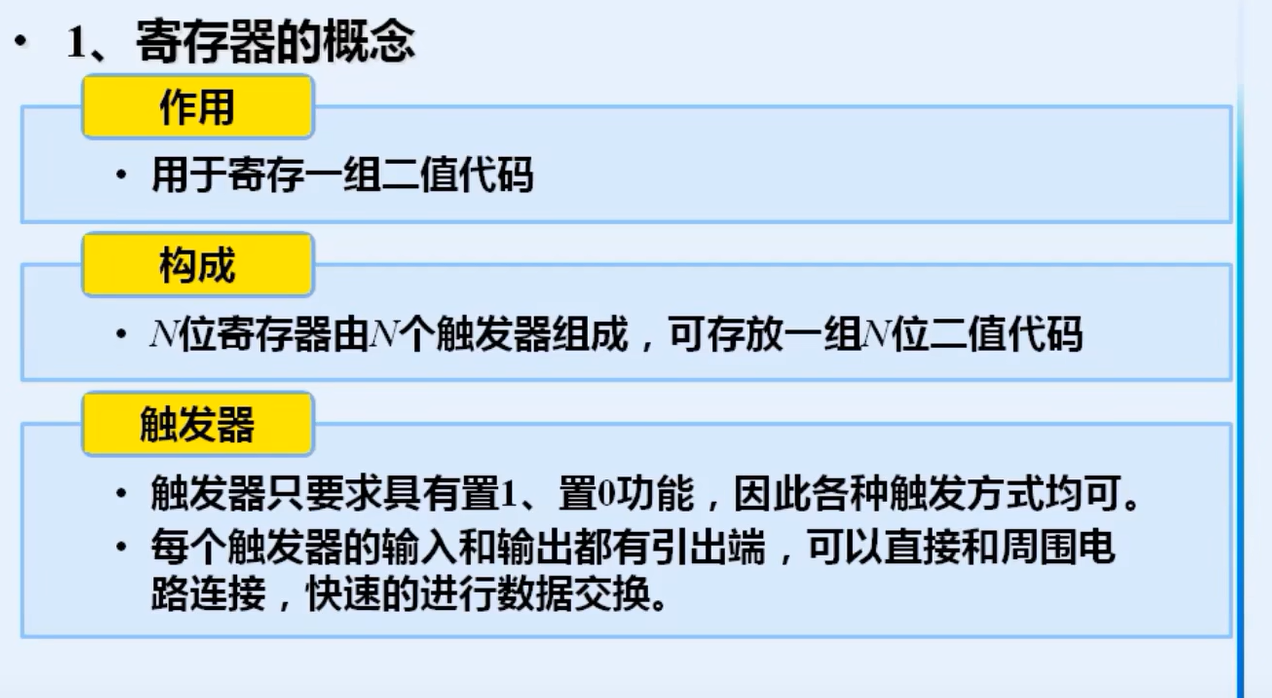

3.7 寄存器和存储器

第4章 组合逻辑电路

组合逻辑电路(Combinational Logic Circuit),输出仅由当前输入信号决定,与电路过去的状态无关,即电路中没有记忆功能,无需存储元。

典型的组合逻辑电路:加法器(半加器、全加器)、编码器、译码器、数据选择器(MUX)、比较器等。

组合逻辑电路应用场景:算术运算、数字信号的编码/译码、控制逻辑、计算机中的总线数据传输等。

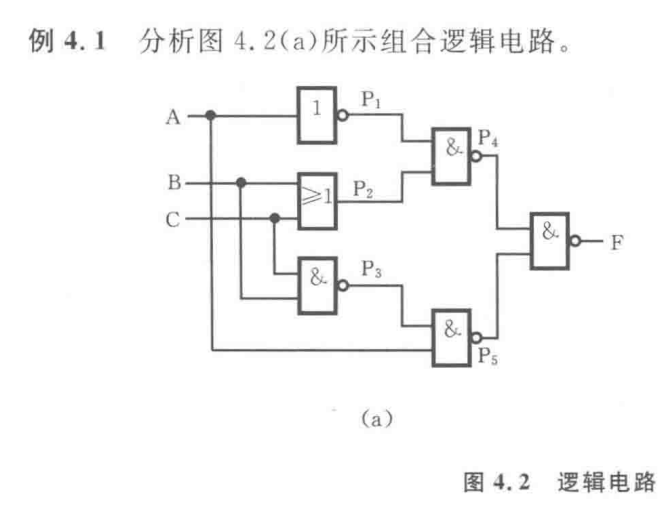

4.1 组合逻辑电路分析

- 根据逻辑电路图写出输出函数表达式

- 化简输出函数表达式

- 列出输出函数真值表

- 功能评述

4.2 组合逻辑电路设计

4.3 组合逻辑电路的险象

第5章 同步时序逻辑电路

数字电子技术基础 6.2 时序逻辑电路的分析(1)_哔哩哔哩_bilibili![]() https://www.bilibili.com/video/BV1PR4y1W7Sy?spm_id_from=333.788.videopod.sections&vd_source=cdc2a34485eb016f95eae1a314b1a620数字电子技术基础 6.3 时序逻辑电路的分析(2)_哔哩哔哩_bilibili

https://www.bilibili.com/video/BV1PR4y1W7Sy?spm_id_from=333.788.videopod.sections&vd_source=cdc2a34485eb016f95eae1a314b1a620数字电子技术基础 6.3 时序逻辑电路的分析(2)_哔哩哔哩_bilibili![]() https://www.bilibili.com/video/BV1kF411z72v?spm_id_from=333.788.videopod.sections&vd_source=cdc2a34485eb016f95eae1a314b1a620

https://www.bilibili.com/video/BV1kF411z72v?spm_id_from=333.788.videopod.sections&vd_source=cdc2a34485eb016f95eae1a314b1a620

5.1 时序逻辑电路概述

时序逻辑电路:时序逻辑电路的输出不仅取决于当前的输入信号,还与电路过去的状态有关,这是因为电路中包含存储元件(如触发器、寄存器等),能够保存历史信息。

时序逻辑电路的基本构成:由组合逻辑电路和存储电路(最常用的存储元件是触发器)。

5.1.1时序逻辑电路的分类

1. 按照电路的工作方式,时序逻辑电路可分为两大类:

| 类别 | 特点 | 优势 | 劣势 | 应用示例 |

|---|---|---|---|---|

| 同步时序逻辑电路 | 所有存储元件(触发器)的状态更新受同一时钟信号控制,仅在时钟特定边沿或电平有效时改变状态 | 抗干扰能力强,电路工作稳定,设计和分析相对简单 | - | 计数器、寄存器、移位寄存器等 |

| 异步时序逻辑电路 | 存储元件的状态更新不受统一时钟信号控制,状态改变可能由输入信号直接触发或其他触发器输出间接触发 | 速度快(无需等待时钟信号),电路结构可能更简单 | 容易产生竞争冒险现象,设计和分析较复杂 | 异步计数器、某些控制电路等 |

2.按照电路的输出/输入关系分类

Mealy和Moore(米勒型和摩尔型)

3.按照输入信号的形式进行分类

脉冲型和电平型

5.1.2

第6章 异步时序逻辑电路

杂

时钟

在数字电路,尤其是时序逻辑电路中,时钟(Clock) 是一个至关重要的控制信号,它像 “时间基准” 一样协调电路中各部分的工作节奏,确保电路按预期时序稳定运行。以下从多个角度详细解析时钟信号:

一、时钟信号的基本特性

时钟信号通常是周期性的脉冲信号,其典型波形为矩形波,包含以下关键参数:

- 周期(T):时钟信号完成一次完整周期(从一个脉冲的起始到下一个同相位脉冲的起始)所需的时间,单位为秒(s)、纳秒(ns)等。

- 频率(f):单位时间内时钟脉冲的个数,与周期成反比(\(f = 1/T\)),单位为赫兹(Hz)、兆赫兹(MHz)、吉赫兹(GHz)等,是衡量电路工作速度的重要指标(如 CPU 的 “主频” 即核心时钟频率)。

- 占空比(Duty Cycle):时钟信号中高电平持续时间与周期的比值(通常以百分比表示),理想情况下多为 50%(高、低电平持续时间相等),但也可根据需求设计为非对称(如 20%、80%)。

- 边沿(Edge):时钟信号从低电平跳变到高电平的 “上升沿”(Rising Edge)和从高电平跳变到低电平的 “下降沿”(Falling Edge),这两个瞬间是时序电路状态更新的关键触发点。

二、时钟在时序电路中的作用

同步控制状态更新 在同步时序逻辑电路中,所有触发器的状态更新都严格受时钟信号控制。只有当时钟信号到达特定边沿(如上升沿)或处于特定电平(如高电平)时,触发器才会根据输入信号更新状态;其他时间内,即使输入信号变化,触发器状态也保持不变。 例如:D 触发器通常在时钟上升沿时,将输入的 D 信号 “锁存” 到输出端 Q,实现状态更新。

协调电路时序 复杂数字系统(如 CPU、存储器)包含大量逻辑单元,时钟信号确保各单元按统一节奏工作,避免因信号传输延迟导致的逻辑混乱。例如,在数据传输中,时钟可用于 “同步采样”—— 接收端在时钟边沿时刻读取输入数据,确保数据稳定有效。

区分信号先后顺序 时钟的周期性使得电路能通过 “计数时钟脉冲” 记录时间或事件顺序,例如计数器通过累加时钟脉冲个数实现计数功能,定时器通过设定时钟周期数控制延时时间。

三、时钟信号的类型与应用场景

根据电路需求,时钟信号可分为不同类型,适配不同场景:

- 单一时钟:整个电路使用同一时钟信号,适用于结构简单、对同步要求高的电路(如小型计数器、寄存器)。

- 多相时钟:由多个相位不同的时钟信号组成(如两相时钟:φ1 和 φ2,相位相差 180°),常用于需要分时操作的电路(如某些存储器的读写控制,避免读写冲突)。

- 可变频率时钟:频率可动态调整(如 CPU 的 “变频技术”),在高性能需求时提高频率,低功耗需求时降低频率,兼顾速度与能耗。

四、时钟相关的关键问题

时钟 skew(时钟偏移) 由于时钟信号在电路中传输路径长度、负载不同,同一时钟信号到达不同触发器的时间存在差异,称为 “时钟偏移”。严重的偏移可能导致触发器状态更新不同步,引发逻辑错误,因此电路设计中需通过布线优化(如等长布线)减少偏移。

时钟 jitter(时钟抖动) 时钟信号的实际边沿位置相对于理想位置的随机偏差,通常由噪声、电源波动等引起。抖动过大会影响电路的时序裕量,导致采样错误,尤其在高频电路中需严格控制(如高速通信芯片)。

时钟树(Clock Tree) 在大规模集成电路(如芯片)中,为确保时钟信号均匀分配到所有触发器,会设计 “时钟树” 结构 —— 以时钟源为根,通过多级缓冲器(Buffer)形成对称分支,使时钟延迟和偏移最小化。

五、总结

时钟是数字时序电路的 “心脏”,其稳定性、频率和边沿特性直接决定了电路的性能和可靠性。无论是简单的计数器还是复杂的 CPU,都依赖时钟信号实现同步工作,而时钟偏移、抖动等问题的处理则是高性能数字电路设计的核心挑战之一。

5155

5155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?