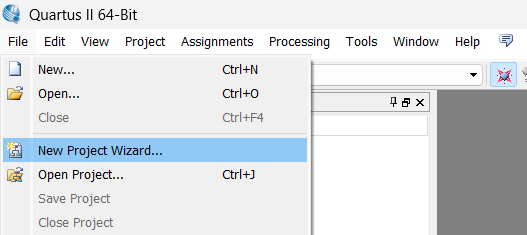

1.我们首先要创建一个新的工程。点击File,选择New Project Wizard。

在这里多说一句,如果遇到报错,请看20。

2.点击Next。

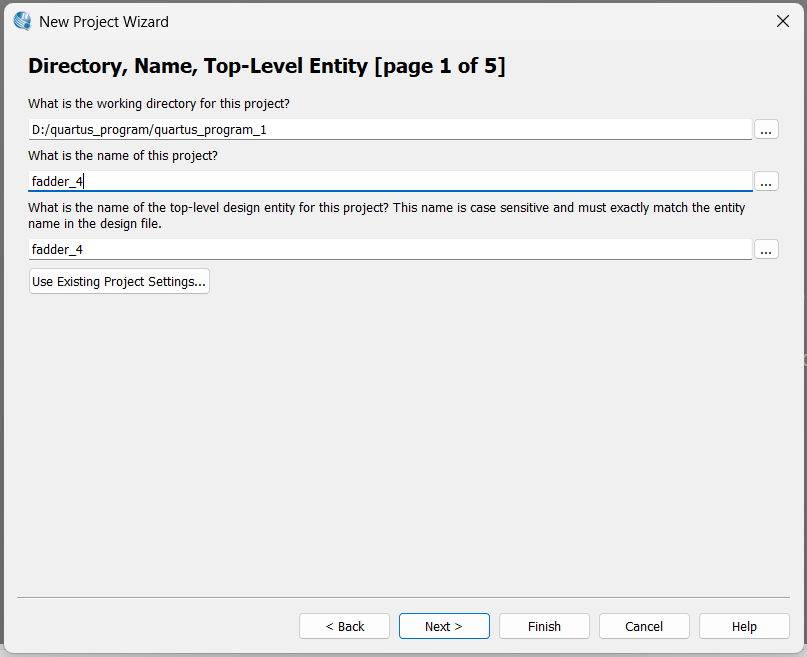

3.下图中,第一个白框为我们要创建的工程路径,第二个白框为工程名称,第三个白框为顶层设计名称。工程名称要与顶层设计名称相同,并且要与代码的模块名称相同,代码我会在下面给出。填写完之后点击Next。

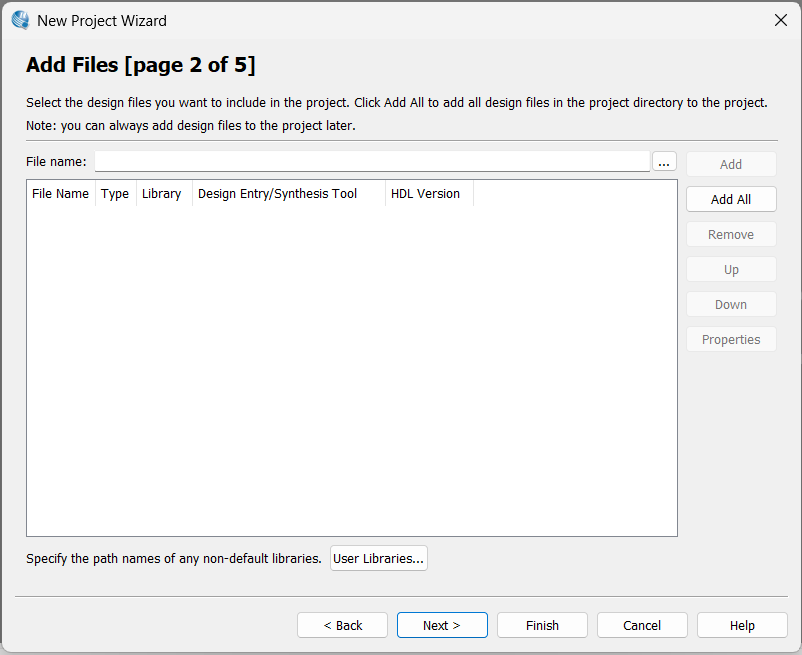

4.这里是问我们需不需要添加已经有的设计文件,在这里不用添加,直接点击Next即可。

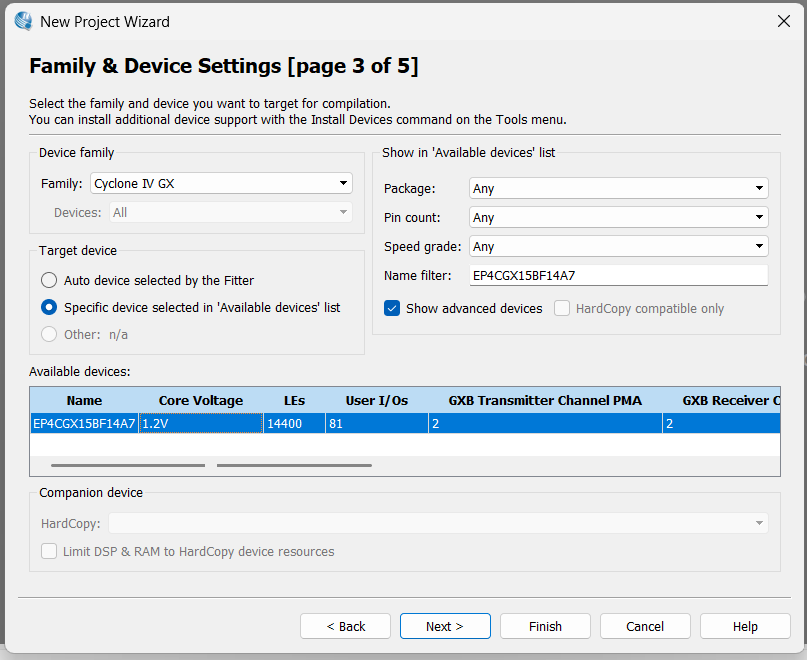

5.下图是选择板子,这里随便选择一个,点击Next就行了。

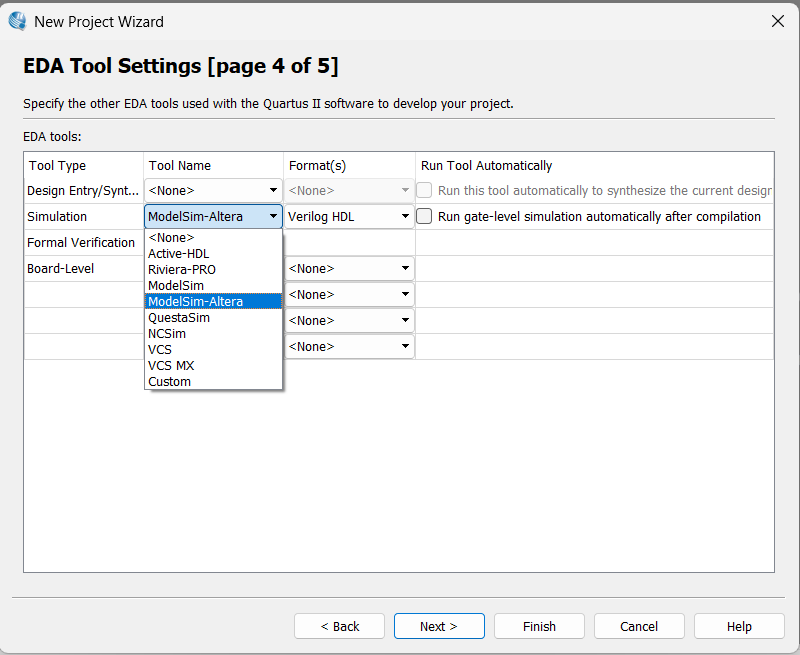

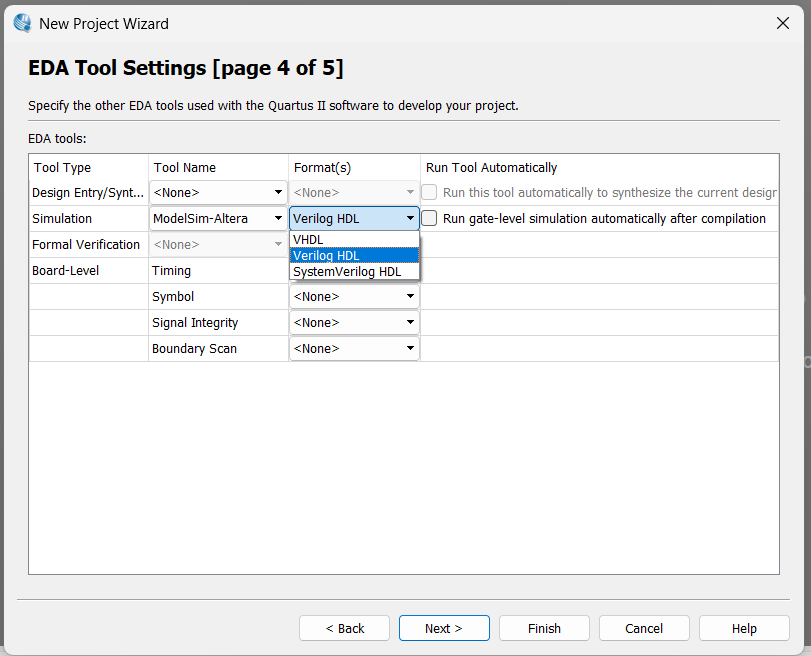

6.这一步请看下面的两张图片,在Simulation这一行,选择ModelSim-Altera,Verilog HDL,其余的不要动,点击Next。

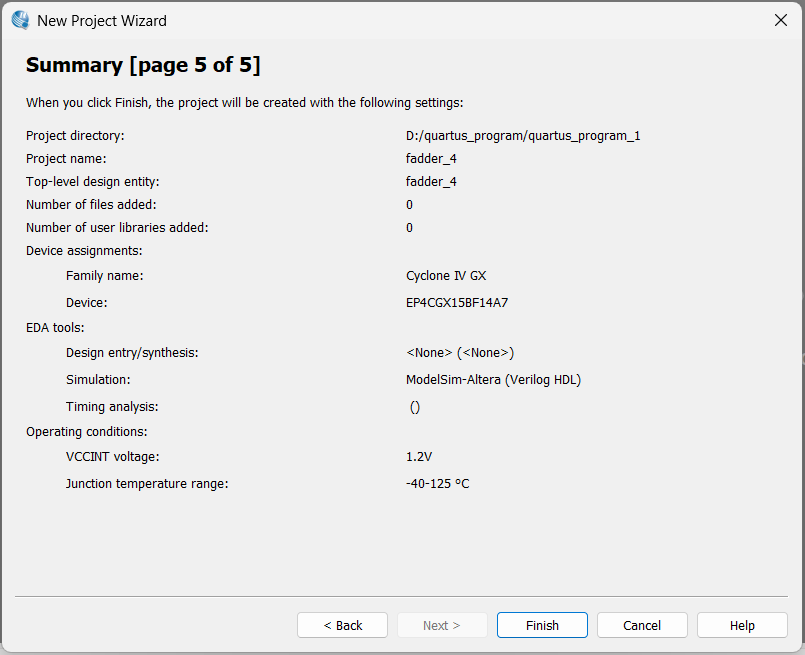

7.下面这张图展示了一些信息,没什么用,直接点击Finish。

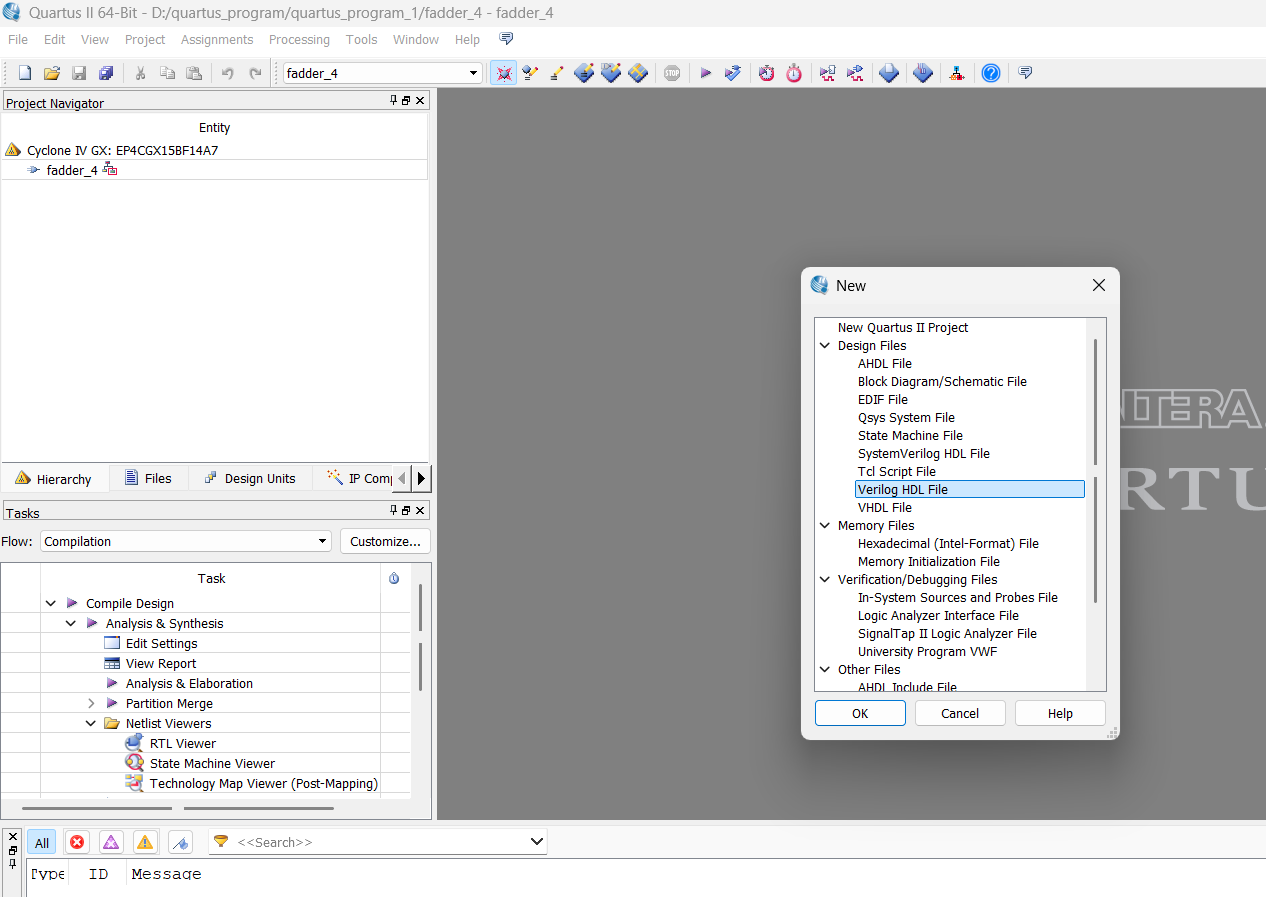

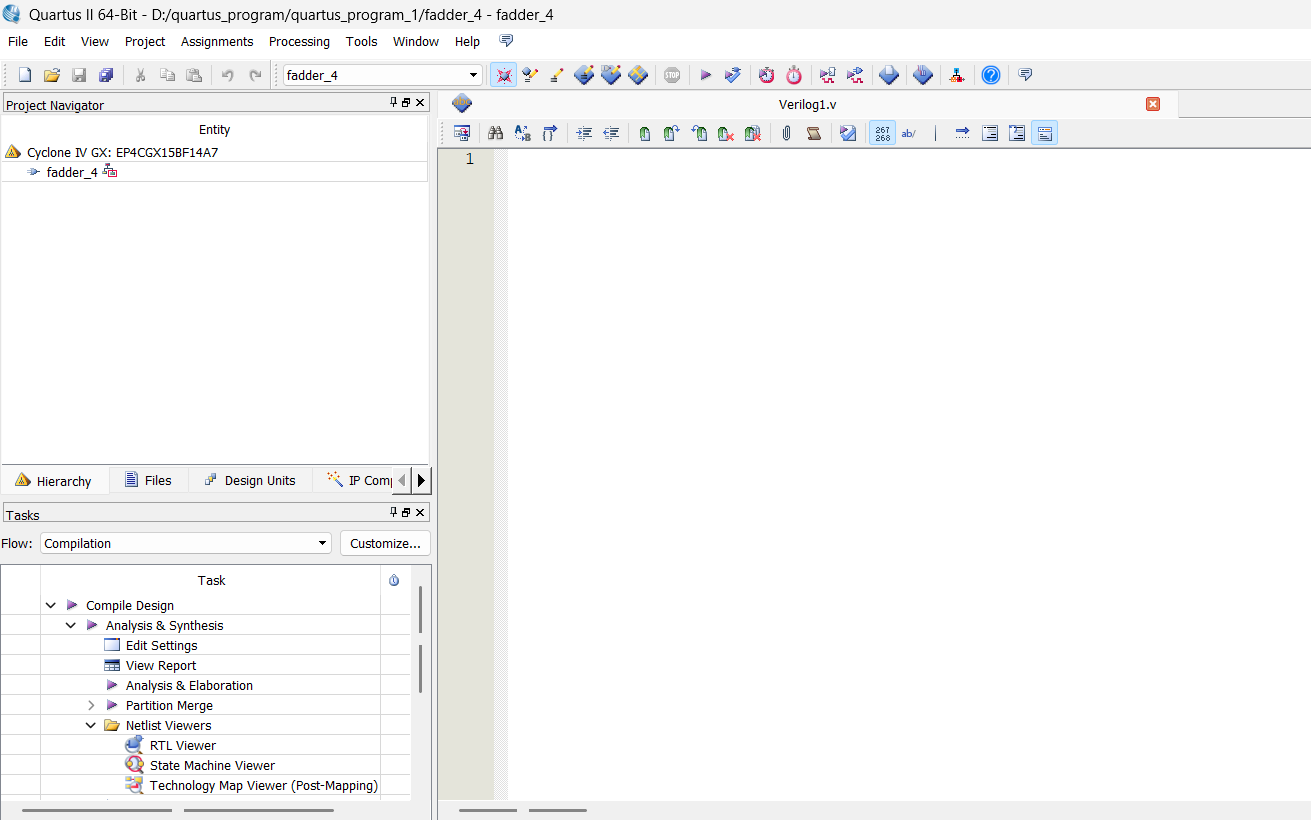

8.点击左上角的File,再点击最上面的New,会弹出如下图所示的New界面,选择Verilog HDL File,再点击OK之后如下面第二张图所示。

9.下面就是实现四位全加器由四个一位的全加器的代码,粘贴到上图所示的Verilog1.v文件当中。

module fadder_4

( i_A, i_B, i_Cin, o_S, o_Cout

);

input [3:0] i_A, i_B;

// 输入端口i_A,i_B

input i_Cin;

// 输入端口i_Cin

output [3:0] o_S;

// 输出端口o_S

output o_Cout;

// 输出端口o_Cout

wire Cout_1, Cout_2, Cout_3;

// wire型数据Cout_1,Cout_2,Cout_3

// 实例化四个1位的全加器

fadder_1 u_fadder_1_1

(

.i_A(i_A[0]),

.i_B(i_B[0]),

.i_Cin(i_Cin),

.o_S(o_S[0]),

.o_Cout(Cout_1)

);

fadder_1 u_fadder_1_2

(

.i_A(i_A[1]),

.i_B(i_B[1]),

.i_Cin(Cout_1),

.o_S(o_S[1]),

.o_Cout(Cout_2)

);

fadder_1 u_fadder_1_3

(

.i_A(i_A[2]),

.i_B(i_B[2]),

.i_Cin(Cout_2),

.o_S(o_S[2]),

.o_Cout(Cout_3)

);

fadder_1 u_fadder_1_4

(

.i_A(i_A[3]),

.i_B(i_B[3]),

.i_Cin(Cout_3),

.o_S(o_S[3]),

.o_Cout(o_Cout)

);

endmodule

module fadder_1

(

i_A,

i_B,

i_Cin,

o_S,

o_Cout

);

input i_A, i_B;

//输入端口i_A,i_B

input i_Cin;

//输入端口i_Cin

output o_S, o_Cout;

//输出端口o_S,o_Cout

// 计算结果值:o_S = i_A⊕i_B⊕i_Cin

assign o_S = i_A ^ i_B ^ i_Cin;

// 计算进位值:o_Cout=(i_A⊕i_B)i_Cin+(i_A)(i_B)

assign o_Cout = (i_A ^ i_B) & i_Cin | i_A & i_B;

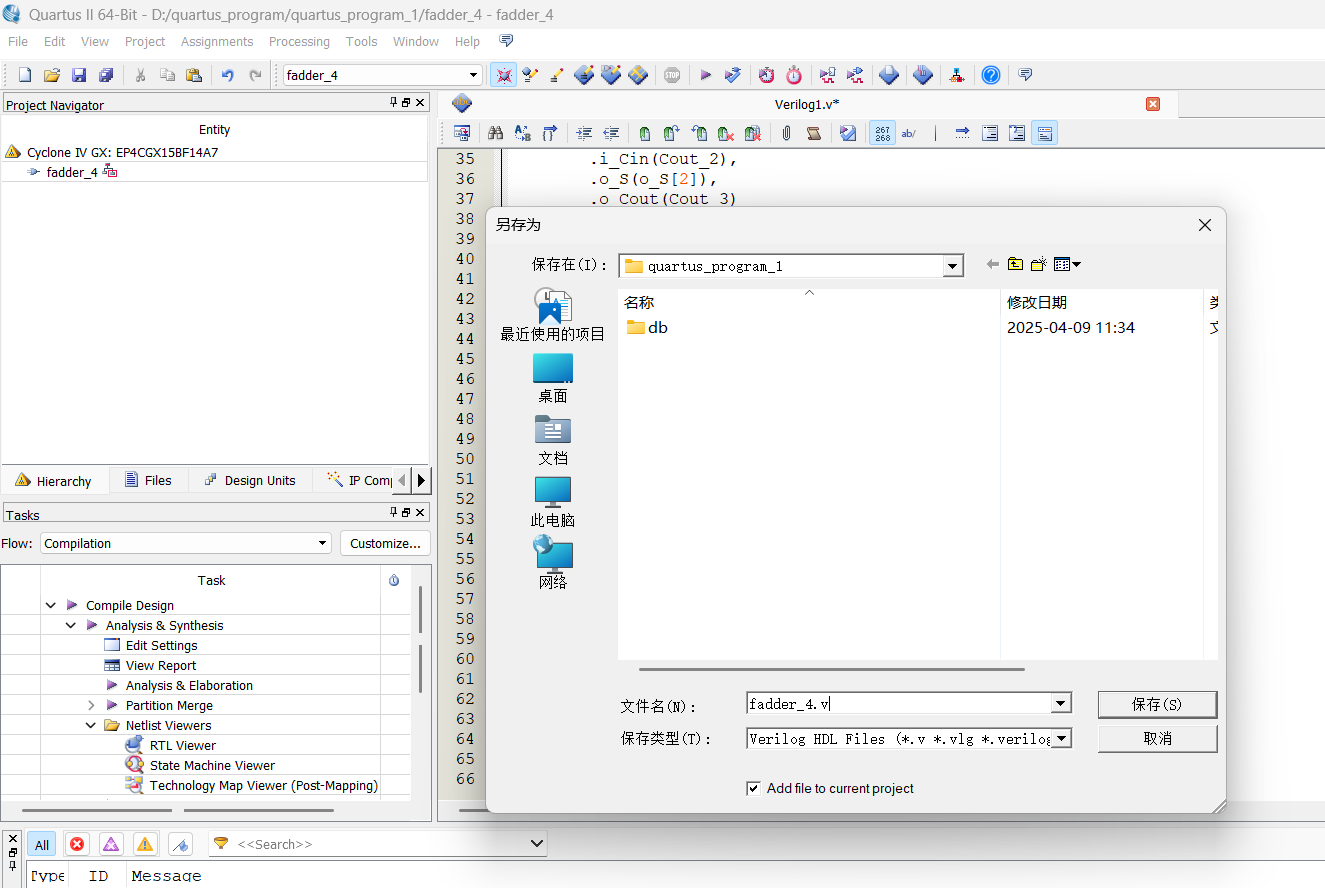

endmodule 10.如下图所示,点击左上角的蓝色小电视进行保存文件,文件名为fadder_4.v,点击保存。

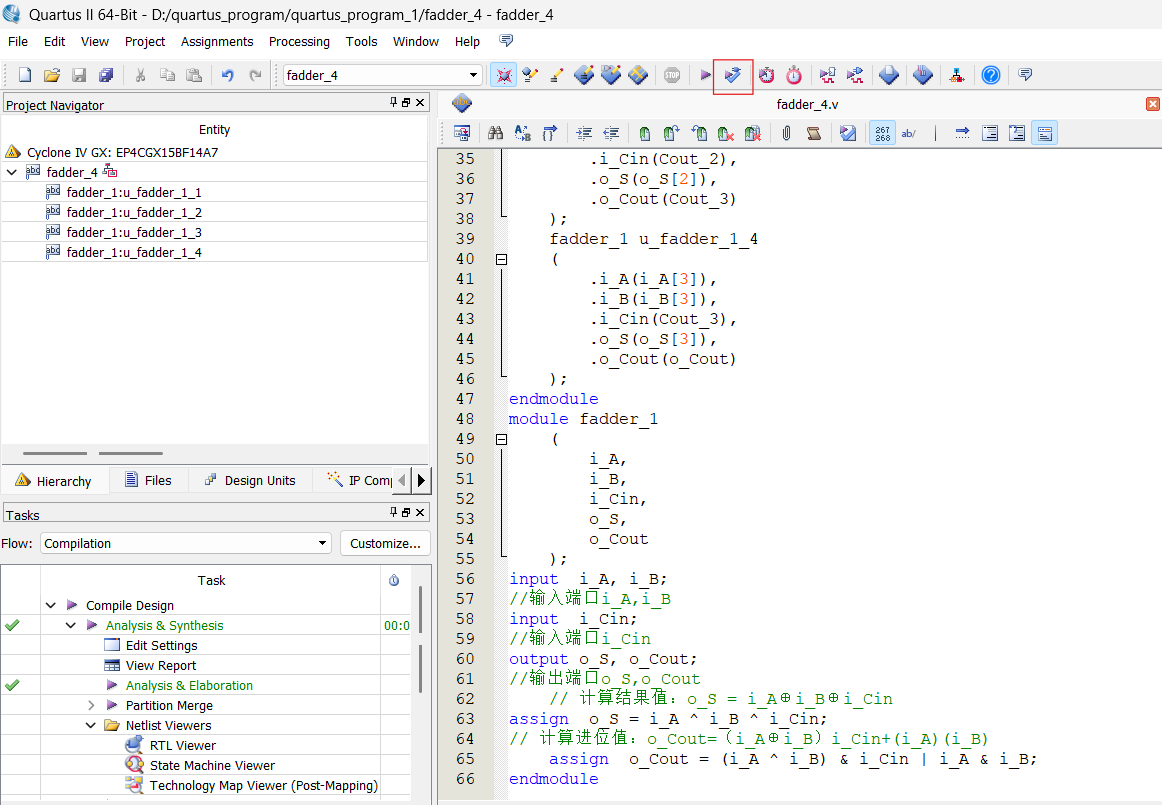

11.如下图所示,点击标注的红色框那里。

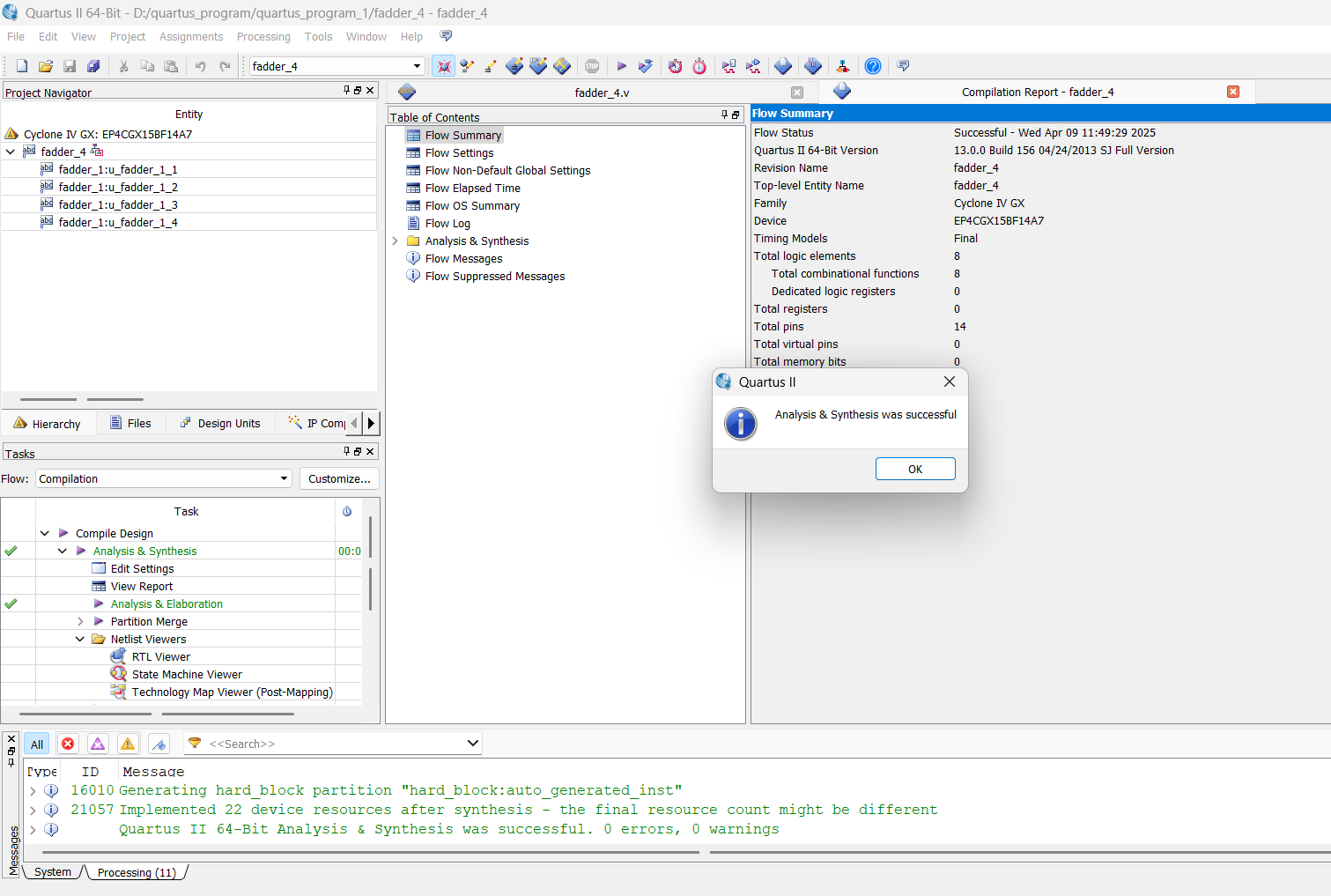

12.点击完红色框运行结果如下图所示,这里显示成功了。

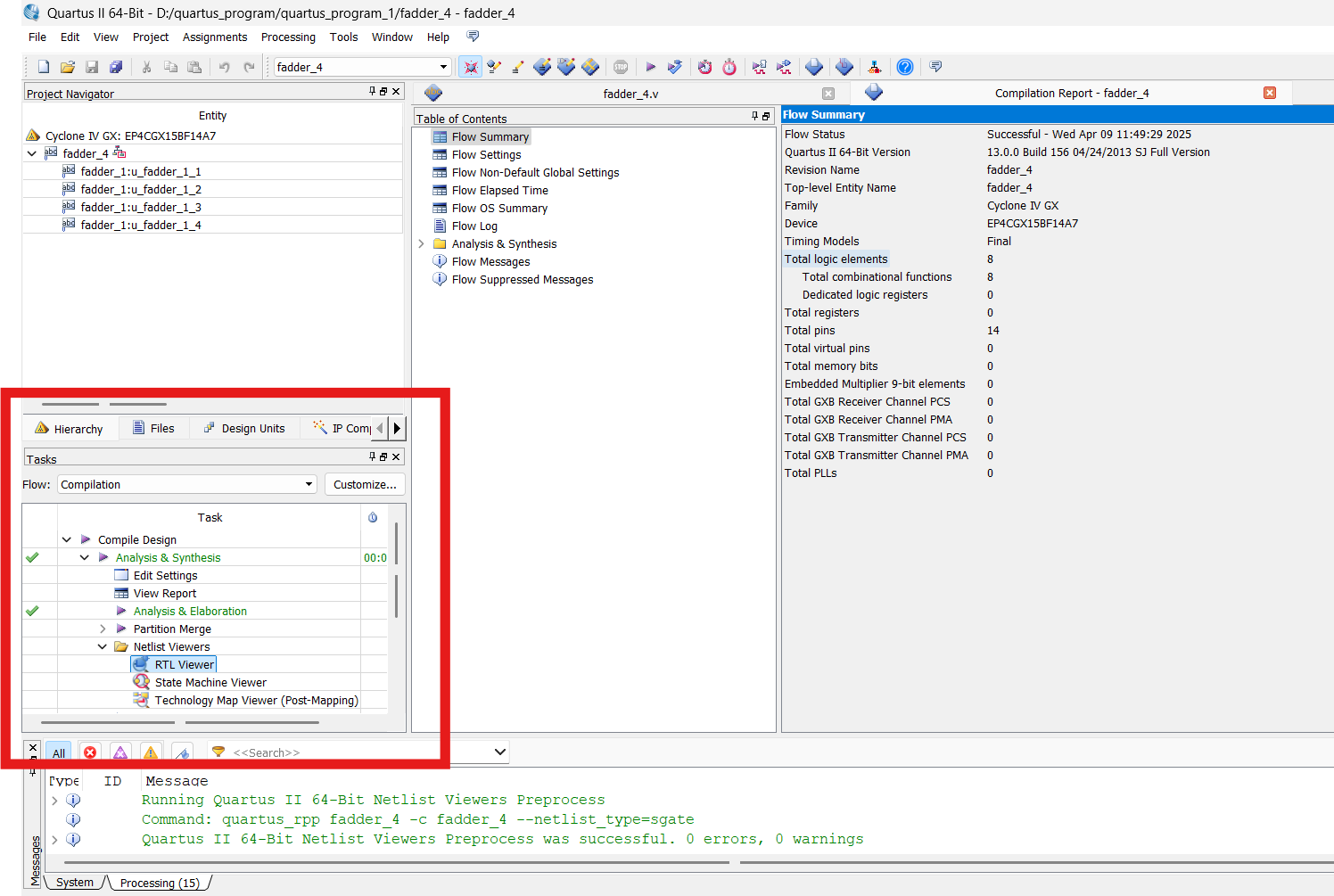

13.看红色框那里,在Analysis & Synthesis下,点击RTL Viewer。

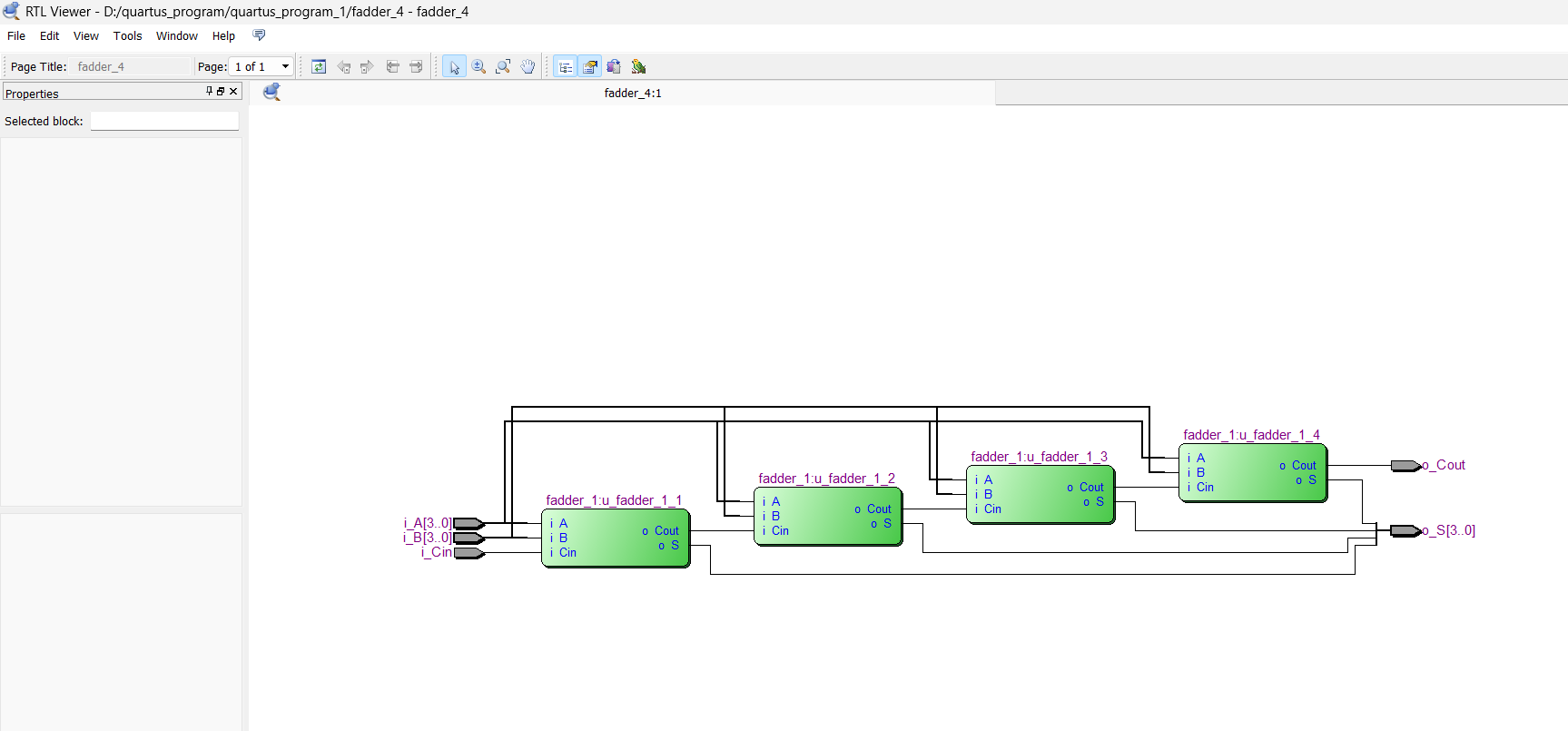

会弹出下面这张图片,这就是生成的RTL电路图。

14.接下来实现仿真波形。点击左上角的File,再点击New,选择University Program VWF,创建一个向量波形文件,点击OK。

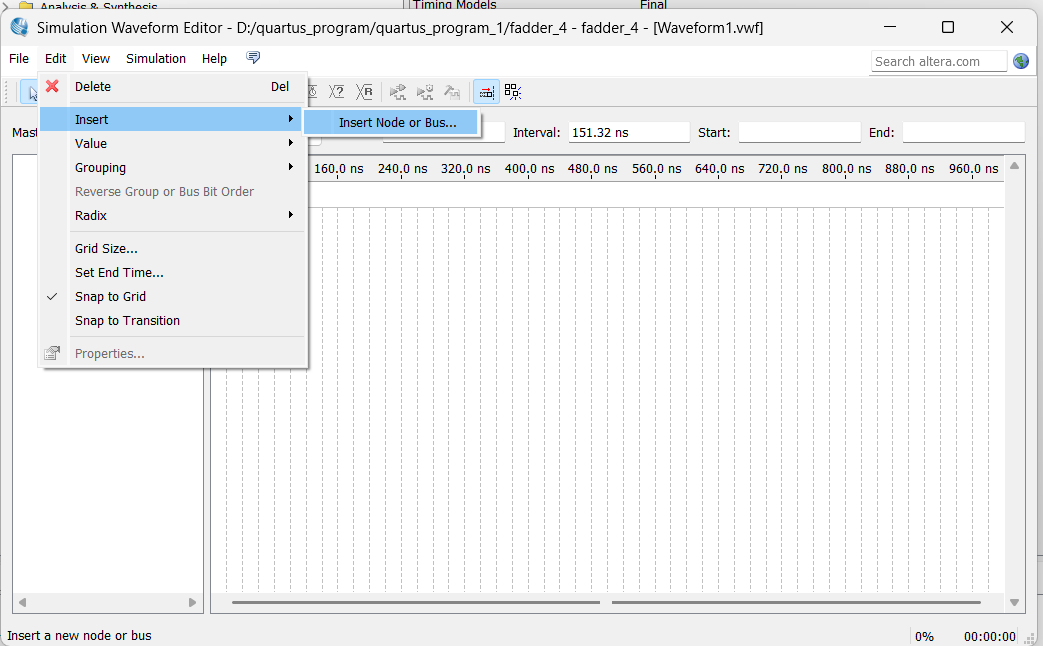

15.点击Edit ---> Insert ---> Insert Node or Bus…

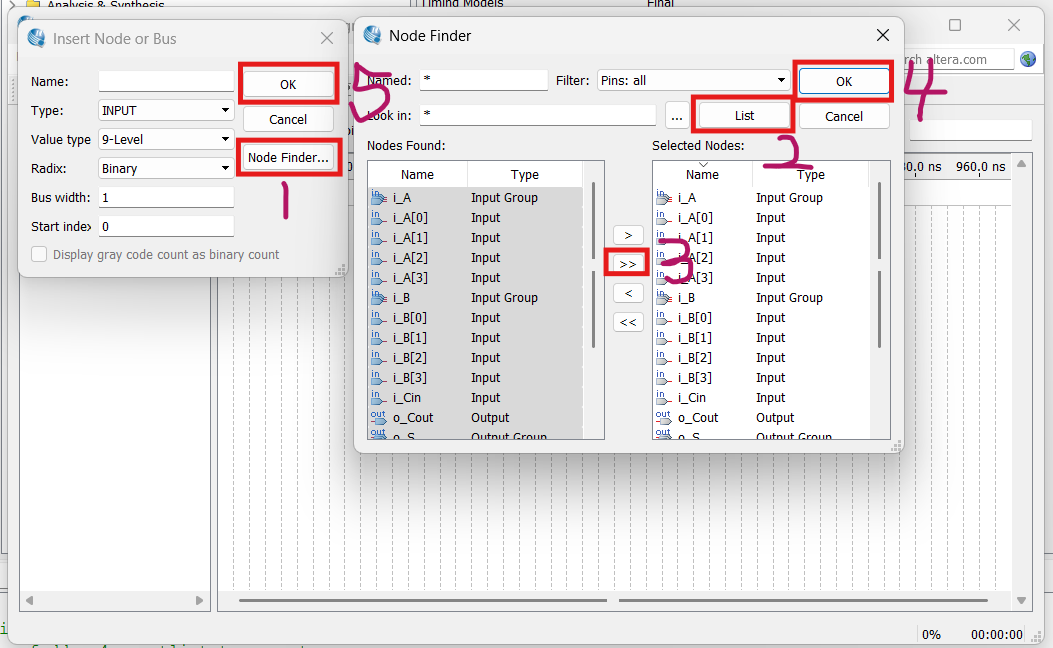

16.按照下图所示的这五步来。

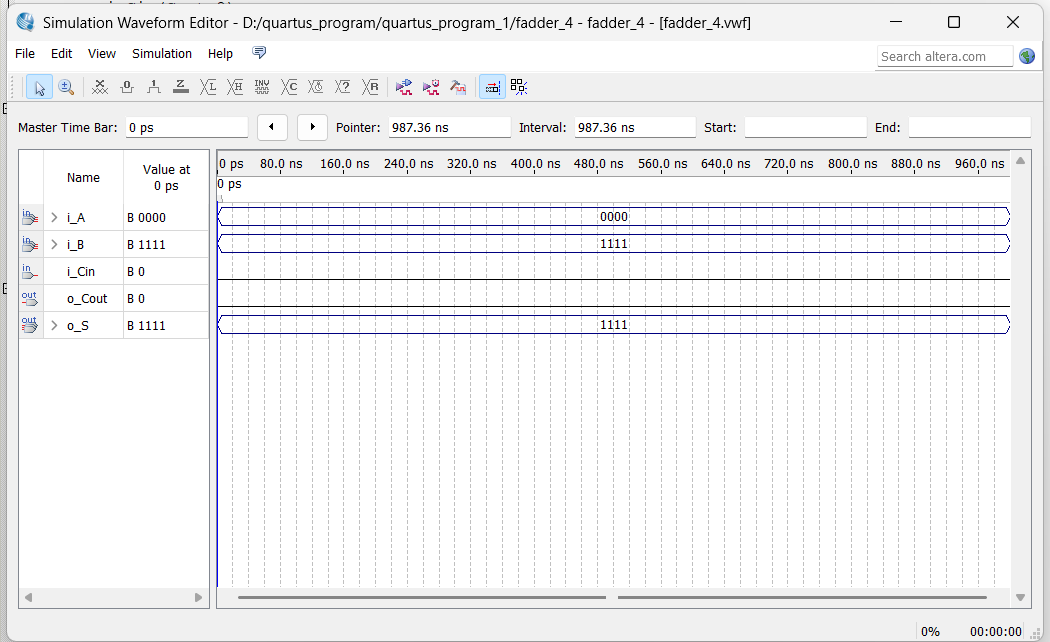

17.看到下面所示的图片就可以了,这里我把.vwf文件的名字改为了fadder_4。

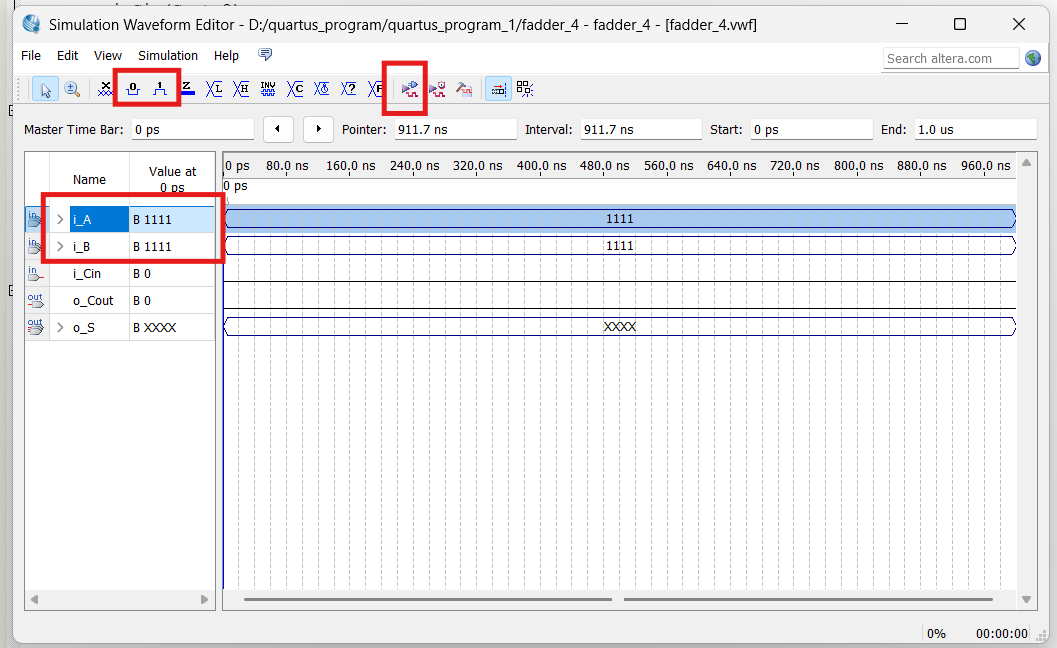

18.如下图所示,点击左上角那个框里的0或1波形,对i_A或i_B进行修改,在点击右边的红框启动仿真功能。

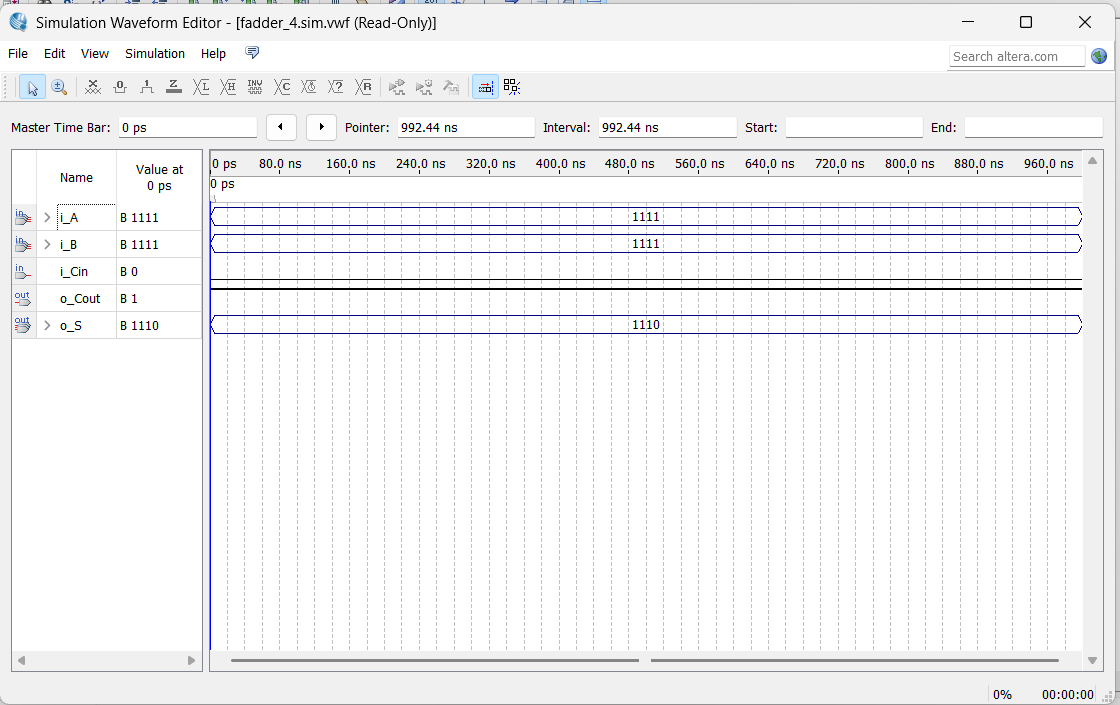

19.启动成功后可以看到下面这张图,到这里,整个流程就结束了。

20.在最后我说一下,如果大家遇到了报错的问题,很有可能是因为Quartus没有破解完成的原因,在这里我推荐大家去看以下由Willliam_william所写的

Verilog学习之路(1)— Quartus II 13.0下载安装和HelloWorld

可以看这篇文章重新下载Quartus,并且在下载时最好关闭Windows安全防护和防火墙。

4940

4940

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?