一、静态随机存储器SRAM

(一)存储元

1、概念

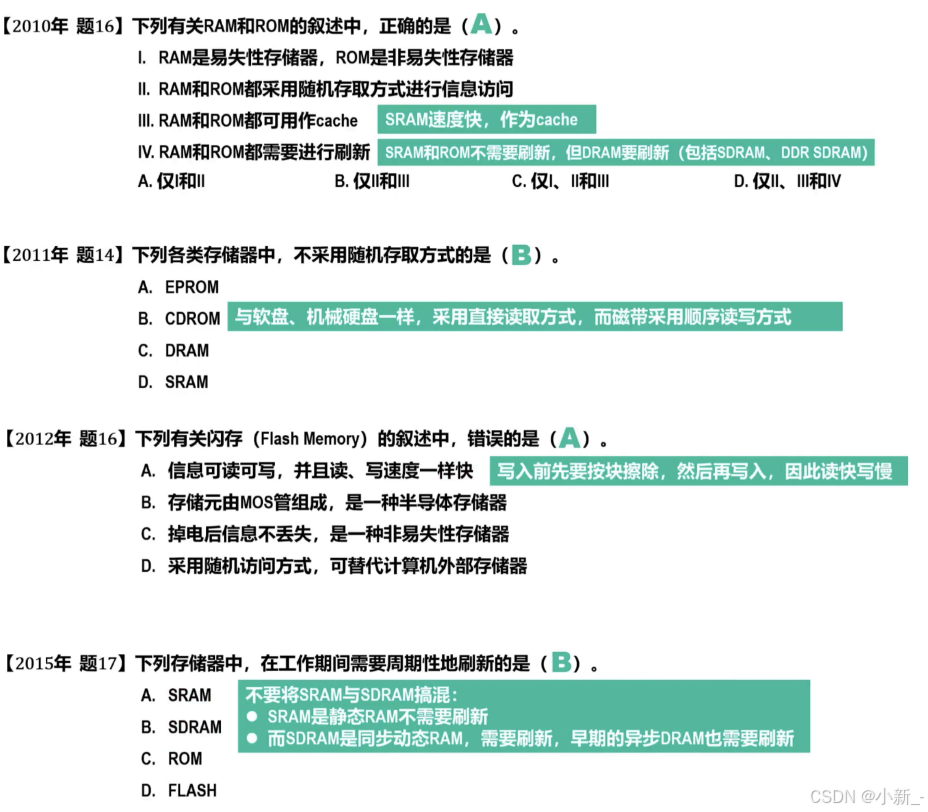

- 静态随机存取存储器SRAM(Static Random-Access emory)是随机存取存储器RAM的一种。

1、所谓"静态",是指这种RAM只要保持通电,其内部所存储的数据就可以保持不变,而不需要进行周期性地刷新。相比之下,动态随机存取存储器DRAM(Dynamic Random-Access Memory)则需要。

请同学们注意:

一旦断电,SRAM和DRAM内部存储的数据还是会消失的,也就是说SRAM和DRAM属于易失性存储器,这与属于非易失性存储器的只读存储器ROM (Read-Only Memory)是不同的。

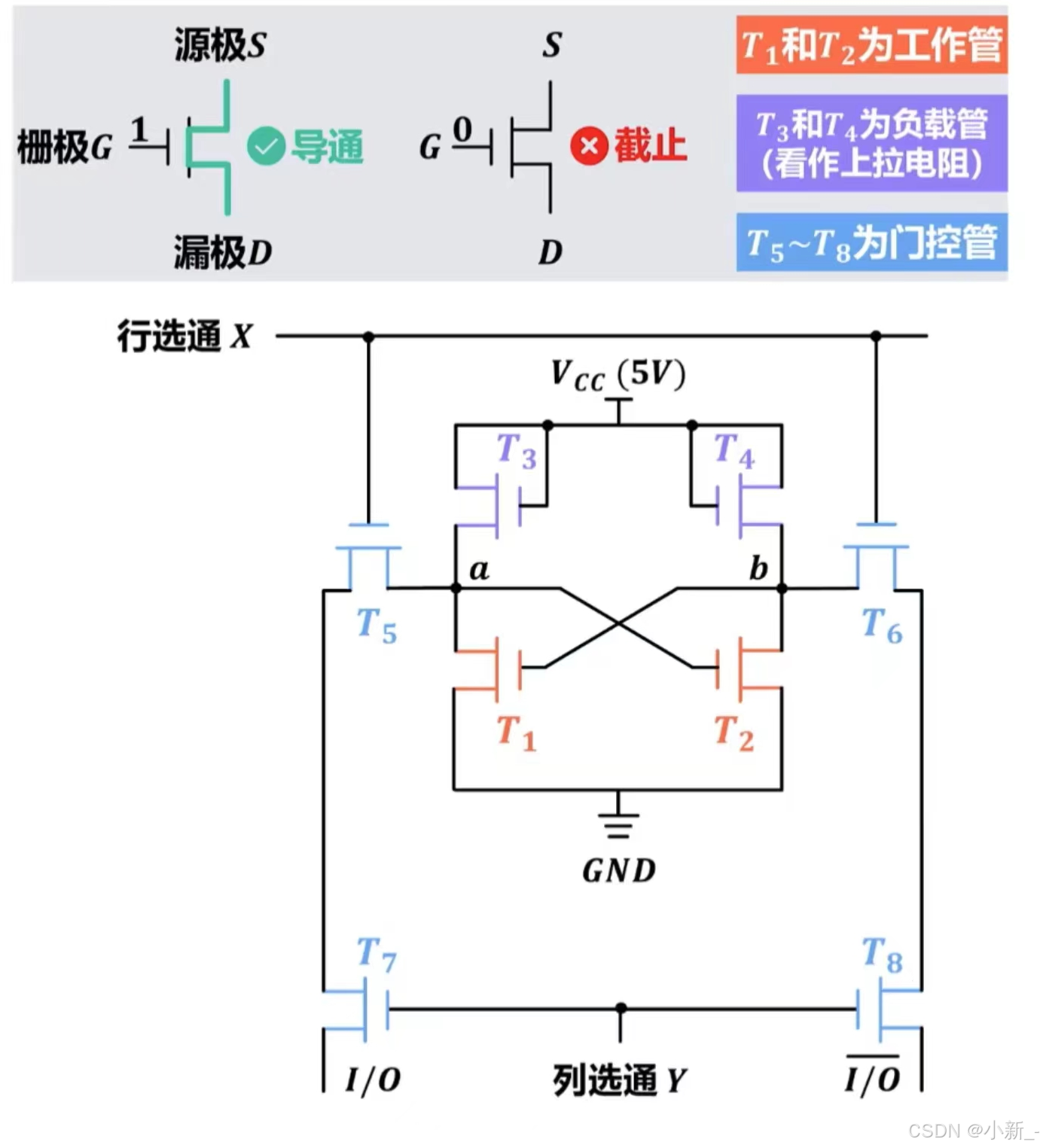

2、目前,SRAM内部的存储元(存储1个二进制位的单元)一般采用多个金属◇氧化物半导体场效应晶体管MOSFET(Metal-Oxide-Semiconductor Field-EffectTransistor)来构建,MOSFET常简称为MOS管。

2、特点

- 上电后的初始状态随机(即存储元的存储内容随机)。

- 读操作不会破坏原有数据。

- 只要不断电,信息一直保存,不需要刷新。

- 电源Vcc通过负载T3、T4不断为工作管T1或T2提供电流,以保存信息,因此功耗大。

- 使用晶体管的数量多,占用晶圆面积大,成本高,价格昂贵,因而不适合用于更高存储密度且低成本的应用,例如PC的内存。

- 速度快,常用于微处理器的cache。

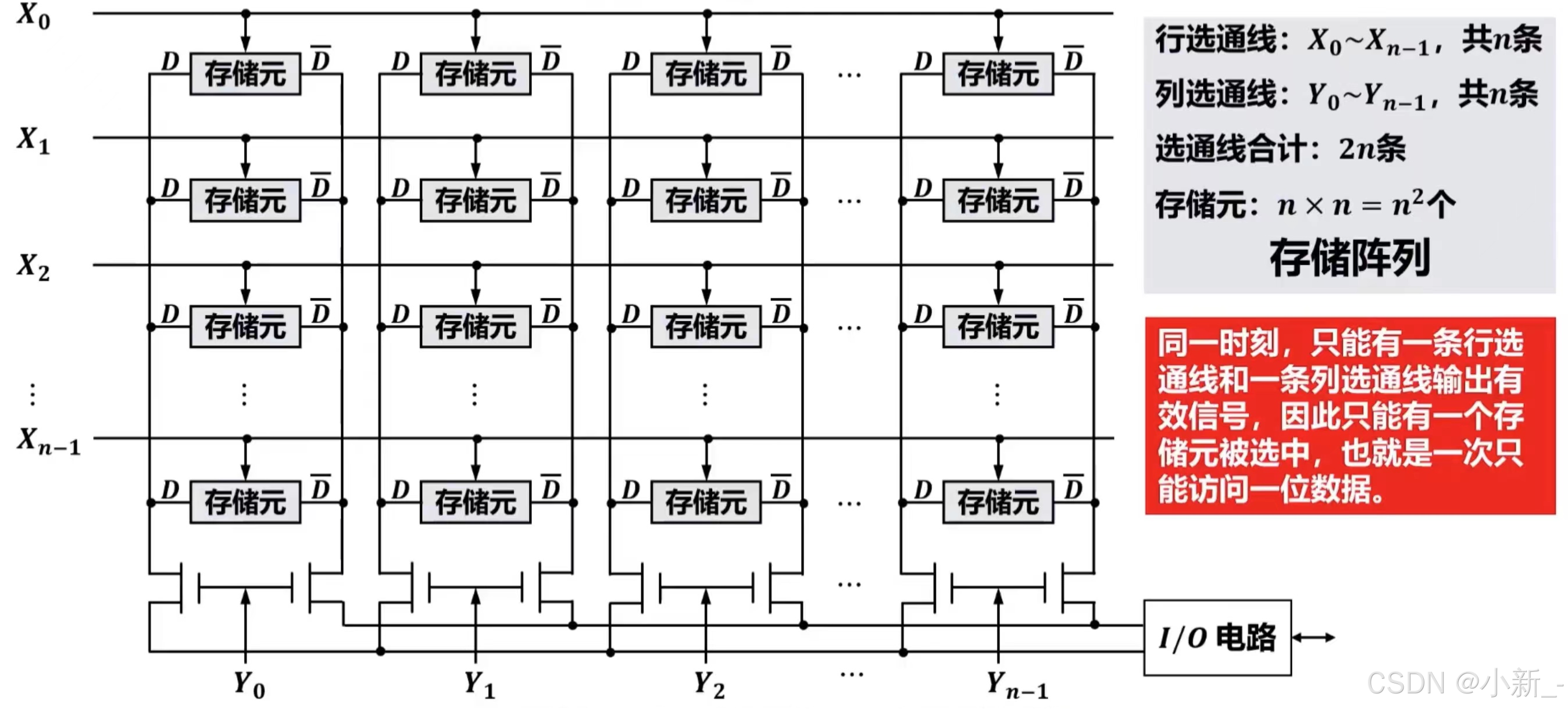

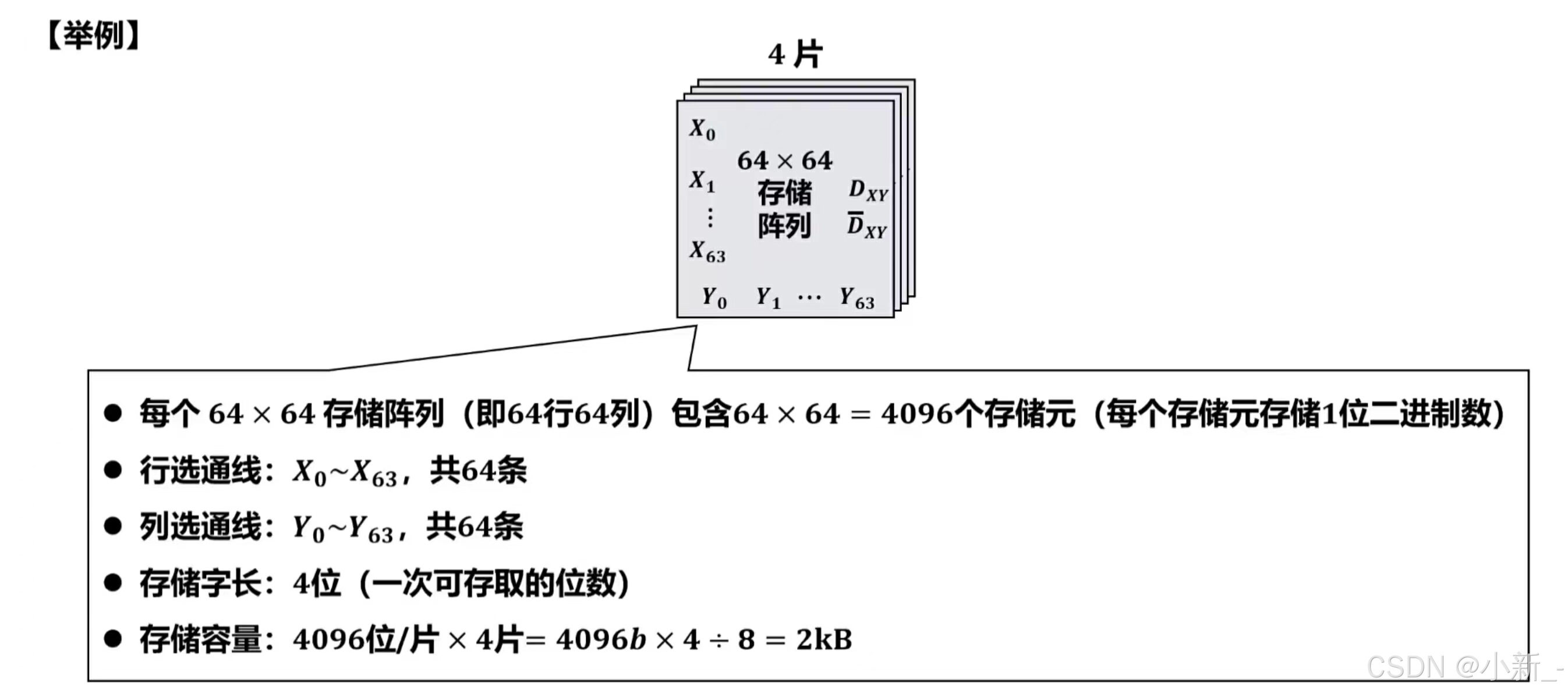

(二)存储元扩展与存储阵列扩展

1、存储元扩展

2、存储阵列扩展

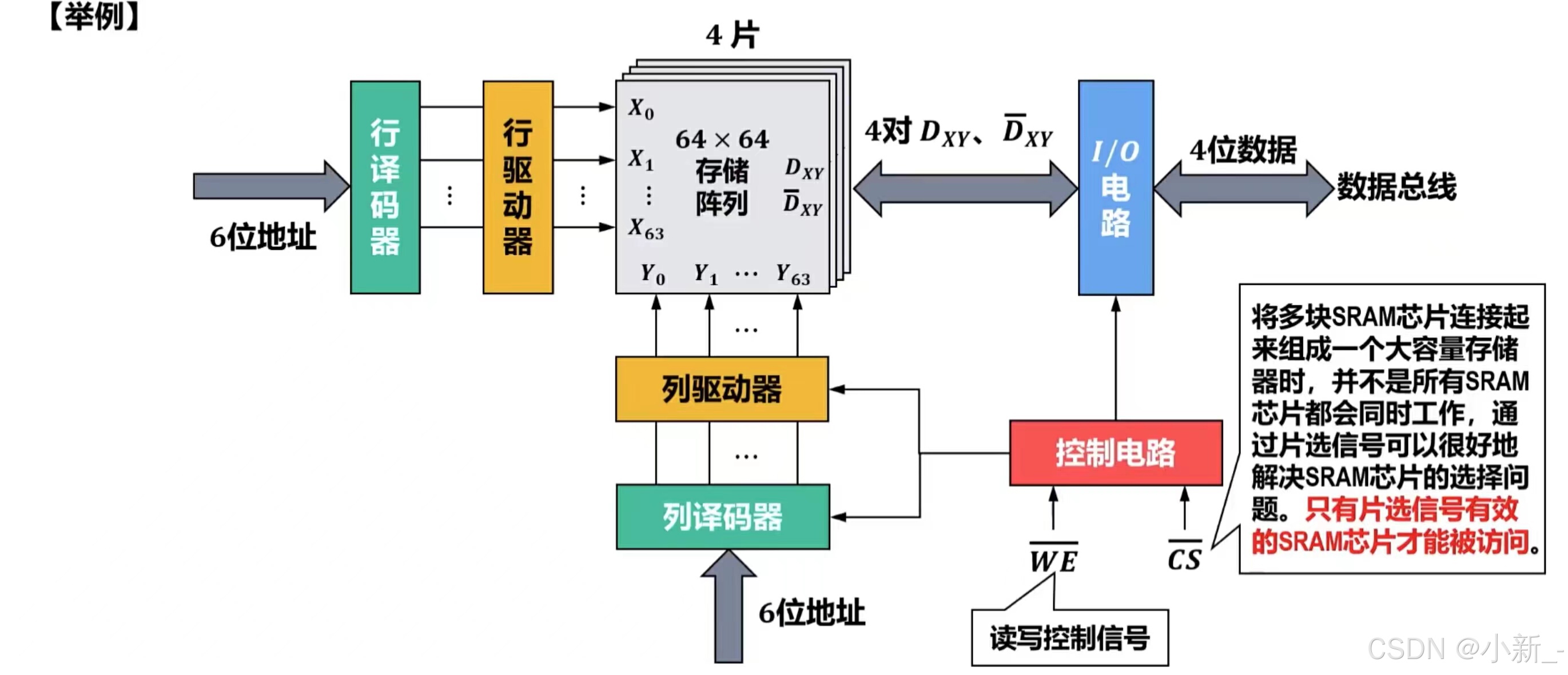

(三)存储器结构及其芯片实例

1、存储器结构

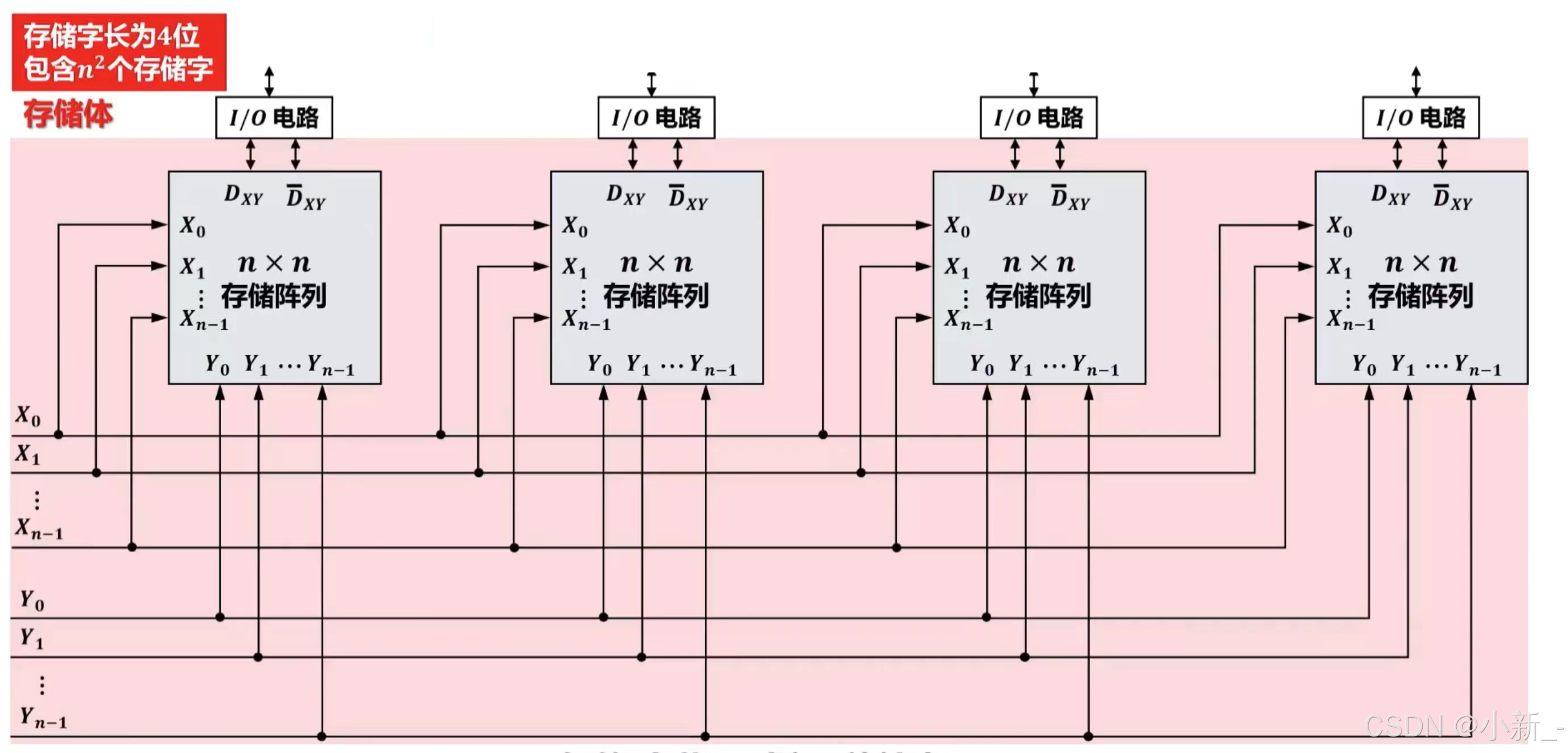

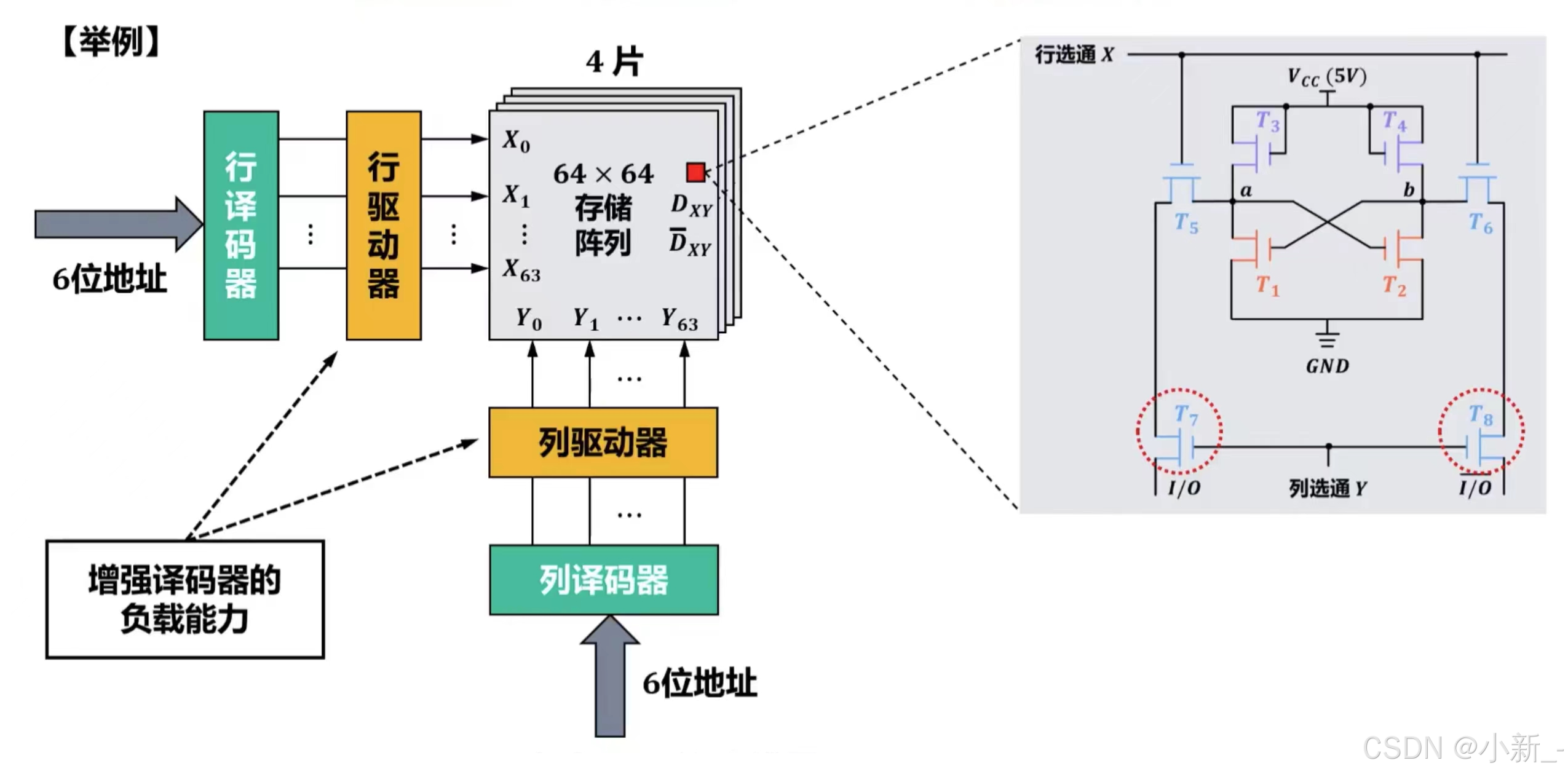

- 行译码器的每个译码输出信号线都要同时驱动这一行上所有存储元的TS、T6两个门控管。

- 4片存储阵列并发,每个行译码输出信号线要驱动2x64x4=512个门控管,负载大。

- 列译码器的每个译码输出信号线都要同时驱动这一列上所有存储元共享的T7、T8两个门控管。

- 4片存储阵列并发,每个列译码输出信号线要驱动2x4=8个门控管,负载较大。

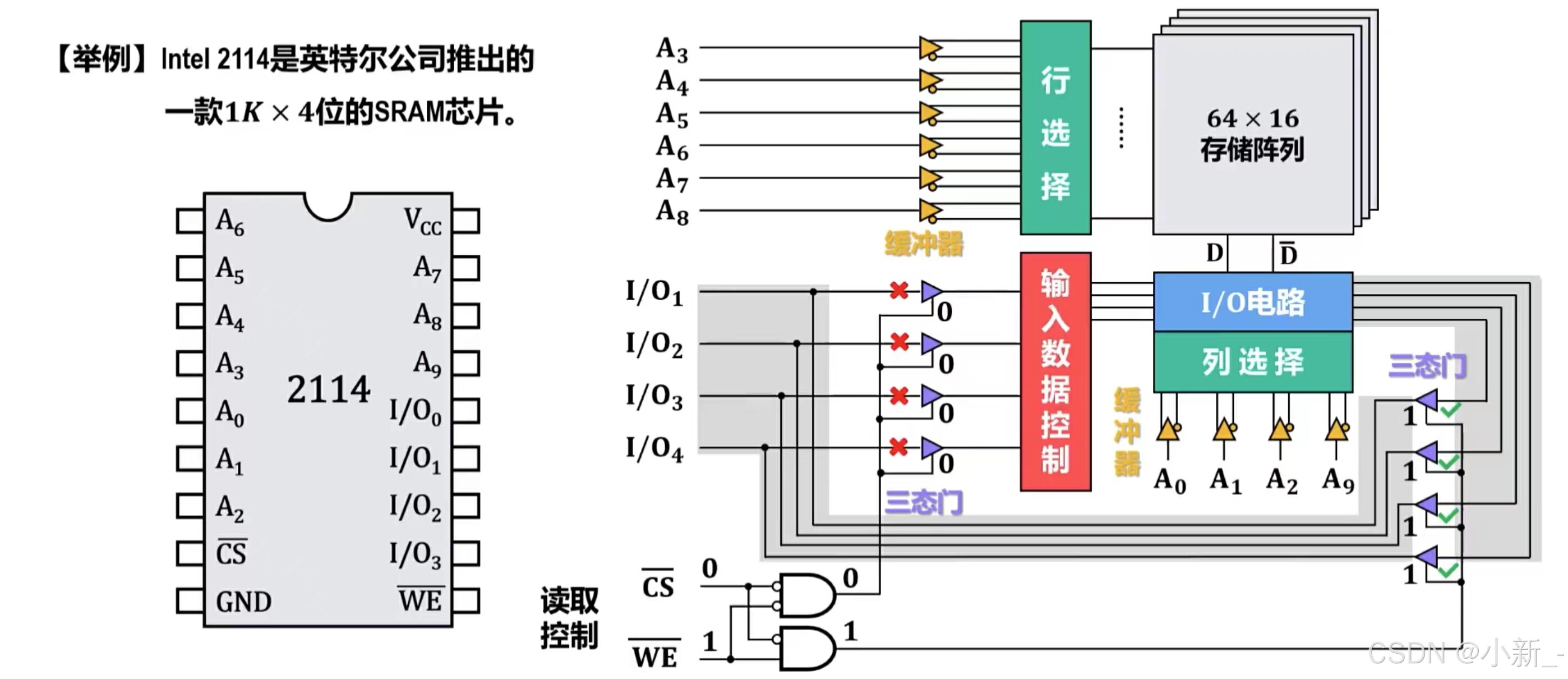

2、存储器芯片实例

二、动态随机存储器DAMR

(一)存储元及其扩展

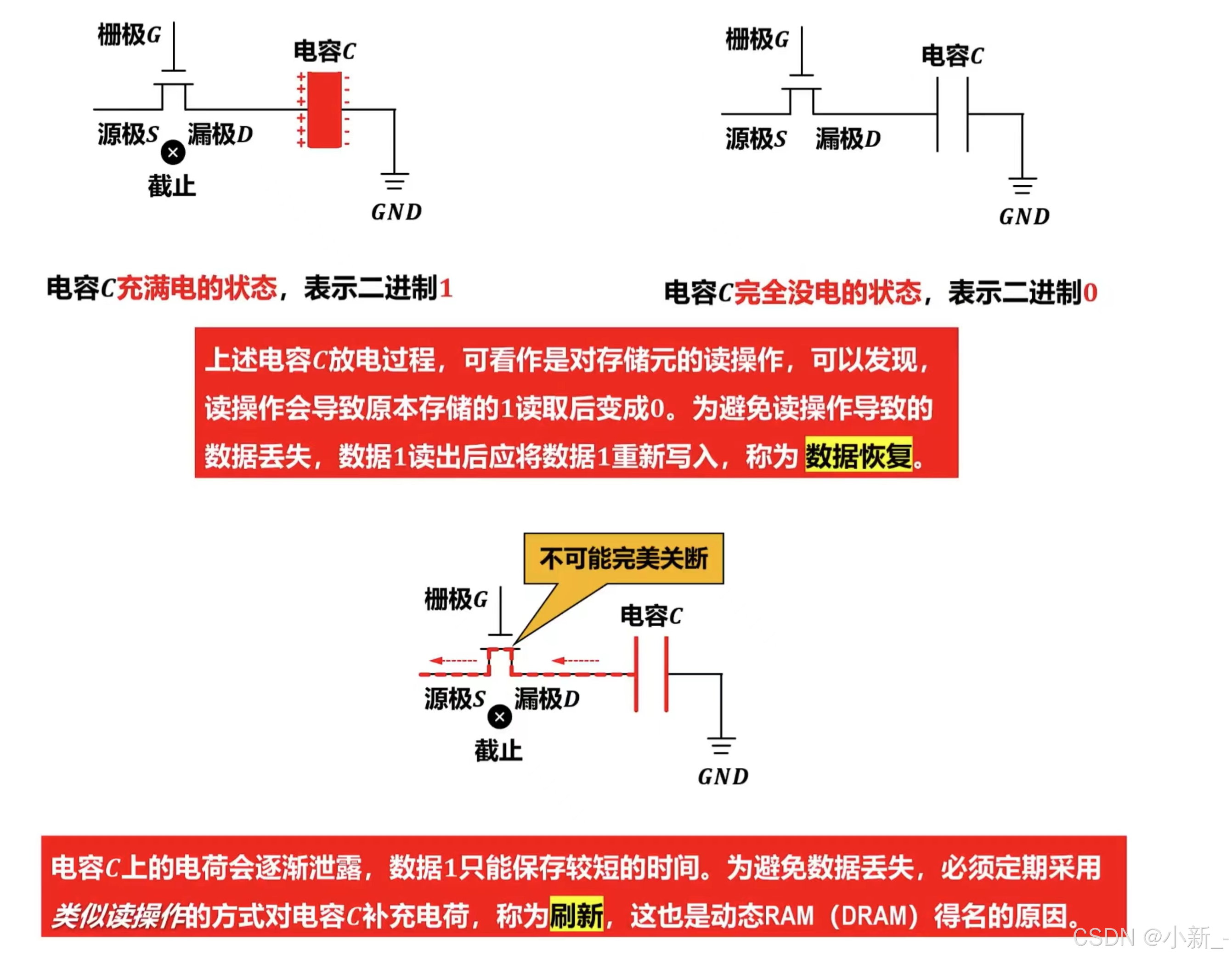

1、存储元

DRAM的存储元结构如图所示

在了解DRAM的组成以及工作原理之后,我们举例说明DRAM存储元的扩展

2、DRAM存储元的扩展

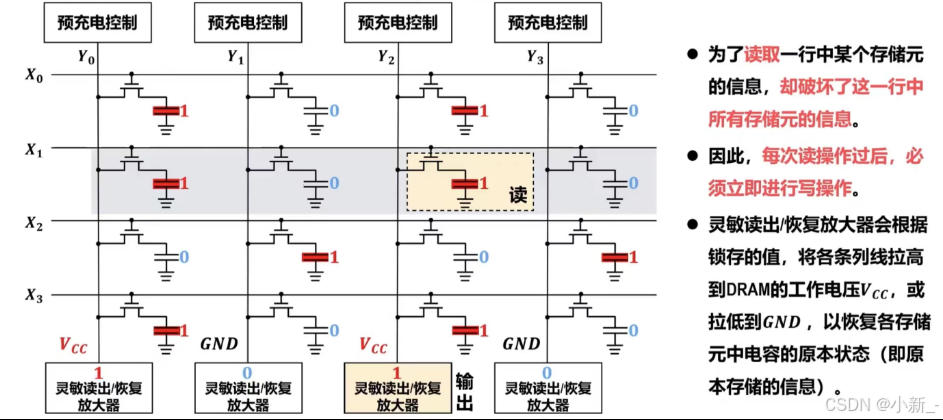

将16个DRAM存储元排列成四行四列的二维阵列形式,每一行所有存储元的MOS管的栅极用一条行线连接起来,每一列所有存储元的MOS管的源极用一条列线连接起来。另外,每一列还需要预充电控制电路以及灵敏读出/恢复放大器。如图所示:

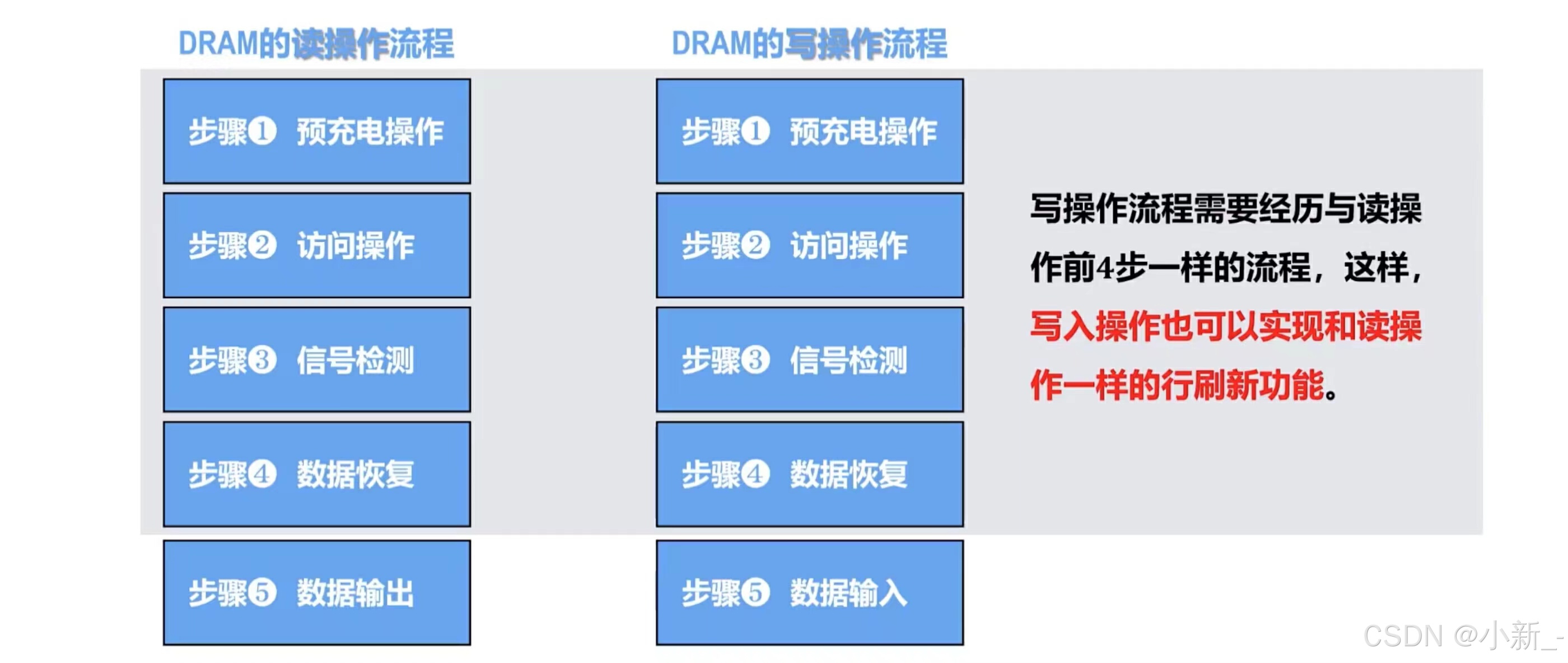

DRAM的读写操作

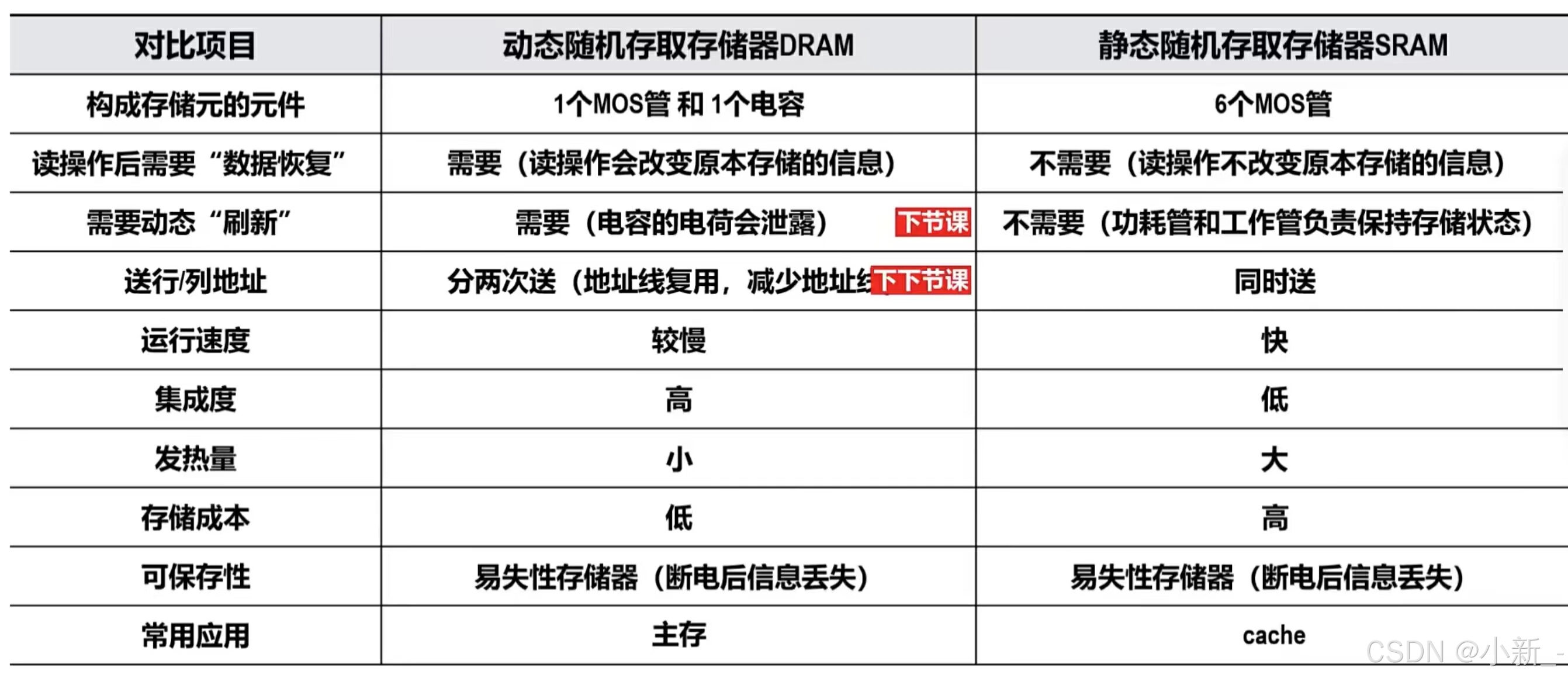

3、DRAM与SRAM的对比

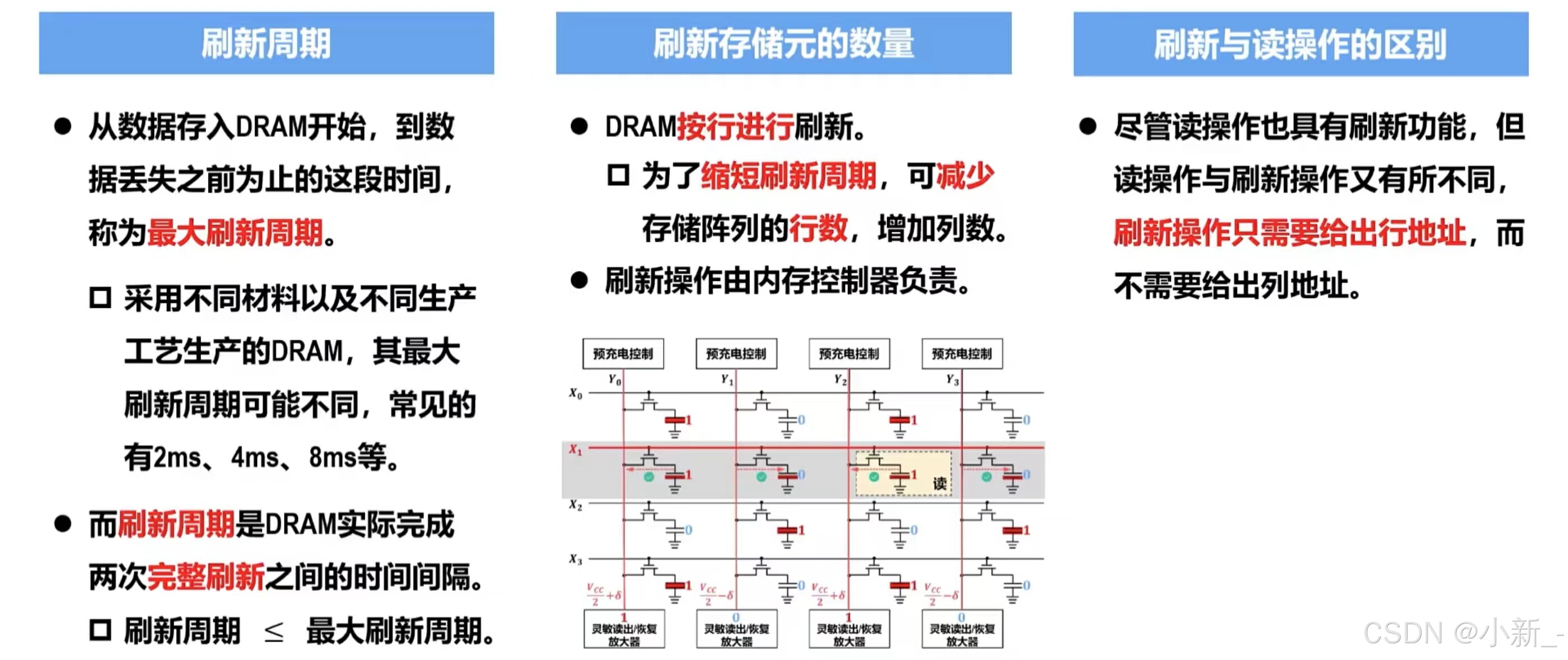

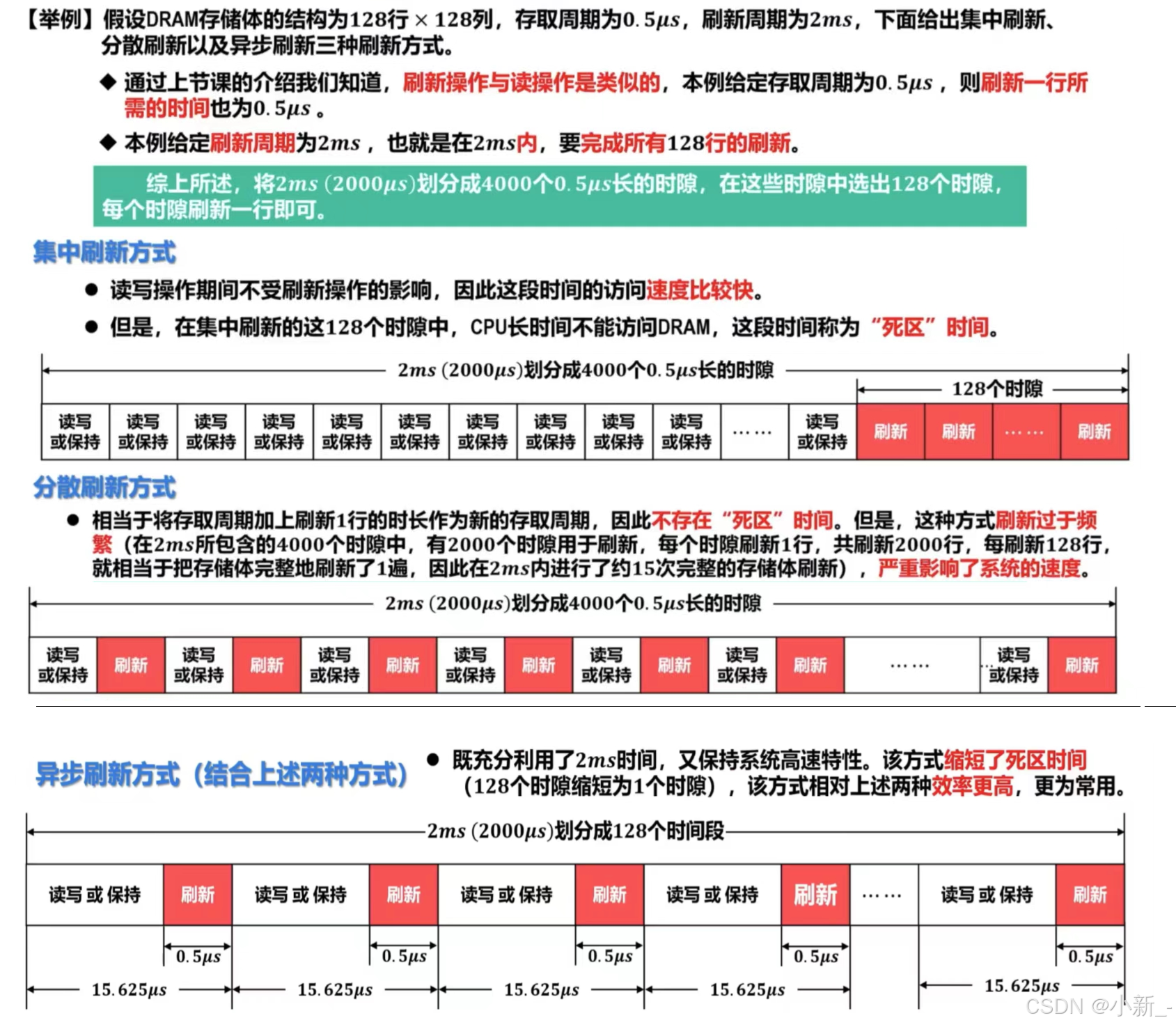

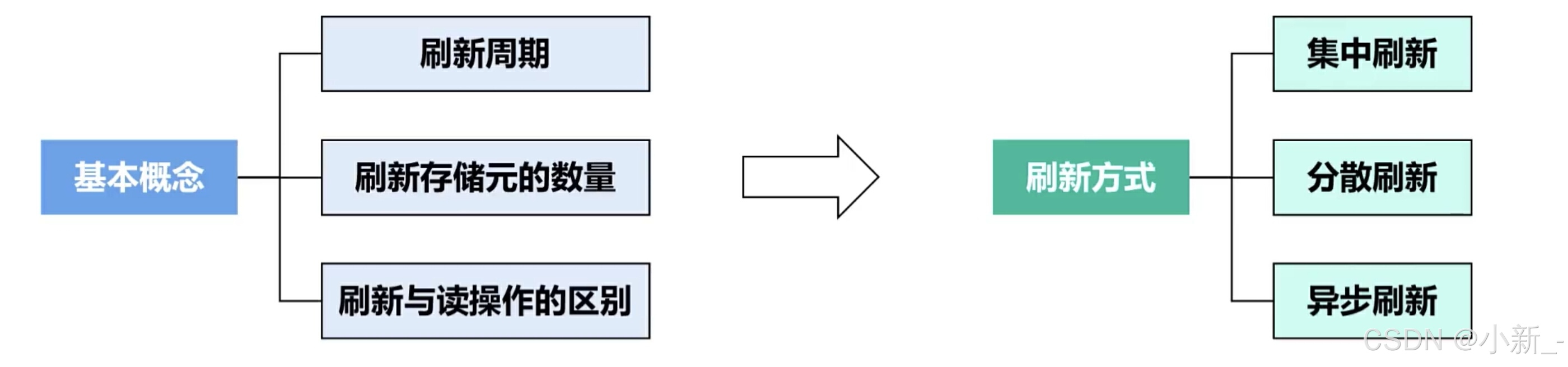

(二)DRAM的动态刷新

1、相关基本概念

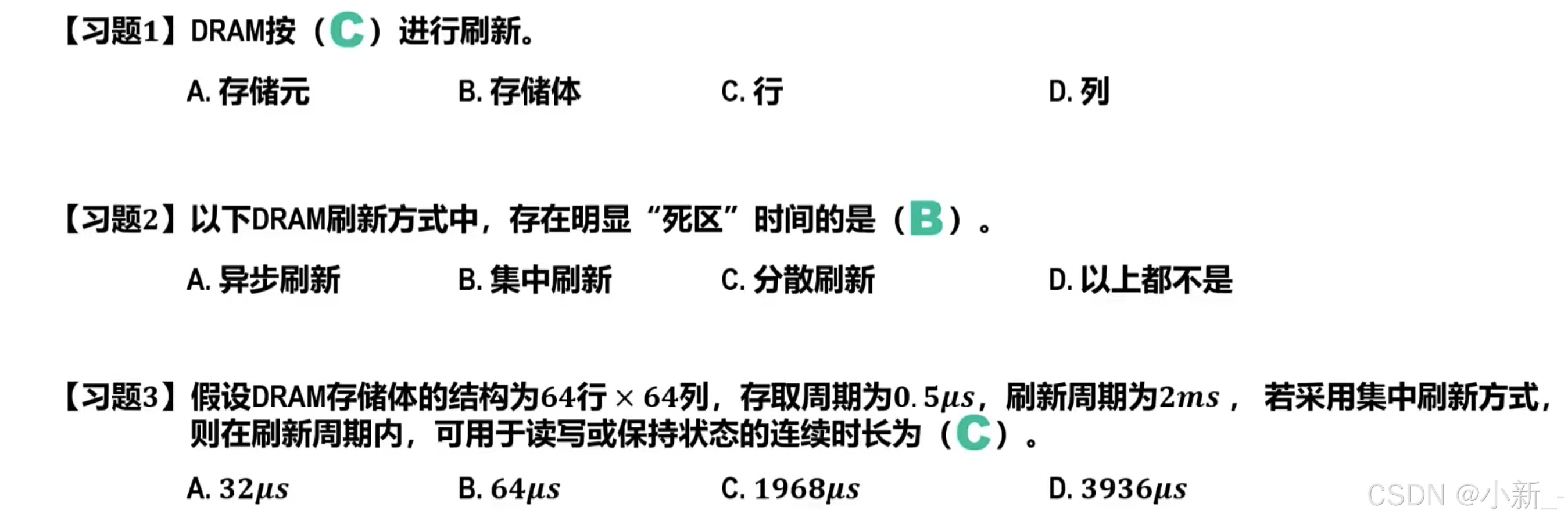

2、刷新方式

【练习】

【总结】

(三)存储器芯片发展及DRAM发展

1、存储芯片实例

三、只读存储器

1、概念

只能从其读出信息、而不能向其随意写入信息的存储器,称为只读存储器(Read-onlyMemory,ROM)

通过特定方式将信息写入ROM后,信息就固定在ROM中,即使电源断电,所保存的信息也不会丢失,也就是说,ROM属于非易失性存储器。

2、分类及其简介

按照制造工艺的不同,ROM可分为:

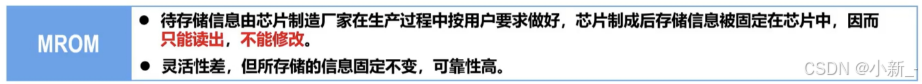

1、掩膜式只读存储器(MasKROM,MROM)

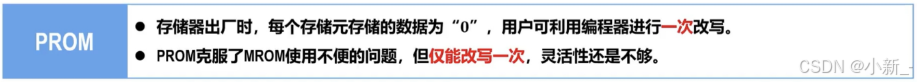

2、可编程只读存储器(ProgrammableROM,PROM)

3、可擦除可编程只读存储器(Erasable Programmable ROM,EPROM)

4、电可擦除可编程只读存储器(Electricaly Erasable ProgrammableROM,EEPROM或E2PROM)

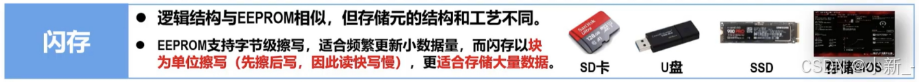

5、闪存

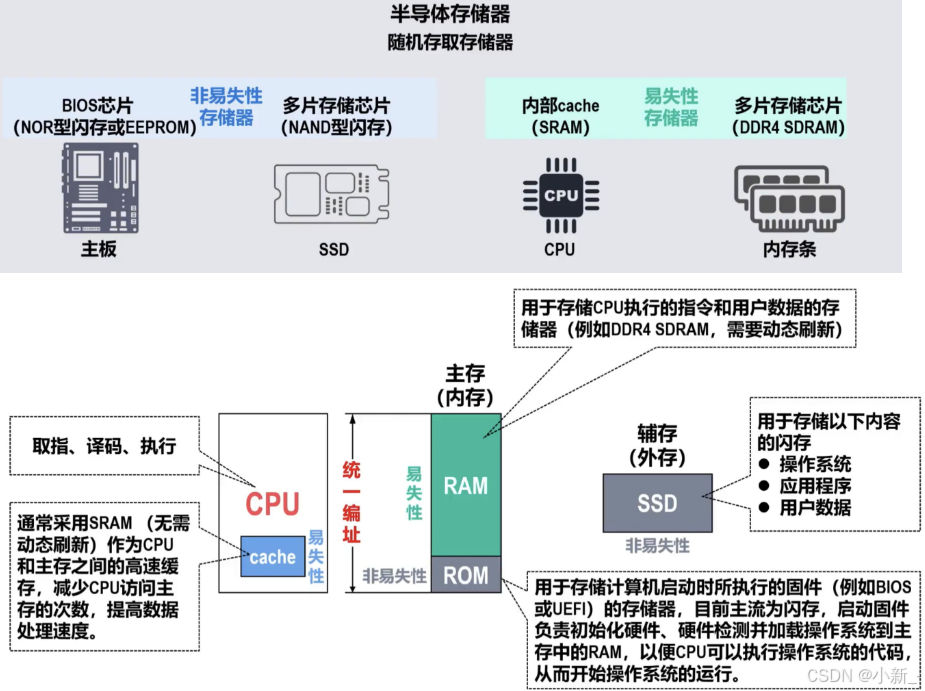

3、PC用到的半导体存储器

4、练习

4451

4451

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?