最简单的D触发器

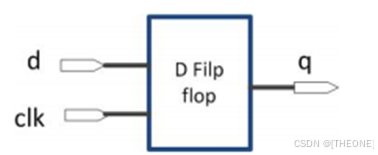

如下为最简单的D触发器的实现代码,图3.4为其模块示意图。表3.4为其真值表。

always @(posedge clk) begin

q <= d ;

end

图 3.4 简单D触发器示意图

表 3.4 简单D触发器的真值表

| 时钟信号CLK |

输入D |

输出Q |

| 其余时刻 |

X |

Qprev |

| 上升沿 |

1 |

1 |

| 上升沿 |

0 |

0 |

//设计代码

`timescale 1ns / 1ps

module d(

input wire d,

input wire clk,

output reg q

);

always @(posedge clk) begin

q <= d ;

end

endmodule

//仿真代码

`timescale 1ns / 1ps

module dd(

);

reg d;

reg clk;

wire q;

d d1(d,clk,q);

initial begin

clk = 0;

forever begin

#10 clk=~clk;

end

end

initial begin

d=0;

forever begin

#55 d=~d;

end

end

endmodule

3.2.2带低电平有效异步复位端的触发器

如下为带低电平有效异步复位端的触发器实现代码,图3.5为其模块示意图。表3.5为其真值表。

always @(posedge clk or negedge reset )

begin

if ( !reset )

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?