一 理论

fpga是并行执行的,当处理需要顺序解决的事时,就要引入状态机。

状态机:

简写FSM,也称同步有限状态机。

分为:more型状态机,mealy型状态机。

功能:执行该事件,然后跳转到下一事件。

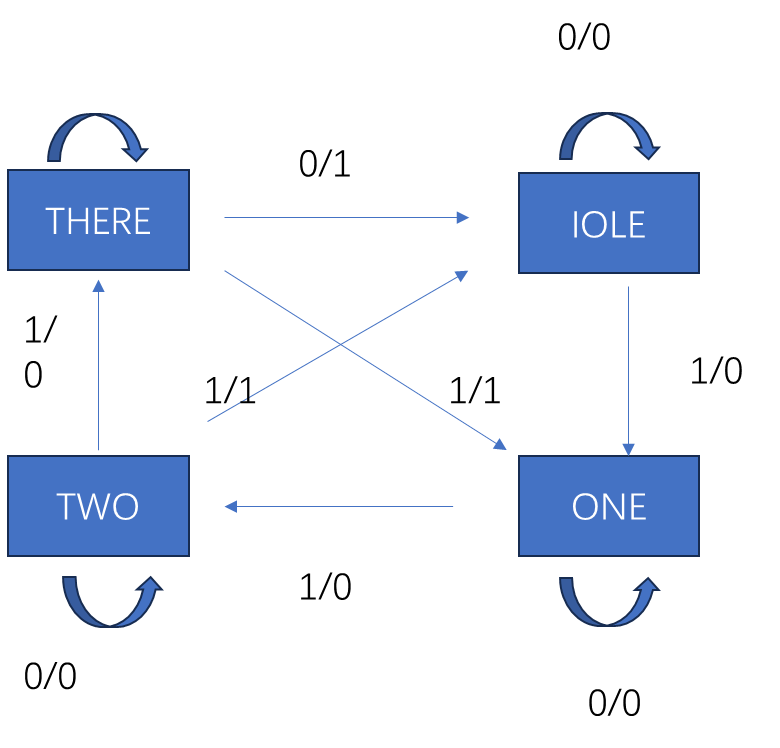

状态转移图:

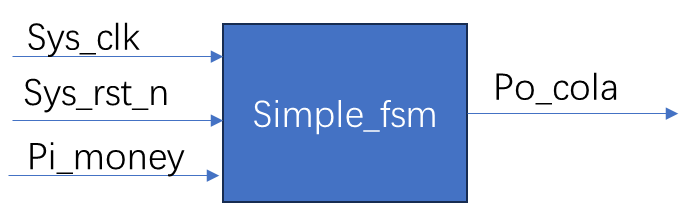

二 电路

写功能模块(可乐机),配置io;

三 信号

框图:

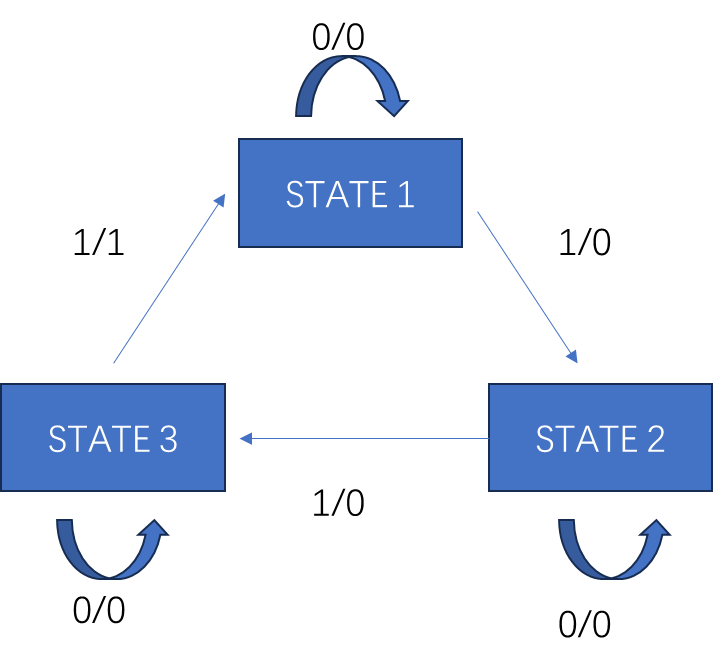

状态转移图:

输入:投入一元硬币

输出:出可乐,不出可乐

状态:投入0元,投入1元,投入2元,投入3元

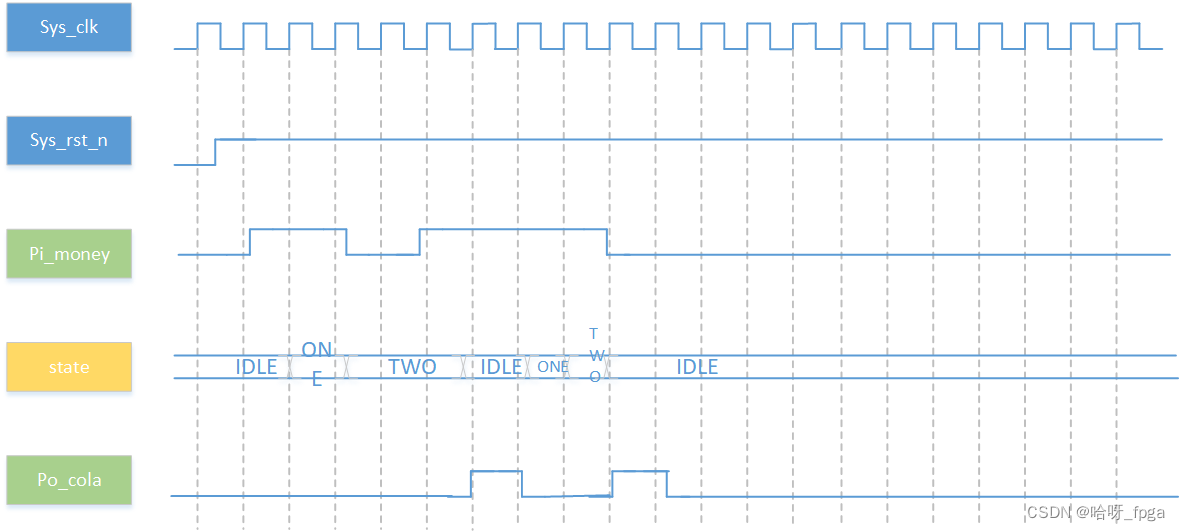

波形图:

四 代码

module simple_fsm

(

input wire sys_clk,

input wire sys_rst_n,

input wire pi_money,

output wire po_cola

);

parameter IDLE = 3'b001;

parameter ONE = 3'b010;

parameter TWO = 3'b100;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)//异步复位。

state <= IDLE;//初始状态。

else case(state)

IDLE: if(pi_money == 1'b1)

state <= ONE;//状态变化。

else

state <= IDLE;//状态保持。

ONE: if(pi_money == 1'b1)

state <= TWO;

else

state <= ONE;

TWO: if(pi_money == 1'b1)

state <= IDLE;

else

state <= ONE;

default: state <= IDLE;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n==1'b0)//异步复位。

po_cola <= 1'b0;//赋初值。

else if((state ==TWO)&& (pi_money == 1'b1))

po_cola <= 1'b1;//高电平有效。

else

po_cola <= 1'b0;//取低电平。

endmodule

1962

1962

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?