一些数字设计及验证的笔试题汇总,仅供参考。

目录

(2)SystemVerilog中,从一个类派生一个新类的关键字是什么?

(3)在SystemVerilog中,仿真器运行一个用例时需要建立多个子线程。这些子线程结束时间各不相同,此时需要使用什么语句来等待所有的线程结束?

(5)在SystemVerilog中,使用随机函数产生随机数并赋值给信号a[11:0],随机范围为3~255。命令是什么?

(6)SystemVerilog创建一个数据类型为int的动态数组a的命令是什么?

(7)SystemVerilog创建一个数据类型为int的队列b的命令是什么?

(8)SystemVerilog中,如何在int类型的队列queue的后面插入数据data?

(9)SystemVerilog中,rand int src;constrain c_dist{0 :=40, [1:2] :=60};}。此时0,1,2的权重分别是多少?

(10)在SystemVerilog中,rand bit[5:0]; constraint c_data {data inside {[$:5},[30:$]},那么变量data的取值范围是什么?

2、请描述对disable fork以及wait fork的理解。利用fork线程,请编码示意如何实现timeout的检查。

3、请简要描述TLM中analysis_port和analysis_fifo。

4、请简述UVM RAL model的使用机制,同时解释一下adapter具体做了哪些操作,并简述对predictor的理解。

1、问答题

(1)验证中,代码覆盖率是指什么?

代码覆盖率是指衡量哪些设计代码在激活触发,而哪一些则一直处于非激活状态的统计数据。

(2)SystemVerilog中,从一个类派生一个新类的关键字是什么?

extends。

(3)在SystemVerilog中,仿真器运行一个用例时需要建立多个子线程。这些子线程结束时间各不相同,此时需要使用什么语句来等待所有的线程结束?

wait fork。

(4)在SystemVerilog中,定义int_data[ ] = {9,1,8,3,4,4}。在执行data.reverse()操作后,data[]的值应该是什么?执行data.rsort()操作后,data[]的值应该是什么?

执行data.reverse() 操作后,data[]的值应该是({4,4,3,8,1,9})。

执行data.rsort() 操作后,data[]的值应该是({9,8,4,4,3,1})。

(5)在SystemVerilog中,使用随机函数产生随机数并赋值给信号a[11:0],随机范围为3~255。命令是什么?

$urandom_range(3,255)。

(6)SystemVerilog创建一个数据类型为int的动态数组a的命令是什么?

int a[]。

(7)SystemVerilog创建一个数据类型为int的队列b的命令是什么?

int b[$]。

(8)SystemVerilog中,如何在int类型的队列queue的后面插入数据data?

{queue, data}。

(9)SystemVerilog中,rand int src;constrain c_dist{0 :=40, [1:2] :=60};}。此时0,1,2的权重分别是多少?

40, 60, 60。

(10)在SystemVerilog中,rand bit[5:0]; constraint c_data {data inside {[$:5},[30:$]},那么变量data的取值范围是什么?

{[0:5], [30:63]}。

2、请描述对disable fork以及wait fork的理解。利用fork线程,请编码示意如何实现timeout的检查。

fork...join_any和fork...join_none继续执行后,其一些未完成的子程序仍将在后台运行。如果要等待这些子程序全部完成,或者停止这些子程序,可以使用wait fork或者disable fork。

fork

thread1();

begin

#timeout;

disable fork;

end

join_any3、请简要描述TLM中analysis_port和analysis_fifo。

analysis_port是一种TLM端口,可以实现一对多的连接,monitor往往会使用analysis port将其数据写出到其它的subscriber组件,例如scoreboard,coverage collector等。

analysis_fifo本身是一种TLM FIFO缓存,它继承于uvm_tlm_fifo,在具备已有TLM端口的同时还具备了analysis imp,它可以用来与另外一端组件(例如monitor)的analysis fifo完成TLM端口的连接,继而从initiator端接收数据并加以缓存。

4、请简述UVM RAL model的使用机制,同时解释一下adapter具体做了哪些操作,并简述对predictor的理解。

寄存器模型(RAL model)是硬件寄存器模块在UVM一侧构建的模型。其内部的寄存器信息包括所有的域信息(field)、地址信息(address map)、可读写方式、复位值与硬件一侧都是一一对应的。

寄存器模型可以在更高的抽象级用来对寄存器进行访问,继而提高寄存器访问的可读性和可维护性,同时由于其提供的后门访问方式,也可以加速寄存器的配置和访问。

寄存器模型本身也可以用来实现对寄存器测试的自动化,继而提高寄存器测试的效率。

adapter在寄存器访问中完成了抽象级transaction转换的任务,即其内部的reg2bus()和bus2reg()任务,继而实现了两种不同抽象级访问事务之间的桥接。

predictor的预测任务需要其它几个组件的参与,包括uvm_reg_map,bus monitor和adapter。其原理是利用monitor analysis port收集到的bus transaction,利用adapter::bus2reg()完成类型转换,继而利用uvm_reg_map更新对应的uvm_reg的镜像值(mirror value),完成寄存器值的预测,便于后期的便捷访问和寄存器值比较。

5、判断电路是否存在竞争冒险的方法有哪些?

A. 代数法

B. 卡诺图法

C. 实验法

D. 观察法

答案:ABCD

A选项,代数法在逻辑函数表达式中,若某个变量同时以原变量和反变量两种形式出现,就具备了竞争条件。如果表达式为 F=A+A~,就会产生0型冒险(F应该为1而实际却为0);如果表达式为 F=AA~,就会产生1型冒险。例如,表达式 F=AB+CB~,当A=C=1时,F=B+B~,在B发生跳变时,可能出现0型冒险。

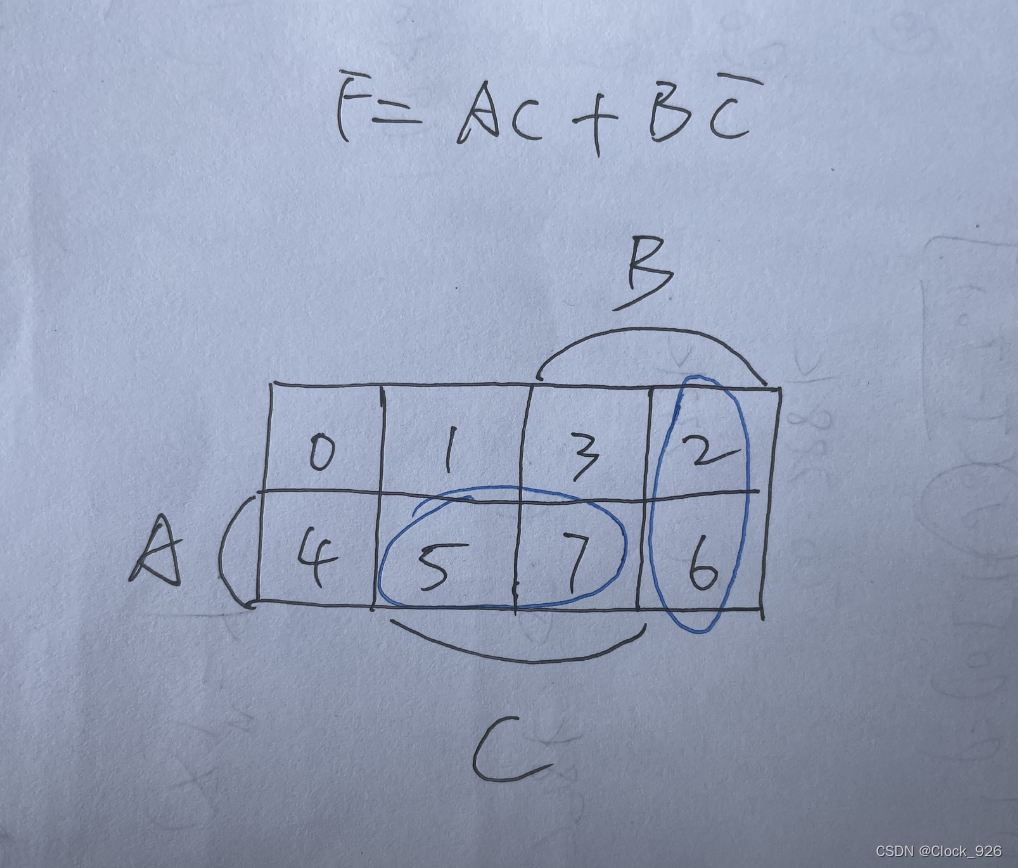

B选项,通过画出卡诺图也可以确定竞争冒险。如果两个卡诺圈相切,则函数在相切处两值间跳变时会发生逻辑冒险(前提是这两个卡诺圈没有被其他卡诺圈包围)。下图是一个简单例子。

D选项,没太理解这个观察到底是观察什么,不过观察肯定是可以判断的,干啥不得观察。

6、关于数字通信的特点,下面描述正确的是?

A. 抗干扰能力强,且噪声不积累

B. 易于保密,保密性好

C. 比模拟通信占据更窄的系统频带,系统设备简单,对同步要求更低

D. 易于集成,使通信设备微型化

答案:ABD

C选项错误,模拟通信才具有更窄的频带。

7、以下关于Latch与Flip_flop特性描述正确的是?

A. Latch与Flip_flop,都属于时序逻辑

B. Flip_flop只会在时钟触发沿采样当前输入,产生输出

C. Latch无时钟输入

D. Latch输出可能产生毛刺

答案:ABD

锁存器(latch)和触发器(flip-flop)的概念。

这篇文章汇总了一些数字设计验证的笔试题目,涉及SystemVerilog的关键概念,如类的继承、线程管理、数组操作、随机数生成、TLM中的analysis_port和analysis_fifo、UVMRALmodel的使用以及adapter的作用。同时,还探讨了如何检查竞争冒险和数字通信的特点。

这篇文章汇总了一些数字设计验证的笔试题目,涉及SystemVerilog的关键概念,如类的继承、线程管理、数组操作、随机数生成、TLM中的analysis_port和analysis_fifo、UVMRALmodel的使用以及adapter的作用。同时,还探讨了如何检查竞争冒险和数字通信的特点。

2302

2302

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?