一、概论

1.1存储器分类

1.按存储介质分类(注意易失性)

(1)半导体存储器 TTL晶体管、MOS管、主存、cache 易失

(2)磁表面存储器 磁头、载磁体 非易失

(3)磁芯存储器 硬磁材料、环状元件 非易失

(4)光盘存储器 激光、磁光材料 非易失

2.按信息的可保存性

易失性存储器:通电的时候01保存,断电即丢失——主存,cache

非易失性存储器:断电后存储信息依然保持——磁盘,光盘

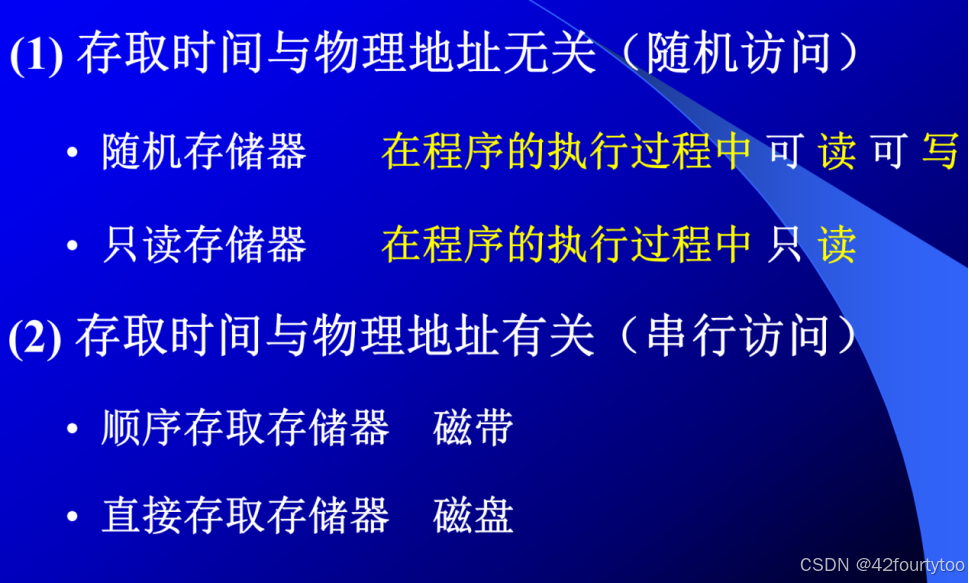

3.按存取方式分类

(随机访问)

(1)随机存取存储器RAM读写任何一个存储单元的用时都是相同的,与存取单元所在的物理位置无关

随机存储器 在程序的执行过程中可读可写

只读存储器 在程序的执行过程中只读

(串行访问)

(2)顺序存储存储器SAM读写一个存储单元所需时间取决于该存储单元的物理位置 磁带

(3)直接存取存储器DAM 磁盘

先直接选取信息所在区域,再按顺序存取。速度介于随机存取存储器和顺序存储存储器之间

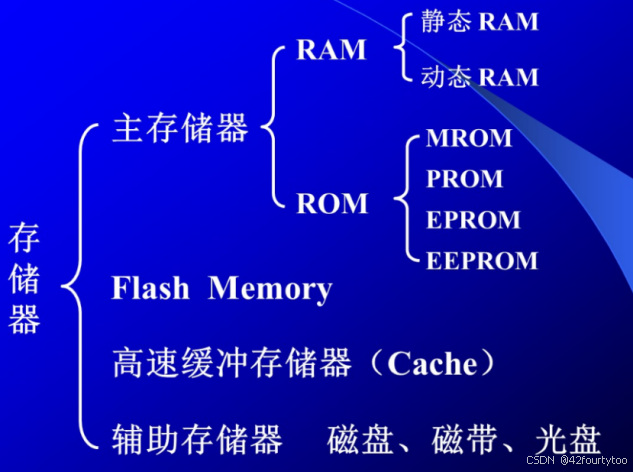

4.按在计算机中的作用分类

1.2存储器的层次结构

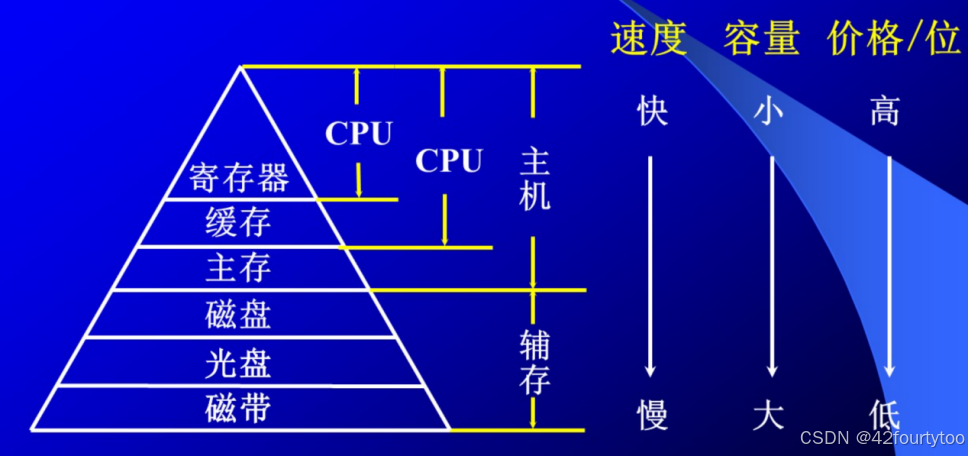

1.存储器三个主要特性的关系

CPU中也有缓存

存储器三个主要指标:速度、容量、价格。速度越快价格越高;容量越大,价格越低,速度也更慢。

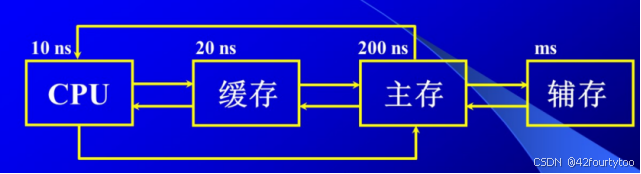

2.缓存——主存层次和主存——辅存层次

CPU和缓存、主存能交换信息;缓存和CPU、主存能交换信息;主存和CPU、缓存、辅存能交换信息。

缓存-主存层次解决了CPU和主存间的速度差异问题。由于缓存速度比主存快,只要将CPU近期要用的信息调入缓存,CPU便可以直接从缓存中获取信息,提高访存速度。但缓存容量小,需要不断的将主存内容调入,这一过程是硬件实现的,对程序员透明。

主存—辅存层次解决了主存容量不够的问题。辅存的速度低于主存,但容量比主存大得多,存储着暂时未用到的信息。当CPU需要使用这些信息时,再调入主存,供CPU直接访问。这一过程由硬件和操作系统共同实现。

辅存中的数据要调入主存中才能被CPU访问

没保存的时候,数据存在主存里(比如ctrl c)是易失的

二、主存储器

2.1概述

1.主存的基本组成

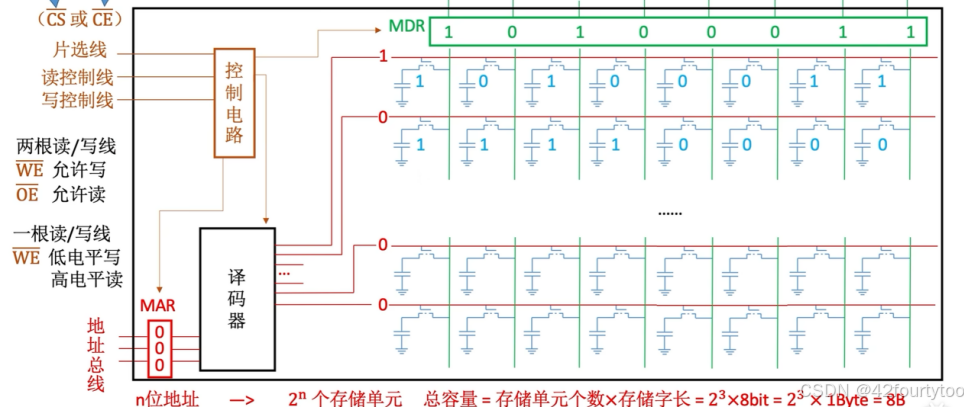

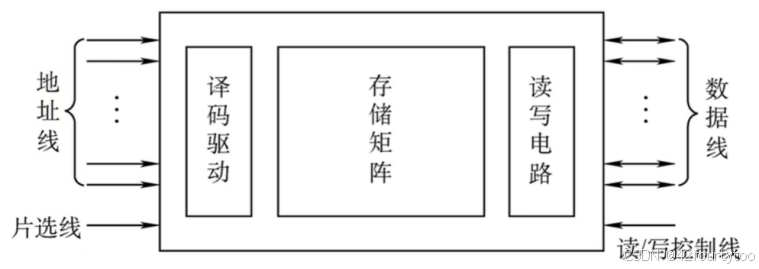

以下是对一个主存存储芯片的抽象(主存使用DRAM,所以图中为栅极电容)

控制电路的意义:当地址线中的信号稳定后才能送入译码器。

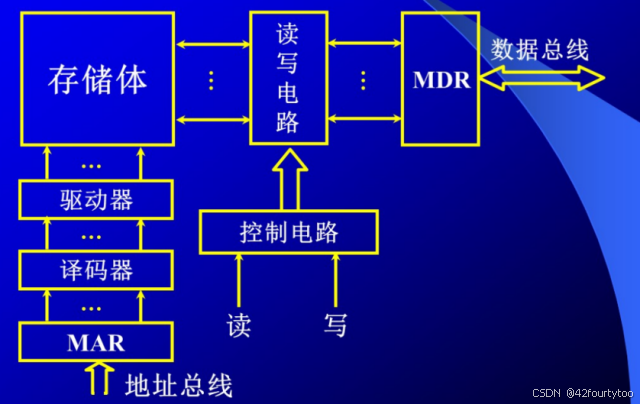

MAR经过译码驱动才能找到要访问的单元;存储体经过读写电路才能和MDR交互

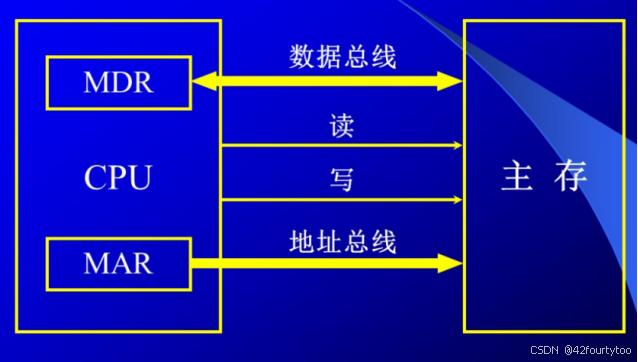

2.主存和CPU的联系

译码驱动器和读写电路制作在主存中,而MAR和MDR制作在CPU芯片内

3.主存中存储单元地址的分配

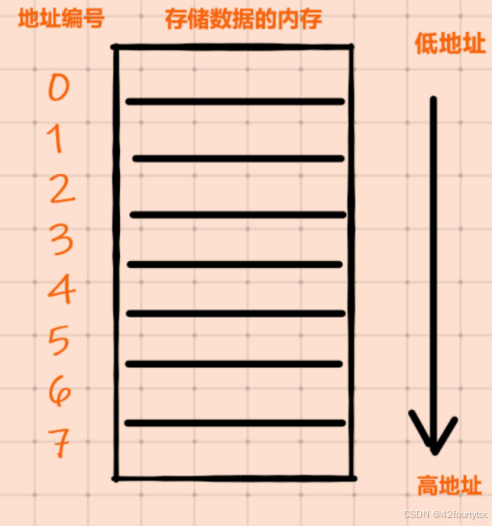

地址:地址编号小的是低地址,地址编号大的是高地址

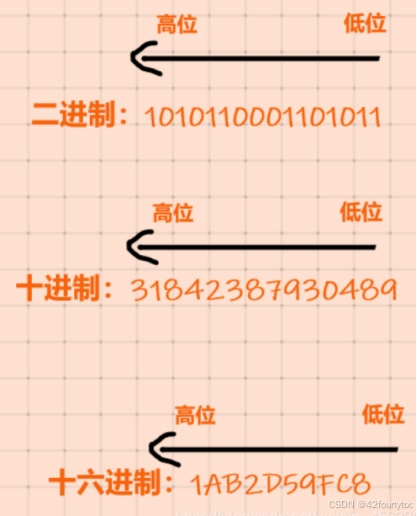

数据:靠右的是低位,靠左的是高位

小端存储:低位对应低地址,高位对应高地址

大端存储:高位字节存在低地址,低位字节存在高地址(字节越靠左位越高)

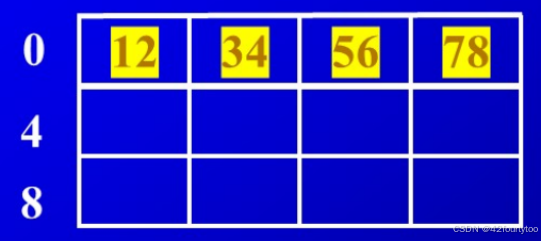

例:12345678H 的存储

假定每个字含4个字节,其中编号高的字节为高位字节;2整个字的地址用最低地址表示

12345678H是一个字(一行一个字),两个数字是一个字节

大端存储:

小端存储:

注意:每个存储单元内部不需要调换顺序

设地址线 24 根 按字节寻址 2^24=16M

若字长为 16 位 按字寻址 8MW,字长增加一倍,行数减少一半

若字长为 32 位 按字寻址 4MW

4.主存的技术指标

(1)存储容量

主存存放二进制代码的总位数,存储字数*字长,如(1M*8位)

(2)存储速度

存取时间 又称为存储器的访问时间,指启动一次存储器操作到完成该操作所需的全部时间;分为读出时间、写入时间

存取周期 连续两次独立的存储器操作(读或写)所需的最小间隔时间。读/写的平均值,因为写一般较慢。

存取周期大于存取时间,因为存取后还有恢复时间

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?