本篇博客,博主将总结FPGA时钟方面的问题。以前碰到过一些时钟的问题,但是由于没记录也就都忘记了,所以这篇文章将用来记录FPGA中时钟的问题。这篇文章属于持续更新的系列,将总结接下来时钟的注意点。

FPGA时序问题主要就是体现在时钟上面,虽然可以设置IO Delay,但是我还是喜欢使用PLL来调节相位。该方法虽然不好,但是非常简单。

有一些时钟的输出没有接到专用时钟引脚,可以使用OSERDESE2 原语来串行输出0、1信号增强时钟的质量。

Xilinx 7系列FPGA专用时钟引脚标志

相信许多同学们都知道FPGA内部的全局时钟网络质量特别高,时钟偏移、到达不同寄存器的时钟延迟比较小。进入全局时钟网络有几种方法:

1、经过专用时钟引脚引入的时钟

2、PLL输出的时钟

3、经过BUFG输出的时钟

写的不全,但是以后会继续补充。

那么如何判断FPGA的时钟引脚是专用时钟引脚呢?

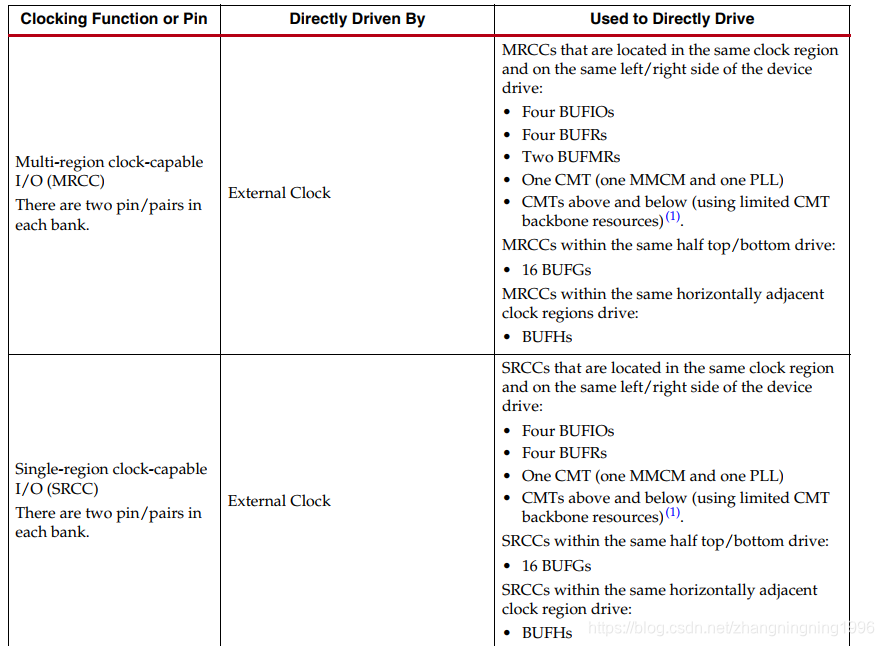

对于7系列的FPGA专用时钟引脚主要会标志上:SRCC、MRCC

UG472中的内容如下:

我们只要看见FPGA的引脚上面带有MRCC与SRCC,那么便证明这个引脚是FPGA专用时钟引脚。

Quartus II将普通引脚引用的时钟连接到全局时钟网络

有时候一些芯片的时钟引入到FPGA的普通引脚,但是扇出系数比较大,那么我们便需要将该引脚引入到FPGA的全局时钟网络。所以我们将使用IP ALTCLKCTRL,如下图:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4340

4340

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?