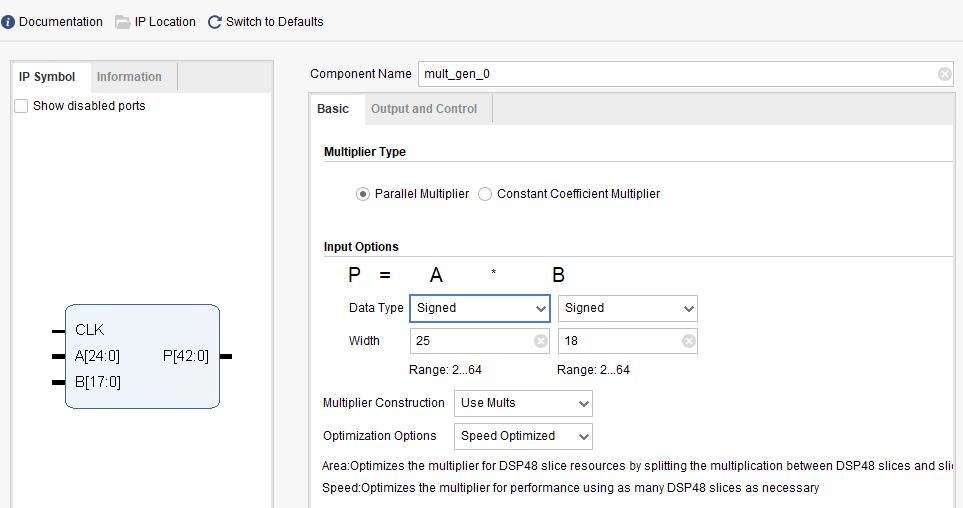

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

当然,我们也可以直接使用*符合来进行乘法,对于无符号的乘法

reg [7:0] ubyte_a;

reg [7:0] ubyte_b;

(* use_dsp48="yes" *)

output reg[15:0] u_res;

always @ ( posedge clk ) begin

if(rst)

u_res <= 'b0;

else

u_res <= ubyte_a * ubyte_b;

end

有符号乘法可以在Verilog中使用signed来标注。

reg signed [7:0] byte_a;

reg signed [7:0] byte_b;

(* use_dsp48="yes" *)

reg signed [15:0] res;

always @ ( posedge clk ) begin

if(rst)

res <= 'b0;

else

res <= byte_a * byte_b;

end

当然我们也要理解有符号数乘法的原理,其实就是扩位乘法,把高位都补充为符号位。

有符号

本文探讨了FPGA中乘法器作为稀缺资源的重要性,特别是在算法实现中的作用。详细介绍了通过IPCore或原语进行乘法操作的方法,包括无符号和有符号数的乘法,并解释了有符号乘法的扩位原理。文章还讨论了乘法结果位宽的问题,尤其是在处理有符号数时如何避免不必要的位宽。

本文探讨了FPGA中乘法器作为稀缺资源的重要性,特别是在算法实现中的作用。详细介绍了通过IPCore或原语进行乘法操作的方法,包括无符号和有符号数的乘法,并解释了有符号乘法的扩位原理。文章还讨论了乘法结果位宽的问题,尤其是在处理有符号数时如何避免不必要的位宽。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

548

548

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?