DMA Engine API Guide — The Linux Kernel documentation

在嵌入式系统中,从需求的角度看内存,是非常简单的,可以总结为两大类:

1)CPU 有访问内存的需求,包括从内存中取指、从内存中取数据、向内存中写数据。相应的数据流为:

CPU<-------------->MMU(Optional)<----------->Memory

2)其它外部设备有访问内存的需求,包括从内存“读取”数据、向内存“写入”数据。这里的“读取”和“写入”加了引号,是因为在大部分情况下,设备不像 CPU 那样有智能,不具备直接访问内存的能力。总结来说,设备有三种途径访问内存:

a)由 CPU 从中中转,数据流如下(本质上是 CPU 访问内存):

Device<---------------->CPU<--------------------Memory

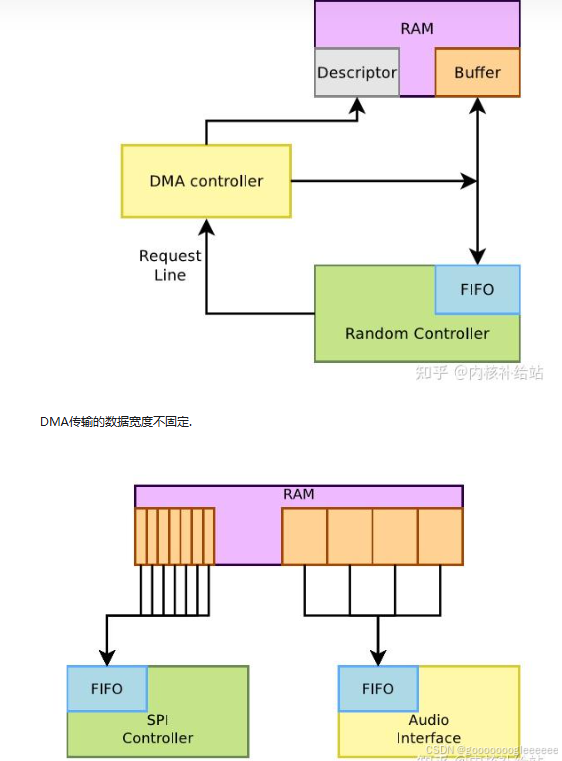

b)由第三方具有智能的模块(如 DMA 控制器)中转,数据流如下:

Device<----------->DMA Controller<--------->Memory

c)直接访问内存,数据流如下:

Device<---------->IOMMU(Optional)--------->Memory

DMA Engine

DMA Engine可以表示两个概念,第一,一个DMA Engine实际就是一个硬件DMA设备的驱动(DMA Engine Device)。第二,DMA Engine在内核中是一个DMA设备驱动的通用框架(DMA Engine Framework)。

DMA Engine Framework跟大多数内核设备框架一样,DMA Engine Driver需要根据其硬件特性填充dma device结构体,并基于其硬件实现功能接口,注册到DMA Engine框架,由DMA Engine Framework向外提供统一功能接口。

通常DMA的使用者包括三类人:

-

DMA Engine Developer,开发DMA设备驱动,向系统注册DMA Engine Device,为系统提供DMA的搬运服务,比如dw-axi-dma。

-

DMA Client Developer,比如UART、USB、UFS的driver开发者,调用DMA Engine Framework提供的通用DMA操作接口,帮助其完成DMA搬运服务。

-

DMA Mapping User,利用DMA Alloc时可以建立SMMU页表的功能,创建用于与其他子系统共享的内存Buffer。

本文主要介绍前两种情况。

DMA Engine Device

DMA硬件是一个可以脱离CPU,独立在Memory与IO Device间做数据搬运的设备。

CPU CPU Bus

Virtual Physical Address

Address Address Space

Space Space

+-------+ +------+ +------+

| | |MMIO | Offset | |

| | Virtual |Space | applied | |

C +-------+ --------> B +------+ ----------> +------+ A

| | mapping | | by host | |

+-----+ | | | | bridge | | +--------+

| | | | +------+ | | | |

| CPU | | | | RAM | | | | Device |

| | | | | | | | | |

+-----+ +-------+ +------+ +------+ +--------+

| | Virtual |Buffer| Mapping | |

X +-------+ --------> Y +------+ <---------- +------+ Z

| | mapping | RAM | by IOMMU

| | | |

| | | |

+-------+ +------+

如图所示,DMA设备所在的BUS上有两类设备,一类是IO设备,一类是主存(DDR),DMA设备只能看到自己所在的Bus Address(ba),访问IO设备,直接使用ba,访问DDR,可能会有一个offset转换或者经过iommu的转换。也就是说,CPU这边读写DDR,是通过VA,而DMA engine device访问DDR,使用的是ba,或者叫iova(translate ba=>pa)。内核中ba用dma_addr_t类型表示。

一个DMA硬件由多条Channel,Channel的数量由硬件决定,需要在DMA Device注册时填入到DMA Device结构体中。

DMA的搬运操作由DMA Request发起,DMA Request是一个软件虚拟概念,对应到硬件上,是一组寄存器配置操作。

DMA做搬运时,支持多种方向(direction):MEM_TO_DEV、DEV_TO_MEM、MEM_TO_MEM,具体硬件上支持哪个方向,也需要在DMA Device初始化时配入。

搬运时,硬件支持多种搬运模式(transaction_type or cap),以dw-axi-dmac为例,该DMA Device支持DMA_MEMCPY(从连续内存搬运)、DMA_SLAVE(使用scatter-gather list搬运非连续内存)、DMA_CYCLIC(搬运ringbuffer)三种搬运模式。这些硬件支持的搬运类型,在DMA Device初始化时,使用dma_cap_set来配置。(详细见provider.rst)

DMA支持的地址,不一定是64bit,所以在device注册时,需要指定src addr、dst addr的地址位宽(mask)。由于一般情况下DMA Device支持的物理地址位宽为32位,所以内核将DDR 32bit范围内的部分做成了一个DMA zone,用于给DMA设备分配可映射访问的buffer。

一次搬运操作支持的read或write字符数,叫做transfer width,但是一般DMA会支持将多次访问合并为一个burst(read、write operation collection),burst中支持合并多少个独立transfer操作,叫做burst的length,或者max_burst,同样在device初始化时需要定义。

DMA Engine Device除了需要填充上述硬件信息外,还需要实现DMA Device Operation:

device_tx_status # poll for transaction completion

device_issue_pending # push pending transactions to hardware (Do the transfer)

device_terminate_all # aborts all transfers on a channel

device_pause # pause any transfer on a channel

device_resume # resume paused transfer on a channel

device_alloc_chan_resources

device_free_chan_resources

device_synchronize

device_config

device_prep_dma_memcpy # get memcpy operation desc

device_prep_slave_sg # get slave operation desc

device_prep_dma_cyclic # get cyclic operation desc

最后通过 dmaenginem_async_device_register 注册到DMA Engine Framework中。

Reference: DMAengine controller documentation — The Linux Kernel documentation

Reference Code: dw-axi-dmac-platform.c

DMA Engine Client

DMA Engine Client是使用DMA Engine帮其从主存搬运数据的IO设备。这些设备包括支持dma的uart、pcie、usb、ufs、wifi(挂在pcie总线上)、modem(挂在pcie总线上)

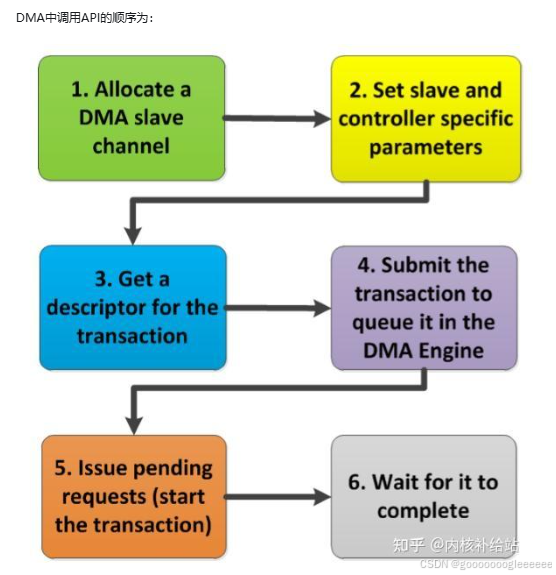

Slave Device Driver在使用DMA Engine做搬移时,一般包括下面几个步骤:

- Alloc a channel

通过调用 dma_request_chan 得到一个chanel结构体

- Config the channel for transfer

构造 dma_slave_config,通过 dmaengine_slave_config 配置chanel,设置搬运方向,原地址,地址位宽。

- Prepare the transaction descriptor (desc)

根据待传输的数据类型,调用 dmaengine_prep_xxx 接口,获得传输使用的 dma_async_tx_descriptor。

设置desc的callback信息。这时,desc中包含了所有transfer的信息,包括使用的channel(源地址)、目标地址、方向、大小、传输方式、callback等信息。

- Submit transaction

调用 dmaengine_submit 将获取并准备好的desc提交。

提交后的dma desc并不会直接开始传输,只是加入到pending队列。

- Issue pending requests

调用 dma_async_issue_pending 开始chanel request队列的异步传输。

- Wait and handle the callback event

当每个desc传输完成后,会通过tasklet回调callback。

Reference: DMA Engine API Guide — The Linux Kernel documentation

Reference Code: 8250_dma.c

Files

- /drivers/dma/dmaengine.c # dma engine framework implementation

- /include/linux/dmaengine.h # dma engine framework implementation

# also interfaces for both engine and client driver

- /drivers/tty/serial/8250/8250_dma.c # dma client device driver

- /drivers/dma/dw-axi-dmac/dw-axi-dmac-platform.c # dma engine device driver

Structure

struct dma_device

dma device,在注册前初始化,前面已经有描述

struct dma_chan

dma channel,指向所属的dma device,被使用的slave device。

每个channel还对应一个供sysfs使用的dma_chan_dev结构体,在sysfs中暴露节点。(channel本身也被注册为一个device)

struct dma_slave_config

供slave device配置chanel使用的config结构体,用来为传输配置channel。

Variable

dma_device_list

dma engine device全局链表

Functions

dma_bus_init

初始化unmap pool,debugfs节点,sysfs节点

Interface(for DMA Engine)

* Reference Driver: dw-axi-dma

dma_async_device_register

DMA Engine Device注册,会将device注册到全局device链表,并注册device的每个channel

Interface(for DMA Client)

* Reference Driver: 8250_dma

Request a channel

dma_request_chan

根据dts配置拿到对应dma设备的chanel,或动态分配一个channel(调用find_candidate找一个合适channel)

dma_request_slave_channel_compat

dma_release_channel

释放一个channel

Get channel’s device caps

dma_get_slave_caps

Config the channel

dmaengine_slave_config

Pause / Resume DMA transfer

dmaengine_pause

暂停channel传输

dmaengine_resume

恢复channel传输

Prepare dma transfer descripter

dmaengine_prep_dma_memcpy

dmaengine_prep_slave_single

dmaengine_prep_dma_cyclic

Submit the transfer

dmaengine_submit

提交传输desc到channel的pending队列,返回cookie(desc的传输句柄)

Issue pending request and wait for callback

dma_async_issue_pending

开始channel的队列传输。

Check transaction finish

dma_async_is_tx_complete

通过cookie来判断submit的desc传输有没有完成

Terminate all transfer

dmaengine_terminate_async

停止channel的所有传输,异步方式

dmaengine_terminate_sync

停止channel的所有传输,同步等待

dmaengine_synchronize

如果使用async接口停止传输,可以用这个接口进入等待

Debugfs

dmaengine/summary

打印出DMA设备列表,每个DMA设备的channel数,是否正在使用。

dmaengine/<dma_device>/

调用每个DMA设备自己的dump功能打印

Sysfs

/sys/devices/system/dma/<dma_device>

- memcpy_count

- bytes_transferred

- in_use:chanels in use

Reference

How to implement a dma engine device driver:

DMAengine controller documentation — The Linux Kernel documentation

How to use dma in dma client device driver:

DMA Engine API Guide — The Linux Kernel documentation

How to test dma client device with dmatest:

DMA Test Guide — The Linux Kernel documentation

// SPDX-License-Identifier: GPL-2.0

// Copyright (C) 2019 Spreadtrum Communications Inc.

#include <linux/dma-mapping.h>

#include <linux/dmaengine.h>

#include <linux/dma/sprd-dma.h>

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/of_reserved_mem.h>

#include <linux/platform_device.h>

#include <sound/pcm.h>

#include <sound/pcm_params.h>

#include <sound/soc.h>

#include "sprd-pcm-dma.h"

#define SPRD_PCM_DMA_LINKLIST_SIZE 64

#define SPRD_PCM_DMA_BRUST_LEN 640

struct sprd_pcm_dma_data {

struct dma_chan *chan;

struct dma_async_tx_descriptor *desc;

dma_cookie_t cookie;

dma_addr_t phys;

void *virt;

int pre_pointer;

};

struct sprd_pcm_dma_private {

struct snd_pcm_substream *substream;

struct sprd_pcm_dma_params *params;

struct sprd_pcm_dma_data data[SPRD_PCM_CHANNEL_MAX];

int hw_chan;

int dma_addr_offset;

};

static const struct snd_pcm_hardware sprd_pcm_hardware = {

.info = SNDRV_PCM_INFO_MMAP | SNDRV_PCM_INFO_MMAP_VALID |

SNDRV_PCM_INFO_INTERLEAVED | SNDRV_PCM_INFO_PAUSE |

SNDRV_PCM_INFO_RESUME | SNDRV_PCM_INFO_NO_PERIOD_WAKEUP,

.formats = SNDRV_PCM_FMTBIT_S16_LE | SNDRV_PCM_FMTBIT_S24_LE,

.period_bytes_min = 1,

.period_bytes_max = 64 * 1024,

.periods_min = 1,

.periods_max = PAGE_SIZE / SPRD_PCM_DMA_LINKLIST_SIZE,

.buffer_bytes_max = 64 * 1024,

};

static int sprd_pcm_open(struct snd_soc_component *component,

struct snd_pcm_substream *substream)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct device *dev = component->dev;

struct sprd_pcm_dma_private *dma_private;

int hw_chan = SPRD_PCM_CHANNEL_MAX;

int size, ret, i;

snd_soc_set_runtime_hwparams(substream, &sprd_pcm_hardware);

ret = snd_pcm_hw_constraint_step(runtime, 0,

SNDRV_PCM_HW_PARAM_PERIOD_BYTES,

SPRD_PCM_DMA_BRUST_LEN);

if (ret < 0)

return ret;

ret = snd_pcm_hw_constraint_step(runtime, 0,

SNDRV_PCM_HW_PARAM_BUFFER_BYTES,

SPRD_PCM_DMA_BRUST_LEN);

if (ret < 0)

return ret;

ret = snd_pcm_hw_constraint_integer(runtime,

SNDRV_PCM_HW_PARAM_PERIODS);

if (ret < 0)

return ret;

dma_private = devm_kzalloc(dev, sizeof(*dma_private), GFP_KERNEL);

if (!dma_private)

return -ENOMEM;

size = runtime->hw.periods_max * SPRD_PCM_DMA_LINKLIST_SIZE;

for (i = 0; i < hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

data->virt = dmam_alloc_coherent(dev, size, &data->phys,

GFP_KERNEL);

if (!data->virt) {

ret = -ENOMEM;

goto error;

}

}

dma_private->hw_chan = hw_chan;

runtime->private_data = dma_private;

dma_private->substream = substream;

return 0;

error:

for (i = 0; i < hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (data->virt)

dmam_free_coherent(dev, size, data->virt, data->phys);

}

devm_kfree(dev, dma_private);

return ret;

}

static int sprd_pcm_close(struct snd_soc_component *component,

struct snd_pcm_substream *substream)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct sprd_pcm_dma_private *dma_private = runtime->private_data;

struct device *dev = component->dev;

int size = runtime->hw.periods_max * SPRD_PCM_DMA_LINKLIST_SIZE;

int i;

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

dmam_free_coherent(dev, size, data->virt, data->phys);

}

devm_kfree(dev, dma_private);

return 0;

}

static void sprd_pcm_dma_complete(void *data)

{

struct sprd_pcm_dma_private *dma_private = data;

struct snd_pcm_substream *substream = dma_private->substream;

snd_pcm_period_elapsed(substream);

}

static void sprd_pcm_release_dma_channel(struct snd_pcm_substream *substream)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct sprd_pcm_dma_private *dma_private = runtime->private_data;

int i;

for (i = 0; i < SPRD_PCM_CHANNEL_MAX; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (data->chan) {

dma_release_channel(data->chan);

data->chan = NULL;

}

}

}

static int sprd_pcm_request_dma_channel(struct snd_soc_component *component,

struct snd_pcm_substream *substream,

int channels)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct sprd_pcm_dma_private *dma_private = runtime->private_data;

struct device *dev = component->dev;

struct sprd_pcm_dma_params *dma_params = dma_private->params;

int i;

if (channels > SPRD_PCM_CHANNEL_MAX) {

dev_err(dev, "invalid dma channel number:%d\n", channels);

return -EINVAL;

}

for (i = 0; i < channels; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

data->chan = dma_request_slave_channel(dev,

dma_params->chan_name[i]);

if (!data->chan) {

dev_err(dev, "failed to request dma channel:%s\n",

dma_params->chan_name[i]);

sprd_pcm_release_dma_channel(substream);

return -ENODEV;

}

}

return 0;

}

static int sprd_pcm_hw_params(struct snd_soc_component *component,

struct snd_pcm_substream *substream,

struct snd_pcm_hw_params *params)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct sprd_pcm_dma_private *dma_private = runtime->private_data;

struct snd_soc_pcm_runtime *rtd = snd_soc_substream_to_rtd(substream);

struct sprd_pcm_dma_params *dma_params;

size_t totsize = params_buffer_bytes(params);

size_t period = params_period_bytes(params);

int channels = params_channels(params);

int is_playback = substream->stream == SNDRV_PCM_STREAM_PLAYBACK;

struct scatterlist *sg;

unsigned long flags;

int ret, i, j, sg_num;

dma_params = snd_soc_dai_get_dma_data(snd_soc_rtd_to_cpu(rtd, 0), substream);

if (!dma_params) {

dev_warn(component->dev, "no dma parameters setting\n");

dma_private->params = NULL;

return 0;

}

if (!dma_private->params) {

dma_private->params = dma_params;

ret = sprd_pcm_request_dma_channel(component,

substream, channels);

if (ret)

return ret;

}

sg_num = totsize / period;

dma_private->dma_addr_offset = totsize / channels;

sg = devm_kcalloc(component->dev, sg_num, sizeof(*sg), GFP_KERNEL);

if (!sg) {

ret = -ENOMEM;

goto sg_err;

}

for (i = 0; i < channels; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

struct dma_chan *chan = data->chan;

struct dma_slave_config config = { };

struct sprd_dma_linklist link = { };

enum dma_transfer_direction dir;

struct scatterlist *sgt = sg;

config.src_maxburst = dma_params->fragment_len[i];

config.src_addr_width = dma_params->datawidth[i];

config.dst_addr_width = dma_params->datawidth[i];

if (is_playback) {

config.src_addr = runtime->dma_addr +

i * dma_private->dma_addr_offset;

config.dst_addr = dma_params->dev_phys[i];

dir = DMA_MEM_TO_DEV;

} else {

config.src_addr = dma_params->dev_phys[i];

config.dst_addr = runtime->dma_addr +

i * dma_private->dma_addr_offset;

dir = DMA_DEV_TO_MEM;

}

sg_init_table(sgt, sg_num);

for (j = 0; j < sg_num; j++, sgt++) {

u32 sg_len = period / channels;

sg_dma_len(sgt) = sg_len;

sg_dma_address(sgt) = runtime->dma_addr +

i * dma_private->dma_addr_offset + sg_len * j;

}

/*

* Configure the link-list address for the DMA engine link-list

* mode.

*/

link.virt_addr = (unsigned long)data->virt;

link.phy_addr = data->phys;

ret = dmaengine_slave_config(chan, &config);

if (ret) {

dev_err(component->dev,

"failed to set slave configuration: %d\n", ret);

goto config_err;

}

/*

* We configure the DMA request mode, interrupt mode, channel

* mode and channel trigger mode by the flags.

*/

flags = SPRD_DMA_FLAGS(SPRD_DMA_CHN_MODE_NONE, SPRD_DMA_NO_TRG,

SPRD_DMA_FRAG_REQ, SPRD_DMA_TRANS_INT);

data->desc = chan->device->device_prep_slave_sg(chan, sg,

sg_num, dir,

flags, &link);

if (!data->desc) {

dev_err(component->dev, "failed to prepare slave sg\n");

ret = -ENOMEM;

goto config_err;

}

if (!runtime->no_period_wakeup) {

data->desc->callback = sprd_pcm_dma_complete;

data->desc->callback_param = dma_private;

}

}

devm_kfree(component->dev, sg);

return 0;

config_err:

devm_kfree(component->dev, sg);

sg_err:

sprd_pcm_release_dma_channel(substream);

return ret;

}

static int sprd_pcm_hw_free(struct snd_soc_component *component,

struct snd_pcm_substream *substream)

{

sprd_pcm_release_dma_channel(substream);

return 0;

}

static int sprd_pcm_trigger(struct snd_soc_component *component,

struct snd_pcm_substream *substream, int cmd)

{

struct sprd_pcm_dma_private *dma_private =

substream->runtime->private_data;

int ret = 0, i;

switch (cmd) {

case SNDRV_PCM_TRIGGER_START: // >=start threohold后 ,数据足够pcm_write 才trigger 搬迁。

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (!data->desc)

continue;

data->cookie = dmaengine_submit(data->desc);

ret = dma_submit_error(data->cookie);

if (ret) {

dev_err(component->dev,

"failed to submit dma request: %d\n",

ret);

return ret;

}

dma_async_issue_pending(data->chan);

}

break;

case SNDRV_PCM_TRIGGER_RESUME:

case SNDRV_PCM_TRIGGER_PAUSE_RELEASE:

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (data->chan)

dmaengine_resume(data->chan);

}

break;

case SNDRV_PCM_TRIGGER_STOP:

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (data->chan)

dmaengine_terminate_async(data->chan);

}

break;

case SNDRV_PCM_TRIGGER_SUSPEND:

case SNDRV_PCM_TRIGGER_PAUSE_PUSH:

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (data->chan)

dmaengine_pause(data->chan);

}

break;

default:

ret = -EINVAL;

}

return ret;

}

static snd_pcm_uframes_t sprd_pcm_pointer(struct snd_soc_component *component,

struct snd_pcm_substream *substream)

{

struct snd_pcm_runtime *runtime = substream->runtime;

struct sprd_pcm_dma_private *dma_private = runtime->private_data;

int pointer[SPRD_PCM_CHANNEL_MAX];

int bytes_of_pointer = 0, sel_max = 0, i;

snd_pcm_uframes_t x;

struct dma_tx_state state;

enum dma_status status;

for (i = 0; i < dma_private->hw_chan; i++) {

struct sprd_pcm_dma_data *data = &dma_private->data[i];

if (!data->chan)

continue;

status = dmaengine_tx_status(data->chan, data->cookie, &state);

if (status == DMA_ERROR) {

dev_err(component->dev,

"failed to get dma channel %d status\n", i);

return 0;

}

/*

* We just get current transfer address from the DMA engine, so

* we need convert to current pointer.

*/

pointer[i] = state.residue - runtime->dma_addr -

i * dma_private->dma_addr_offset;

if (i == 0) {

bytes_of_pointer = pointer[i];

sel_max = pointer[i] < data->pre_pointer ? 1 : 0;

} else {

sel_max ^= pointer[i] < data->pre_pointer ? 1 : 0;

if (sel_max)

bytes_of_pointer =

max(pointer[i], pointer[i - 1]) << 1;

else

bytes_of_pointer =

min(pointer[i], pointer[i - 1]) << 1;

}

data->pre_pointer = pointer[i];

}

x = bytes_to_frames(runtime, bytes_of_pointer);

if (x == runtime->buffer_size)

x = 0;

return x;

}

static int sprd_pcm_new(struct snd_soc_component *component,

struct snd_soc_pcm_runtime *rtd)

{

struct snd_card *card = rtd->card->snd_card;

struct snd_pcm *pcm = rtd->pcm;

int ret;

ret = dma_coerce_mask_and_coherent(card->dev, DMA_BIT_MASK(32));

if (ret)

return ret;

return snd_pcm_set_fixed_buffer_all(pcm, SNDRV_DMA_TYPE_DEV,

card->dev,

sprd_pcm_hardware.buffer_bytes_max);

}

static const struct snd_soc_component_driver sprd_soc_component = {

.name = DRV_NAME,

.open = sprd_pcm_open,

.close = sprd_pcm_close,

.hw_params = sprd_pcm_hw_params,

.hw_free = sprd_pcm_hw_free,

.trigger = sprd_pcm_trigger,

.pointer = sprd_pcm_pointer,

.pcm_construct = sprd_pcm_new,

.compress_ops = &sprd_platform_compress_ops,

};

static int sprd_soc_platform_probe(struct platform_device *pdev)

{

struct device_node *np = pdev->dev.of_node;

int ret;

ret = of_reserved_mem_device_init_by_idx(&pdev->dev, np, 0);

if (ret)

dev_warn(&pdev->dev,

"no reserved DMA memory for audio platform device\n");

ret = devm_snd_soc_register_component(&pdev->dev, &sprd_soc_component,

NULL, 0);

if (ret)

dev_err(&pdev->dev, "could not register platform:%d\n", ret);

return ret;

}

static const struct of_device_id sprd_pcm_of_match[] = {

{ .compatible = "sprd,pcm-platform", },

{ },

};

MODULE_DEVICE_TABLE(of, sprd_pcm_of_match);

static struct platform_driver sprd_pcm_driver = {

.driver = {

.name = "sprd-pcm-audio",

.of_match_table = sprd_pcm_of_match,

},

.probe = sprd_soc_platform_probe,

};

module_platform_driver(sprd_pcm_driver);

MODULE_DESCRIPTION("Spreadtrum ASoC PCM DMA");

MODULE_LICENSE("GPL v2");

MODULE_ALIAS("platform:sprd-audio");

3134

3134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?