目录

Flash器件特性

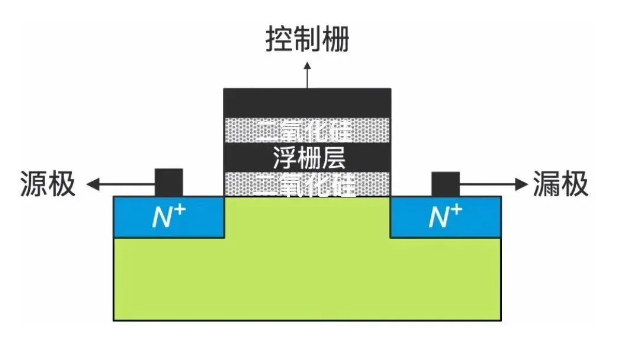

Flash 分为 NAND flash和 NOR flash。均是使用浮栅场效应管作为基本存储单元来存储数据的,浮栅MOS与普通的MOS管区别在于加了⼀个浮栅层,浮栅场效应管共有4个端电极,分别是源、漏、控制栅和浮栅,如下图所示:

浮栅层与硅衬底之间有二氧化硅绝缘层,用来保护浮栅层中的电荷不会泄漏。采用这种结构,使得存储单元具有了电荷保持能力,其中与沟道接近的绝缘层二氧化硅厚度比较薄,电子在比较大的电场作用下,会隧穿进入浮栅层。

Flash存储原理

在浮栅晶体管的设计中,浮栅层可以存储电⼦,Flash读取并⾮以读取浮栅电平为基准,因为浮栅外接导线必然导致电⼦流失,所以读取是通过另⼀种⽅式,判断MOS管是否导通。

如果浮栅存储了电⼦,当在控制栅极施加正电压时,浮栅电⼦与衬底有⼀个负电场,会削弱导通电压,这样晶体管导通需要在控制栅极上放置更高的电压。如果浮栅没有电⼦,MOS管控制栅电压没有被削弱,导通电压正常。

当浮栅中没有电子时,控制栅的电压能直接作用于沟道,使其导通,此时输出为“1”;反之,浮栅有电子时,阈值电压升高导致沟道无法导通,输出为“0”。 导通状态(电流可通过)通常映射为逻辑“1”,而关断状态(电流无法通过)映射为逻辑“0”。

Read

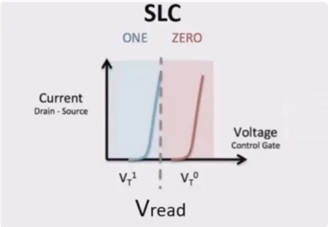

假如在浮栅层上没有电子时,控制栅极施加电压 Vt1 时导通,在浮栅层放置电子后,控制栅极施加电压Vt0导通,满足Vt0 > Vt1。为了读出cell的值,在控制栅极施加一个电压V(Vread),要求Vt1 < V <Vt0。如果晶体管导通,源极和漏极间能读到电流,浮栅层上肯定没有电子,即逻辑 1 。如果晶体管不导通,源极和漏极间不能读到电流,浮栅层上肯定放置有电子,即逻辑 0 。

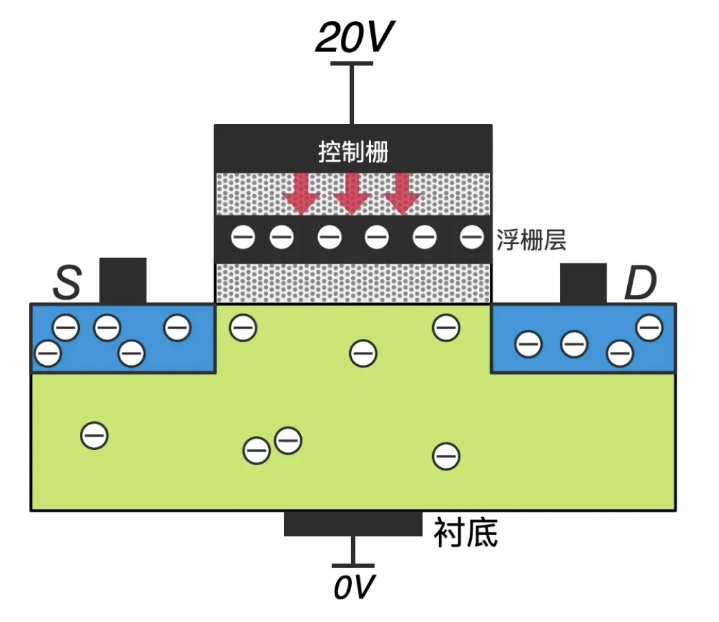

Program

在写入电子时,在控制栅极施加相对于衬底的高压时,离子阱的电子被吸引并隧穿进入浮栅层被存储在其中,如果撤销电压之后,因为浮栅层被绝缘层包裹,浮栅层电子还是存储在这个部位,此状态计为逻辑0。

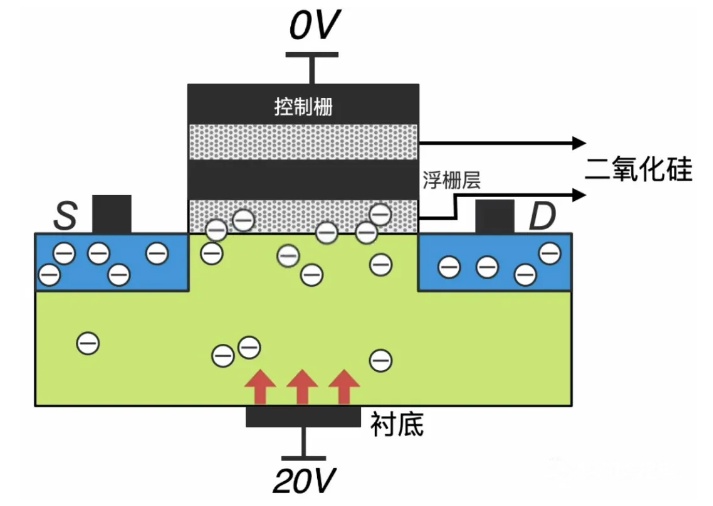

Erase

在擦除电子时,需要在衬底加一个相对于栅极的高压,浮栅层存储的电子就会在电场作用下隧穿回到下面的P型半导体里。此状态计为逻辑1。

过擦原理

擦除时异常掉电

flash擦除操作分为三个阶段:Pre-Program阶段(预编程)、Erase阶段(擦除阶段)和Recovery阶段(恢复阶段,也叫回编)。

- Pre-Program阶段:在这个阶段,Flash设备会进行一些预编程操作,为擦除操作做准备。

- Erase阶段:这是实际的擦除过程,将存储单元的浮栅内的电荷放掉,使存储单元的控制栅极开关阈值电平恢复到初始状态。

- Recovery阶段:在擦除完成后,设备会进行一些恢复操作,确保擦除过程的稳定性和可靠性。

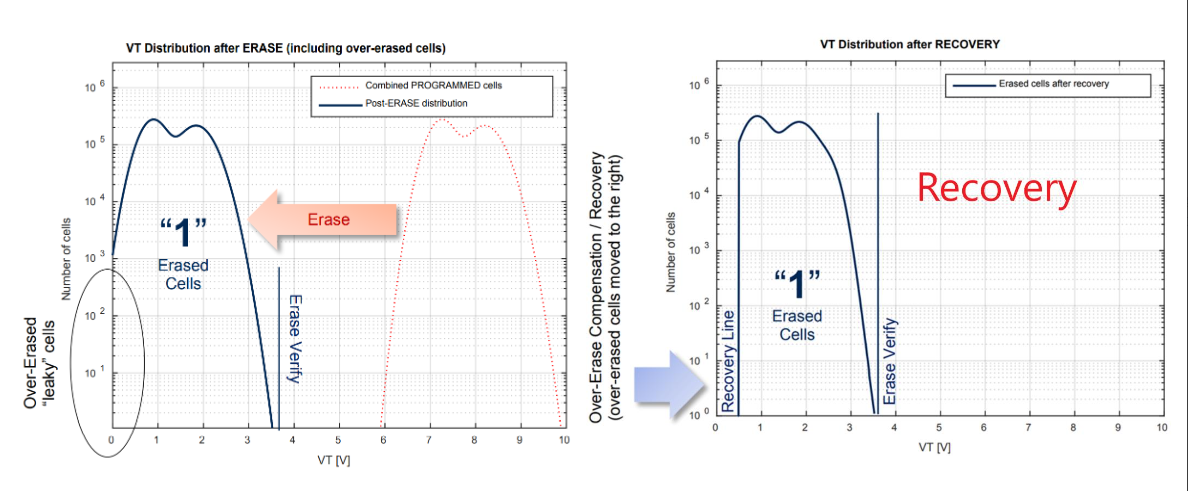

norflash的擦除操作是Erase和Recovery两个动作的循环,回编是为了保证擦除动作完成后没有过擦。通过每个bit物理点的充放电标记0和1,相对高电平阈值范围对应0,低电平阈值范围对应1,当擦除flash时,会先将所有的bit放电到一个低电压的基准值,随后通过回编将所有bit基本都重新拉到1的区域内,这样就实现了擦成全FF如下图所示:

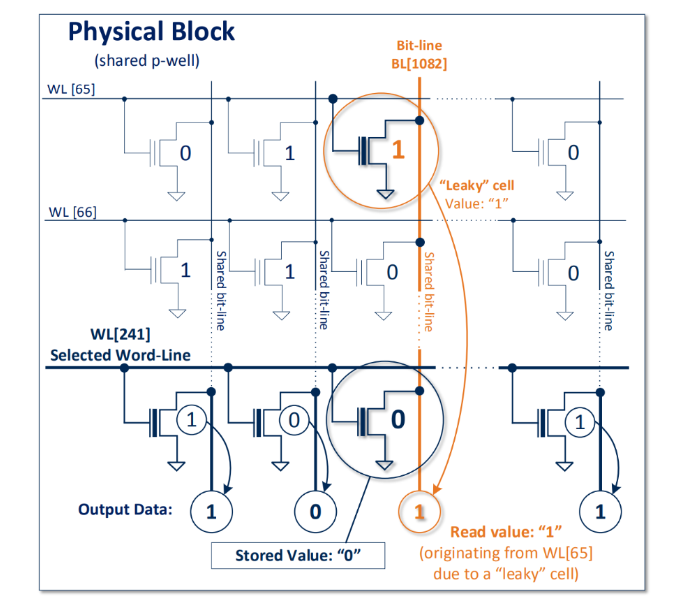

擦除阶段将所有bit擦到基准范围时,由于一些特殊原因,导致电压值低于这个基准范围,在后续的回编过程中,由于这些bit电压过低,会出现这些bit大部分都无法校准到1的电平范围,这将会导致同group的其他bit叠加一个过擦的漏电流,如果该电流大于1的读出判据,则该地址数据会被误判为1,引起邻区的bit由0到1的翻转。如下图所示:

改善方案: 消除过擦可以通过回编即对存在过擦的Group执行一次正常的编程来消除,软件上可以增加保护,应用增加补擦机制,每次擦除flash前记录下擦的地址,并做好标记,下次开机如果检测到标记地址未擦完,则开机时将这个flash做一次擦除。对于主动掉电的操作,增加掉电保护,掉电时有操作flash等待1s断电。

XIP导致flash过擦

原理介绍:

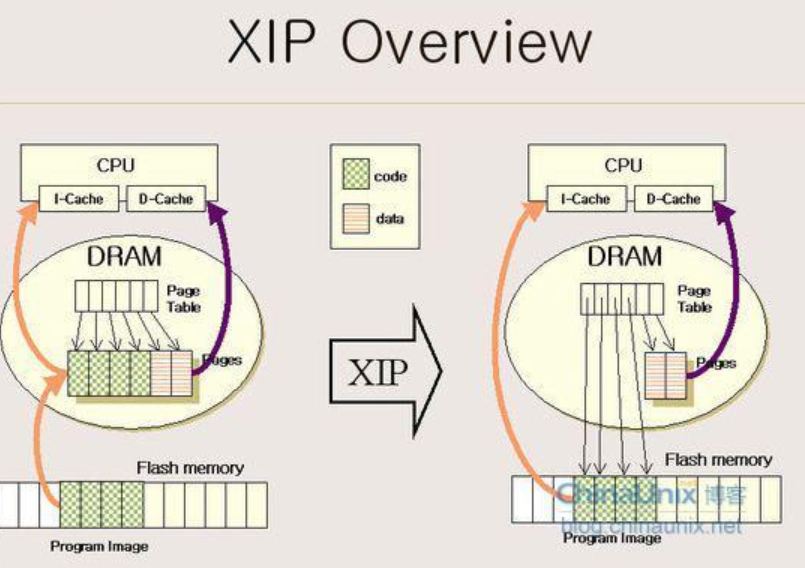

代码默认都是压缩存放在norflash里,在系统启动阶段解压拷贝到psram中运行。对于XIP运行的代码则是不压缩的,存储在norflash上直接运行的,这样可以有效的节约ram资源。

Norflash可以在芯片内执行,应用程序可以直接在flash闪存内执行,不必将代码读到ram上,CPU的主要功能是取指译码执行,norflash片内执行指的是CPU的取指模块能够直接从norflash上将指令读取出来,供后面的译码执行模块使用。

左边是非XIP方式代码执行流程,可以理解成是 Nand Flash,CPU 想要从 Nand Flash 中读取数据,必须要先通过在 RAM 中计算地址,各种时序计算,然后通过 MMU 转换地址,然后给 Nand flash 发送命令,注意是命令,不是地址, Nand Flash根据命令进行相应的操作,如果是读命令,则返回对应地址的数据到 RAM 中,如果是写命令,则进行写操作。

右边是XIP方式代码执行流程,是针对 Nor Flash 的,CPU 可以像读内存一样,直接跟 Norflash 交互,即可以直接从 Nor Flash 中取指令,然后交给译码模块和执行模块进行执行。

由于 xip 是片内执行,故需要执行 norflash 的读指令,xip机制允许flash在擦的过程中,去读flash,但是需要发送一个flash suspend指令,再读完flash后,再发一个flash resume指令恢复之前的擦写操作。由于resume到suspend之间时间过短会导致flash的过擦现象,如果此时正好读的是同一个bank的指令会导致死机,死机后擦的过程无法继续完成,导致bitflip。

tRS(Resume-to-Suspend Interval):指从发送擦除恢复(Erase Resume)命令到允许再次发送擦除挂起(Erase Suspend)命令之间的最小时间间隔。擦除恢复后,设备需要完成当前块的擦除操作。若过早发送挂起命令可能导致擦除流程中断,引发过擦。

tSUS(Suspend Latency):指发送擦除挂起(Erase Suspend)命令后,主机必须等待的最短时间才能继续发送其他指令,挂起操作涉及擦除进程的暂停和内部状态保存,期间设备可能处于"忙"状态,无法响应新命令。

改善方案:在resume flash时增加tick记录,tick值在下一次suspend时等待达到一定时间后才会进行suspend。模块发生死机后,如果检测到当前flash被suspend,则会resume一次让flash可以继续做完此次擦除操作,这样下一次开机可以保证bitflip被修复。

心灵鸡汤:不要等着被选,而是选择自己想要的,不要怕,只要是自己选择就好。那样人生才会快乐!

Flash过擦Bug原理及改善方案

Flash过擦Bug原理及改善方案

628

628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?