3.8多 SST操作

3.8.1 Multi-SST 架构概述

多 SST作 (MSO) 允许 eDP 源设备在单独的主链路通道上同时传输多个和单独的 SST 链路,而不是仅使用在多个通道之间划分的单个 SST 链路。这使得一个 Source 设备能够直接连接到单个显示模块中的多个面板段,每个面板段都有一个单独的 eDP Main-Link 接收器连接到每个面板段。面板仍将具有一个用于 AUX CH 的连接和一个用于 HPD 的连接

3.8.2 Multi-SST作源配置

除了 DP v1.3 第 2.1.4 节中描述的 SST 模式链路拓扑之外,eDP 还可以选择支持 MSO,其中源设备可以将单个 eDP 通道作为两个或四个单独的 SST 链路路由到接收设备。在 eDP 中,所有 SST 链路都连接到一个由一个 AUX 连接描述的 Sink 设备。

使用 MSO 的 eDP Sink 在两个单独的 Panel Segment 上显示两个图像,或在四个单独的 Panel Segment 上显示四个图像,包含在一个 Sink 设备中。此拓扑仅支持以下三种配置:

• 两个 SST 链路,每个链路一个通道(共两个通道),2x1(第 3.8.3 节)

• 两个 SST 链路,每个链路有两个通道(共四个通道),2x2(第 3.8.4 节)

• 四个 SST 链路,每个链路一个通道(共四个通道),4x1(第 3.8.5 节)

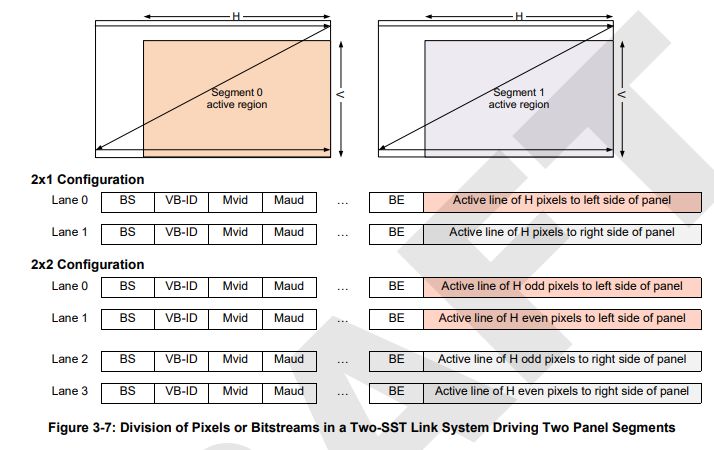

在每种配置中,每个 SST 链路的通道数通过使用标准 DP 方法确定源设备的像素或比特流映射,如下所示:

• 如果源设备使用每个 SST 链路一个通道通过 MSO 发送数据,则使用单通道映射

• 如果源设备使用每个 SST 链路两个通道通过 MSO 发送数据, 使用双车道映射

MSO_LINK_CAPABILITIES寄存器 (DPCD 地址 007A4h;参见 Section 3.8.7) 定义了特定于本节中确定的三种配置中的每一种的 DPCD 寄存器值。以下要求适用于这三种配置:

• Sink device 在 Source 设备中显示为一个面板。

• 源设备从 DisplayID (EDID) 配置中读取 Sink 设备的时序,作为一个 MSO SST Link 所需的时序(例如,具有两个面板段(每个面板段为 960x1080)的 Sink 设备将水平和垂直活动区域设置为等于 960x1080),如图 3-7 所示。

• 源设备通过读取一个 EDID 来发现所有 Panel Segments 的计时。一个 Sink 器件中的每个 Panel Segment 必须具有相同的 active area 和相同的消隐周期。

• 每个通道的 MSO 像素顺序与普通 SST 模式下相同(使用压缩比特流时,请参阅 DP v1.3,第 2.2.1.3 节,第 8.4 节)。

• 使用压缩时,源设备必须仅向每个 MSO 链路发送整数个切片和至少一个独立切片,如第 8.4 节所定义

• AUX 代理传达所有 AUX 信息,包括例如,链路训练和链路锁定。设备之间功能关联和协调的方法不属于本标准的范围。

• 源设备必须将 MSA 数据包复制到所有 SST 链路(请参阅 DP v1.3 的第 2.2.1.2 节)。

• 根据需要在每个链路上发送 SDP;但是,SDP 的内容不需要在每个链路上相同

当不存在歪斜时,视频消隐字段、MSA 字段和像素或比特流在所有 Lanes 中对齐。

3.8.3 多 SST操作,具有两个 SST 链路,每个链路一个通道 (2x1)

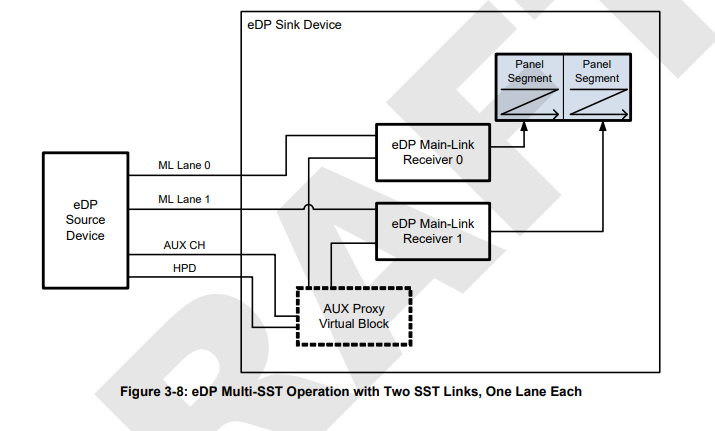

图 3-8 说明了包含两个 Panel Segment 的 Sink 设备,每个 Segment 连接到一个单通道 SST Link 接收器。以下要求适用于此配置:

• 源设备必须将左侧像素发送到映射到源设备通道 0 的 MSO 链路 • 源设备将右侧像素发送到映射到源设备通道 1 的 MSO 链路

• 源设备仅训练通道 0 和 1,没有额外的链路训练要求

3.8.4 多 SST操作,带两个 SST 链路,每个链路两个通道 (2x2)

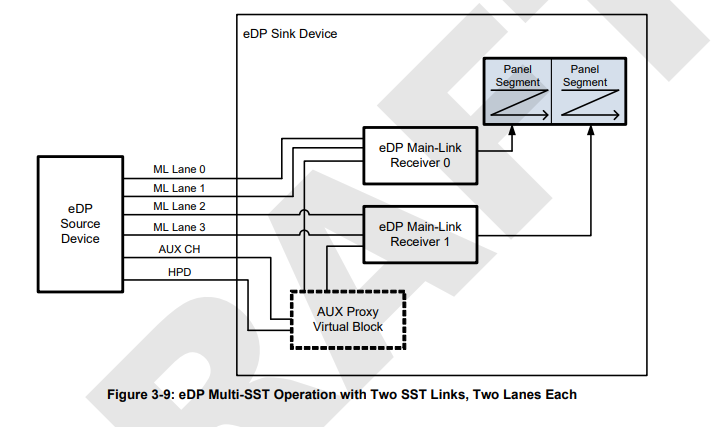

图 3-9 显示了包含两个 Panel Segment 的 Sink 设备,每个 Segment 连接到一个双通道 SST Link 接收器。以下要求适用于此配置:

• 源设备必须将左侧像素发送到映射到源设备通道 0 和 1 的 MSO 链路

• 源设备必须将右侧像素发送到映射到源设备的通道 2 和 3 的 MSO 链路

• 源设备训练通道 0、1、2 和 3,没有额外的链路培训要求.

3.8.5 多 SST操作,具有 4 个 SST 链路,每个链路 1 个通道 (4x1)

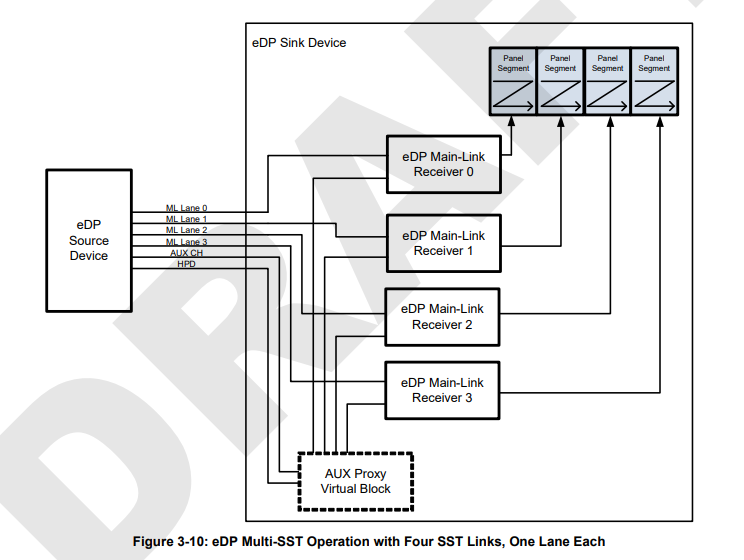

图 3-10 显示了一个包含四个 Panel Segment 的 Sink 设备,每个 Segment 连接到一个单通道 SST Link 接收器。以下要求适用于此配置:

• 源设备必须将最左侧的 1/4 像素行发送到映射到源设备的通道 0 的 MSO 链路

• 源设备必须将最左侧的第二行 1/4 像素发送到映射到源设备的通道 1 的 MSO 链路 • 源设备必须将最左侧的第三行 1/4 像素发送到映射到源设备的通道 2 的 MSO 链路

• 源设备必须将最右侧的 1/4 像素行发送到映射到源设备通道 3 的 MSO 链路 • 源设备训练通道 0、1、2 和 3,没有额外的链路训练要求

3.8.6像素重叠相邻面板段的多 SST作

像素重叠是一个实现选项,用于将一个或多个额外的像素值发送到相邻的 MSO 链接和面板段。像素值可以是未压缩的,也可以是压缩的。

请参阅 DisplayID v1.3 以查找定义 Sink 设备中支持的重叠像素数的寄存器。EDID 在活动区域时序信息中包含重叠像素。

使用压缩方法时,在每个 SST Link 上传输的切片必须独立于源设备正在使用的其他 SST Link 进行编码。

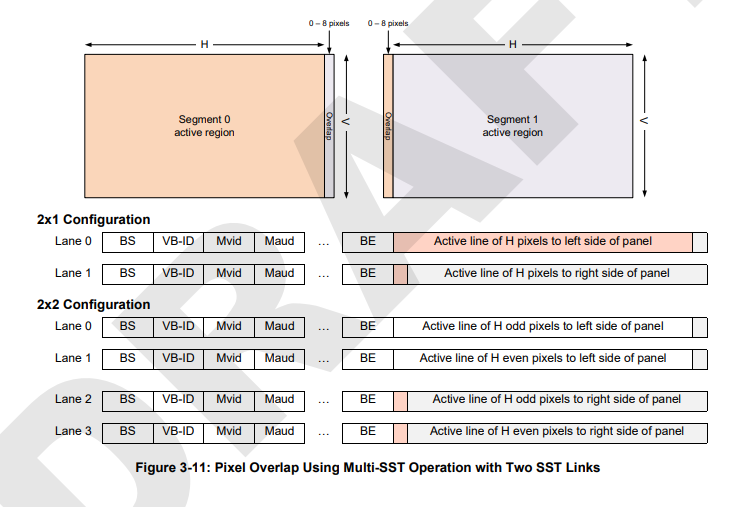

图 3-11 说明了在 MSO 2x1 或 2x2 配置中工作时与每个通道相关的数据。请注意所有 blanking 和 timing 字段在所有 lanes中是如何对齐的。重叠像素将添加到发送图像左半部分的 Link 的右边缘。同样,重叠像素也会添加到发送图像右半部分的 Link 的左边缘

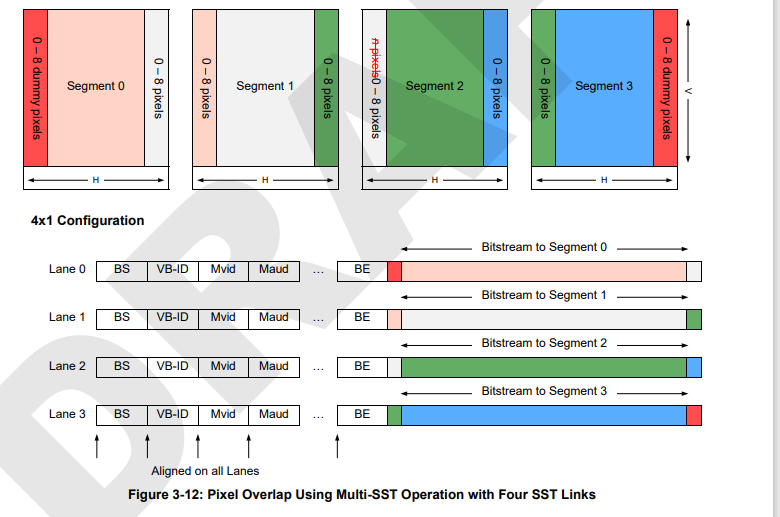

图 3-12 说明了在 MSO 4x1 配置中运行时与每个通道相关的数据。消隐和定时字段在所有通道中对齐,因为虚拟像素已包含在分配给通道 0 和 3 的 MSO 链接中。图 3-12 说明了以下要求:

• 映射到源设备通道 0 的 MSO 链路必须在活动区域的开头包含虚拟重叠像素,在活动区域的末尾包含重叠像素。

• 映射到源设备通道 1 的 MSO 链接必须在活动区域的开头和结尾包含重叠像素。

• 映射到源设备通道 2 的 MSO 链接必须在活动区域的开头和结尾包含重叠像素。

• 映射到源设备泳道 3 的 MSO 链接必须在活动区域的开头包含重叠像素,在活动区域的末尾包含虚拟重叠像素。

• 虚拟像素支持数据通道对齐,但对 Sink 设备没有意义。Sink 设备必须忽略虚拟像素,因为不包含栅格数据。如果 dumy pixels 包含在 bitstream中,则在解压缩后将忽略 dummy pixels

3.8.7 多 SST操作 DPCD 功能寄存器

为清楚起见,存储在 Sink device EDID 中的 timing 信息指定了每个 SST Link 的 timing 。

MSO 的 Link 配置遵循与 SST 模式相同的过程,但需要执行以下附加步骤:

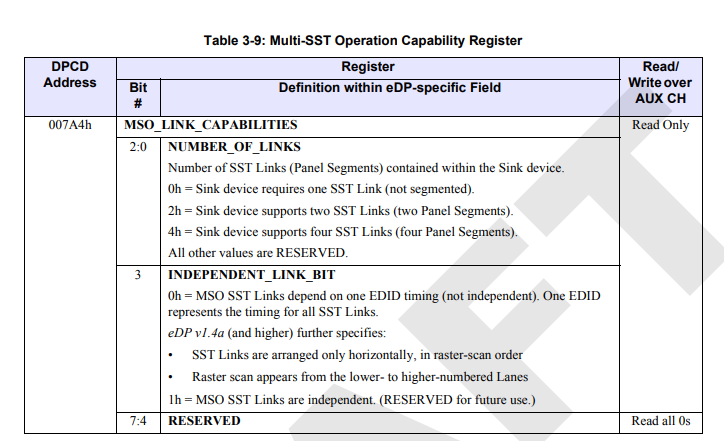

1 源器件读取 MSO_LINK_CAPABILITIES 寄存器中的 NUMBER_OF_LINKS 字段(DPCD 地址 007A4h,位 2:0)。如果字段的值为 2h 或 4h,则 Source device 将配置 MSO。

2 MAX_LANE_COUNT寄存器中的 MAX_LANE_COUNT 字段(DPCD 地址 00002h,位 4:0;参见 DP v1.3)和 MSO_LINK_CAPABILITIES 寄存器中的 NUMBER_OF_LINKS 字段的组合充分指定了源器件的通道选项,如下所示:a 如果 MAX_LANE_COUNT == 2h 且 NUMBER_OF_LINKS = 2h,则源器件限制为两个 MSO 链路, 每个 SST 链路 (2x1) 一个通道。LANE_COUNT_SET寄存器中的LANE_COUNT_SET字段(DPCD 地址 00101h,位 4:0;参见 DP v1.3)必须编程为 2h。

b 如果 MAX_LANE_COUNT == 4h 且 NUMBER_OF_LINKS = 4h,则源器件限制为四个 MSO 链路,每个链路一个通道 (4x1)。LANE_COUNT_SET寄存器中的LANE_COUNT_SET字段必须编程为 4h。

c 如果 MAX_LANE_COUNT == 4h 且 NUMBER_OF_LINKS = 2h,则源器件限制为两个 MSO 链路,每个 SST 链路有两个通道 (2x2)。LANE_COUNT_SET寄存器中的 LANE_COUNT_SET 字段必须编程为 4h。

d 这两种设置没有其他合法组合。

使用 MAX_LANE_COUNT 和 LANE_COUNT_SET 与 DP v1.3 相比没有变化。MSO_LINK_CAPABILITIES寄存器中的 INDEPENDENT_LINK_BIT 位 (DPCD 地址 007A4h,位 3) 限制为 0 值。MSO 依赖于一个 EDID 来分配给所有 MSO Link 的视频时序。此外,此标准还限制了像素顺序,其中所有 MSO Links 驱动程序像素都按水平对齐的光栅扫描顺序排列。保留对独立链接的任何其他使用

3.8.8 多 SST作时序要求(仅限相关多 SST作链路)

如果 Source 器件中的数据定位引入了时序偏移,则数据的未对齐不得超过当前正在传输的光栅的 Horizontal Blanking Offset 值

3.8.9 用于多 SST作的灌电流 CRC 寄存器

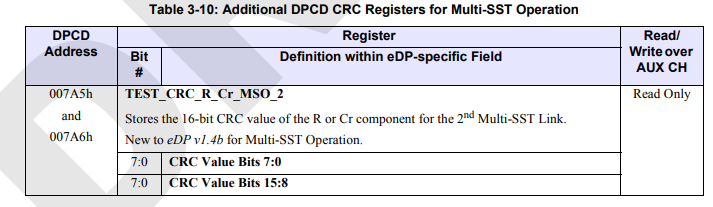

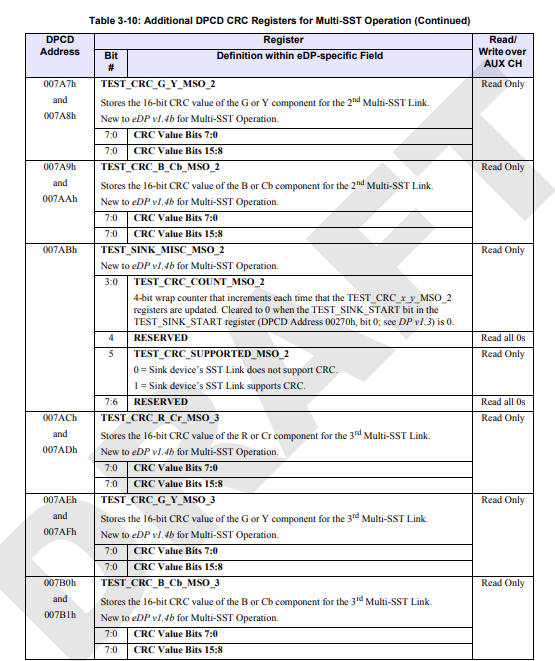

DP v1.3 定义了由 Sink 器件设置的 CRC 寄存器,并且是 PSR作所必需的。这些是 DPCD 地址 00200h 到 002FFh 的 Link/Sink Device Status 字段中的只读 DPCD 寄存器。对于 Multi-SST作,由于仅使用一个 AUX 通道,因此表 3-10 定义了 eDP Sink 器件的额外 CRC 寄存器。这些 registers 的实现是可选的;但是,必须根据需要实现 registers,以实现 PSR2 对 Multi-SST作的支持。

对于 Multi-SST 实现,第一个 SST Link 将使用 DP v1.3 中定义的 TEST_CRC_R_Cr、TEST_CRC_G_Y、TEST_CRC_B_Cb 和 TEST_SINK_MISC 寄存器。

对于使用两个或多个 SST 链接的 Multi-STT 实现,第二个 SST 链接将使用以下寄存器:

• TEST_CRC_R_Cr_MSO_2

• TEST_CRC_G_Y_MSO_2

• TEST_CRC_B_Cb_MSO_2

• TEST_SINK_MISC_MSO_2

对于使用四个 SST 链接的 Multi-STT 实现,第三个 SST 链接将使用以下寄存器:

• TEST_CRC_R_Cr_MSO_3

• TEST_CRC_G_Y_MSO_3

• TEST_CRC_B_Cb_MSO_3

• TEST_SINK_MISC_MSO_3

第四个 SST 链接将使用以下寄存器:

• TEST_CRC_R_Cr_MSO_4

• TEST_CRC_G_Y_MSO_4

• TEST_CRC_B_Cb_MSO_4

• TEST_SINK_MISC_MSO_4

3021

3021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?