背景

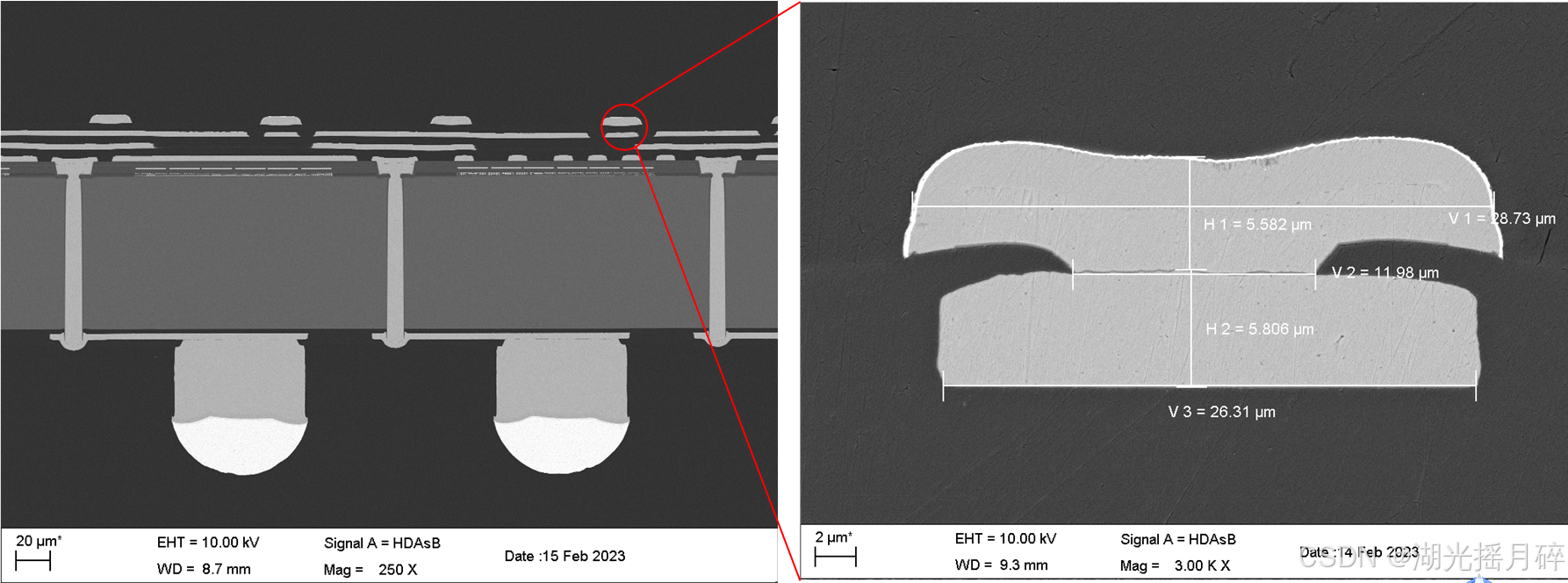

有源转接板是3D IC中常常用到的组件,分为via-first, via-middle和via-last三种,其中via-first指的是在foundry在晶圆制造晶体管之前完成TSV打孔,via-middle则是在晶圆制造晶体管之后金属层之前完成TSV打孔,这两种工艺都需要foundry具有TSV能力,台积电、三星、global foundry等都具备这项能力。via-last则提供了一种更加灵活的方式来制作有源转接板,晶圆从foundry出片之后已经完成了晶体管和金属层的制造,再在预留的位置上进行TSV打孔,一些没有TSV能力的foundry就可以与拥有成熟TSV工艺的OSAT厂商合作满足有源转接板的需求。至于为什么不能先在OSAT厂完成TSV制作后再将晶圆送进foundry呢?这是因为OSTA厂一般比较“脏”,从OSAT厂出来的晶圆将不满足foundry厂的金属管控,因此不会被接受。

后端流程

有源转接板相比于普通后端物理实现的区别是为TSV提前设计的“留空”,这部分在后端设计中会带来不少麻烦,本文的情形是直接给定了TSV的位置,也就意味着这些不规则的TSV留空会一定程度上阻碍P&R。同时作为转接板,这颗芯片面积是比较大的,因此在收timing上也比较困难。同时最棘手的还是DFM相关,通过DRC、ANT检查有一些需要注意的地方。

floorplan

在floorplan阶段就需要导入TSV的位置,这些位置是由RDL的设计导入的(via-last TSV有源转接板打完TSV孔后一般还需要额外增加RDL层将pad扇出到理想位置,这些RDL层同样也会在OSAT厂完成)。因此在这些TSV的位置创建blockage和route guide。下面是代码,先将RDL习惯的中心坐标表示方式转换成边框表示方式,需要创建所有层的blockage和route guide。

# die area

set width 15000

set height 16000

set rail_spacing 3

# read file

set filepath "./script/tsv_coordinate.txt"

if {![file exists $filepath]} {

puts "Error: File $filepath does not exist."

exit 1

}

set tsv_coordinates [open $filepath "r"]

set file_content [read $tsv_coordinates]

close $tsv_coordinates

# Split file content into lines, handling both Unix (\n) and Windows (\r\n) line endings

set tsv_lines [split $file_content "\n"]

# Check if lines are read correctly

puts "Total lines read: [llength $tsv_lines]"

# Create blockage

foreach line $tsv_lines {

# Trim leading and trailing whitespace, including carriage returns

set trimmed_line [string trim $line "\r\n "]

if {$trimmed_line eq ""} {

continue

}

set num_scanned [scan $trimmed_line "%f %f" x y]

if {$num_scanned != 2} {

puts "Skipping malformed line: '$line'"

continue

}

if {![string is double -strict $x] || ![string is double -strict $y]} {

puts "Skipping non-numeric coordinates: x=$x, y=$y"

continue

}

set x [expr {$x + 0}]

set y [expr {$y + 0}]

set x_iccad [expr {$x + $width / 2}]

set y_iccad [expr {$y + $height / 2}]

set size 40

set x1 [expr {$x_iccad - $size}]

set y1 [expr {$y_iccad - $size}]

set x2 [expr {$x_iccad + $size}]

set y2 [expr {$y_iccad + $size}]

# create_placement_blockage -bbox [list [list $x1 $y1] [list $x2 $y2]] -type hard

create_routing_blockage -layers {metal1Blockage via1Blockage metal2Blockage via2Blockage metal3Blockage via3Blockage metal4Blockage via4Blockage metal5Blockage} -bbox [list [list $x1 $y1] [list $x2 $y2]]

create_route_guide \

-coordinate [list [list $x1 $y1] [list $x2 $y2]] \

-no_signal_layers "METAL1 METAL2 METAL3 METAL4 METAL5" \

-no_preroute_layers "METAL1 METAL2 METAL3 METAL4 METAL5" \

-horizontal_track_utilization 0 \

-vertical_track_utilization 0 \

-name "route_guide_${x}_${y}"

}

不规则TSV的坏处就在于创建电源网络时不能保证所有TSV 间隙都能生成power/ground stripe,因此这些地方生成的power/ground rail无法正常供电,导致在这些地方的std cell等也不能被正常供电。因此在自动电源网络生成的情形下,需要直接设置不规则TSV区域直接不让放置std cell或者手动添加stripe,还要在之后每放置、改动std cell、buffer、diode、filler等每一步都多verify_pg_connnection,保证正常供电。

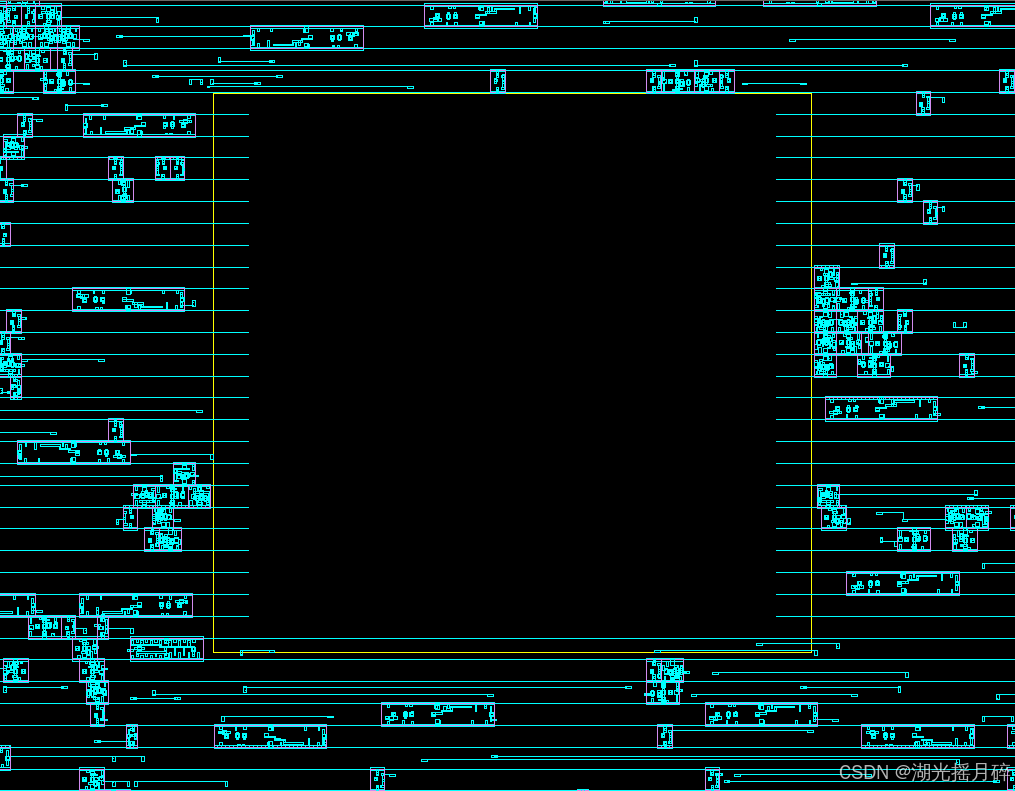

下图是一个TSV块附近的电源轨道,在原本的keep out zoom(route guide和route blockage)的上下左右增加了约1~2个电源轨道的blockage,也就是有的地方可以布线但是不让放置std cell,这可以有效避免出pin的拥塞。

route

由于转接板面积大,一些互连需要跨过半个甚至整个转接板的距离,线长带来的天线效应将会非常明显,一般在route_opt阶段再进行天线效应的修复,但是最好是提前导入天线效应文件,并收紧ratio,比如要求的

define_antenna_layer_rule $lib -mode 4 -layer "METAL1" -ratio 400 -diode_ratio {0.203 0 400.00 2200}

将其收紧到

define_antenna_layer_rule $lib -mode 4 -layer "METAL1" -ratio 200 -diode_ratio {0.203 0 200.00 2200}

并且提前规定好max transition,max_net_route_length,否则在资源紧张的情况下,天线效应将会很难修复。

DFM

在APR工具中完成DRC、ANT、LVS检查后,到calibre检查往往还会检查出新的错,此时可以将检查结果再导回APR工具中,数量少的时候可以手动修复,比如DRC重新调整布线,ANT就增加diode\jump\buffer等手段,在calibre通过检查后才可以最终提交。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?