一、基本概念

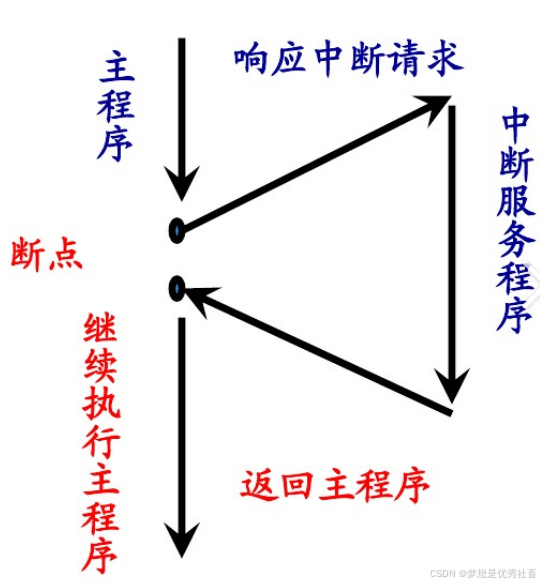

定义:CPU在运行过程中,发生了某些紧急事件需要处理,CPU必须保存现场,暂停当前程序,转而处理紧急事件,处理完毕后再返回原程序继续执行。

内部中断/外部中断:内部中断源来自于CPU内部,如溢出、软件中断指令 等;外部中断来自于CPU外部,由外设提出中断请求

可屏蔽中断/不可屏蔽中断:可屏蔽中断可以通过配置中断控制寄存器等方法被屏蔽,屏蔽后不再处理响应中断

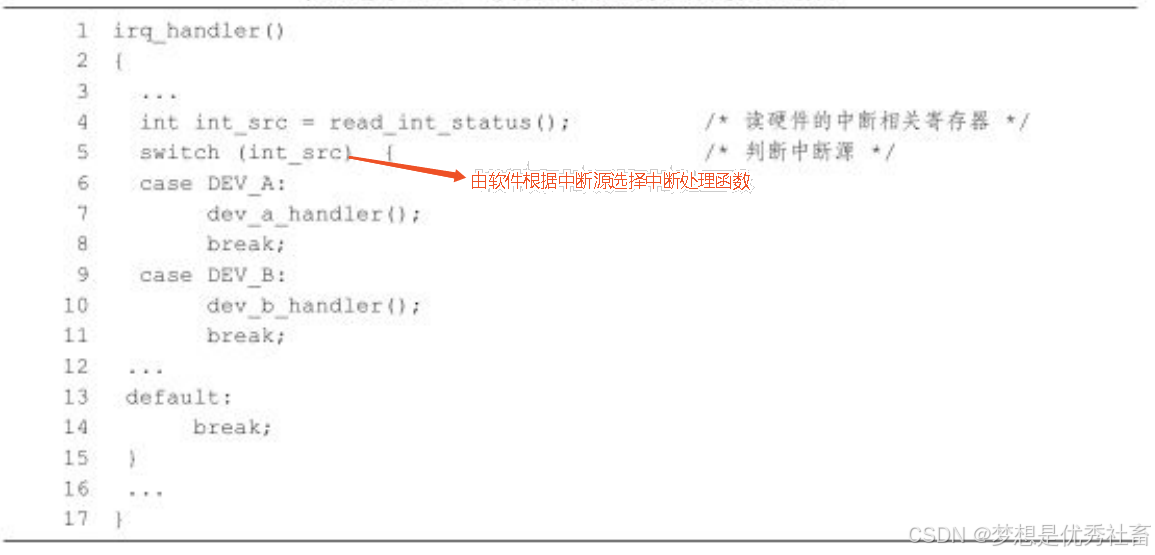

向量中断/非向量中断:向量中断会给中断分配中断号,由硬件决定中断入口地址;非向量中断共享同一个入口地址,进入该地址后,再由软件判别具体执行哪个中断处理函数,下面是非向量中断的中断服务程序示例。

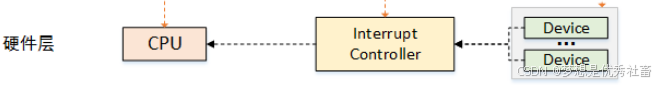

二、中断控制器

中断控制器是负责处理器所有中断源的采集、仲裁和分发的机制/硬件模块。

不同架构使用的中断控制器总结如下:

| 指令架构 | 控制器 | 备注 |

| X86 | 8259(A) -> APIC | APIC相比于8259A,区分本地APIC和I/O APIC,支持多核中断、虚拟中断处理,可支配中断数量更大 |

| ARM | VIC -> NVIC、 GIC(v1-v4) | VIC支持快速中断、向量中断、非向量中断 NVIC 支持中断嵌套,主要用于Cortex-M系列微控制器中 GIC支持多核中断、虚拟中断处理,主要用于Cortex-A/Cortex-R系列处理器中 |

| PowerPC | MPIC、EPIC | MPIC支持多核中断处理 EPIC支持中断嵌套 |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

208

208

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?