实验目的

- 学习寄存器的原理与设计方法;

- 掌握灵活运用Verilog HDL语言进行各种描述与建模的技巧和方法。

实验要求

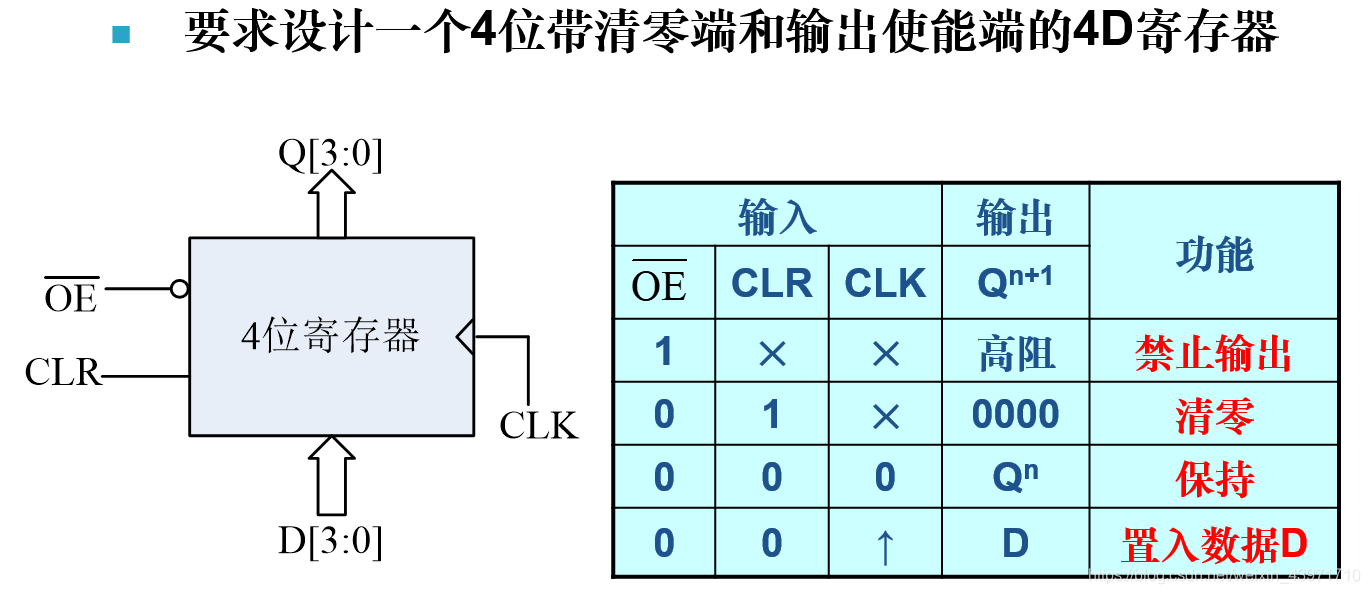

- 使用合适的或者你喜欢的描述方式,编程实现4D寄存器

- 课前任务:在Xilinx ISE上完成创建工程、编辑程序源代码、编程、综合、仿真、验证,确保逻辑正确性。

- 实验室任务:配置管脚,将输入数据信号D[3:0]、控制信号OE#、CLR和CLK信号连接到开关上,注意CLK要接到经过硬件消抖的开关上,将输出Q[3:0]连接到4个LED灯。 生成*.bit文件,完成板级验证。

- 撰写实验报告。

实验原理

程序代码

module jicunqi(OE,CLR,CLK,Q,D);

input[3:0] D;

input OE,CLR,CLK;

output reg[3:0] Q;

always@(OE or CLR or CLK)

if(OE)

begin

Q[3]=0;Q[2]=0;Q[1]=0;Q[0]=0;

end

else if(CLR

本实验旨在学习寄存器的基本原理与设计方法,掌握使用VerilogHDL语言进行寄存器描述与建模的技巧。实验要求编程实现4D寄存器,并在XilinxISE上完成工程创建、编程、综合、仿真及验证,确保逻辑正确性。通过配置管脚,将输入数据信号、控制信号与输出信号连接至硬件设备,完成板级验证。

本实验旨在学习寄存器的基本原理与设计方法,掌握使用VerilogHDL语言进行寄存器描述与建模的技巧。实验要求编程实现4D寄存器,并在XilinxISE上完成工程创建、编程、综合、仿真及验证,确保逻辑正确性。通过配置管脚,将输入数据信号、控制信号与输出信号连接至硬件设备,完成板级验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

9560

9560