简介:RS232串口下载器是嵌入式系统开发中常用的硬件工具,用于实现PC与单片机之间的程序下载和通信。本项目包含完整的“单片机下载口.SchDoc”电路原理图、“单片机下载口.PcbDoc”PCB布局文件及“单片机下载口.PrjPCB”工程管理文件,支持51等系列单片机的稳定固件烧录。通过MAX232电平转换芯片实现TTL与RS232电平兼容,配合DB9接口完成可靠串行通信。该设计涵盖信号完整性、电源管理、保护电路等关键要素,适用于单片机开发、调试与监控,是学习串口通信与硬件设计的理想实践项目。

1. RS232串口通信技术简介

RS232串口通信作为早期广泛应用的串行通信标准之一,在工业控制、嵌入式系统开发中扮演了关键角色。本章将从串口通信的基本概念出发,介绍RS232协议的物理层特性、电气特性、数据格式及典型应用场景。

RS232采用非归零(NRZ)异步串行传输方式,典型电平范围为±3V至±15V,逻辑“1”对应负电压(-5V~-15V),逻辑“0”对应正电压(+5V~+15V),具备较强的抗干扰能力。数据帧通常由起始位、5~8位数据位、可选奇偶校验位和1~2位停止位构成,支持全双工通信。其典型应用包括单片机程序下载、工控设备调试与传感器数据采集等场景,虽逐渐被USB、CAN等取代,但在维护与兼容性需求中仍具实用价值。

2. UART模块与MAX232电平转换电路设计

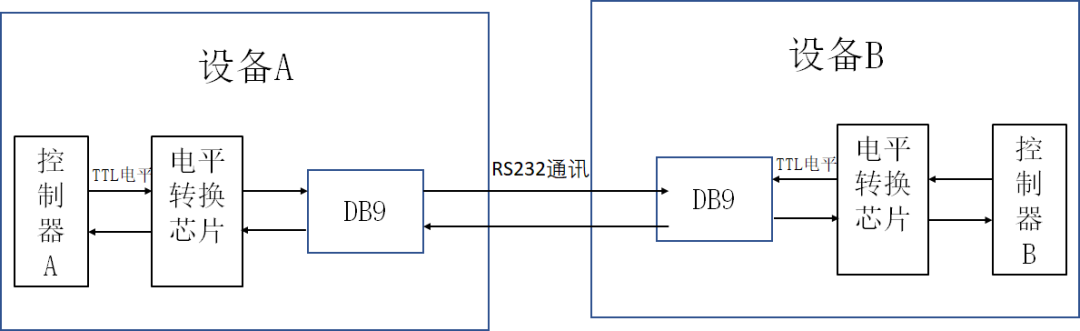

在现代嵌入式系统中,串行通信是实现设备间低速、远距离数据交互的重要手段之一。其中,UART(Universal Asynchronous Receiver/Transmitter)作为最基础的异步串行通信接口模块,广泛集成于各类微控制器内部,承担着调试输出、固件烧录、传感器数据采集等关键任务。然而,由于单片机工作在TTL电平(0V代表逻辑“0”,3.3V或5V代表逻辑“1”),而RS232标准采用负逻辑高电压传输(+3~+15V表示逻辑“0”,-3~-15V表示逻辑“1”),两者之间存在显著的电气不兼容性。因此,在实际应用中必须引入电平转换芯片,如经典的MAX232,完成TTL与RS232之间的双向电平适配。

本章将深入剖析UART模块在单片机中的核心作用及其寄存器配置机制,并详细解析MAX232芯片的工作原理、外围电路设计要点以及替代型号选型策略。通过理论分析与实践指导相结合的方式,帮助工程师构建稳定可靠的串口通信链路,为后续PCB布局和系统级联打下坚实基础。

2.1 UART模块在单片机中的作用

UART作为嵌入式系统中最常见的串行通信外设,其本质是一个全双工异步收发器,能够在没有时钟同步信号的情况下,通过预设的波特率实现点对点的数据传输。它不仅用于程序下载和调试信息输出,还常被应用于GPS模块通信、蓝牙透传、工业仪表协议解析等多种场景。理解UART的工作机制,尤其是其硬件结构与软件配置方法,是开发稳定串口功能的前提。

2.1.1 UART模块的基本结构与工作原理

从架构上看,典型的UART模块由发送单元(Transmitter)、接收单元(Receiver)、控制逻辑、状态寄存器和波特率发生器五个主要部分组成。其工作流程遵循“帧结构”方式进行数据打包与解包,每一帧包含起始位、数据位(通常为8位)、可选的奇偶校验位和停止位(1或2位)。这种异步通信方式不要求主从设备共享时钟线,仅依靠双方预先约定的波特率即可完成同步。

当CPU向UART发送数据时,数据首先写入发送保持寄存器(THR),随后自动移入发送移位寄存器,在波特率时钟驱动下逐位串行输出至TX引脚。接收过程则相反:RX引脚检测到下降沿(起始位)后启动采样逻辑,以波特率的16倍频进行中心采样,确保位判断准确,最终将接收到的串行数据组装成并行字节存入接收缓冲寄存器(RBR),供CPU读取。

为了更直观地展示UART内部工作机制,以下使用Mermaid绘制其典型数据流结构图:

graph TD

A[CPU写入数据] --> B[发送保持寄存器 THR]

B --> C[发送移位寄存器 TSR]

C --> D[TX 引脚输出]

E[RX 引脚输入] --> F[接收移位寄存器 RSR]

F --> G[接收缓冲寄存器 RBR]

G --> H[CPU读取数据]

I[波特率发生器] -->|提供时钟| C

I -->|提供采样时钟| F

J[控制逻辑] -->|管理中断、错误标志| K[状态寄存器 SR]

上述流程体现了UART全双工通信能力的核心支撑机制。值得注意的是,波特率发生器通常基于系统主频分频而来,例如在一个运行于16MHz的MCU中,若需生成9600bps波特率,则需设置合适的分频系数。具体计算公式如下:

\text{Baud Rate} = \frac{F_{\text{osc}}}{16 \times (UBRR + 1)}

其中 $ UBRR $ 是通用异步收发器波特率寄存器(USART Baud Rate Register)的设定值。该公式表明,选择合理的晶振频率和预分频参数对于保证通信精度至关重要。

此外,UART支持多种数据格式组合,常见的包括:

- 数据位:5~9位(常用8位)

- 停止位:1或2位

- 校验位:无校验、奇校验、偶校验

这些参数需在初始化阶段通过配置控制寄存器确定,并且通信双方必须完全一致才能正常通信。

2.1.2 单片机中UART的寄存器配置与中断机制

在大多数8位和32位微控制器中,UART外设通过一组专用寄存器进行控制和状态监控。以AVR系列ATmega328P为例,其USART模块包含多个关键寄存器,下面列出主要寄存器及其功能说明:

| 寄存器名称 | 地址偏移 | 功能描述 |

|---|---|---|

| UCSRnA | - | 状态寄存器A,包含TXC、UDRE、FE、DOR等标志位 |

| UCSRnB | - | 控制寄存器B,启用RX/TX、使能中断、选择字符长度 |

| UCSRnC | - | 控制寄存器C,设置帧格式(数据位、停止位、校验模式) |

| UBRRnH/L | - | 波特率寄存器高/低位,共同决定通信速率 |

| UDRn | - | 数据寄存器,用于读写发送/接收数据 |

以下是ATmega328P初始化UART为9600bps、8N1格式的C语言代码示例:

#include <avr/io.h>

#include <util/setbaud.h>

void uart_init(void) {

// 设置波特率(假设F_CPU=16MHz)

UBRR0H = UBRRH_VALUE; // 使用<util/setbaud.h>自动计算

UBRR0L = UBRRL_VALUE;

// 启用接收器和发送器

UCSR0B = (1 << RXEN0) | (1 << TXEN0);

// 设置帧格式:8位数据,1位停止,无校验

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00); // 8-bit data

}

void uart_transmit(unsigned char data) {

// 等待发送寄存器空

while (!(UCSR0A & (1 << UDRE0)));

UDR0 = data; // 写入数据寄存器触发发送

}

unsigned char uart_receive(void) {

// 等待接收完成

while (!(UCSR0A & (1 << RXC0)));

return UDR0; // 从数据寄存器读取接收到的数据

}

代码逻辑逐行分析:

-

#include <avr/io.h>:包含AVR架构的基础I/O定义。 -

#include <util/setbaud.h>:利用GCC AVR工具链提供的波特率计算头文件,根据F_CPU和目标波特率自动生成UBRR值。 -

UBRR0H = UBRRH_VALUE;和UBRR0L = UBRRL_VALUE;:分别设置波特率寄存器的高八位和低八位。setbaud.h会根据编译时定义的BAUD宏精确计算出最接近的UBRR值,并处理舍入误差。 -

UCSR0B = (1 << RXEN0) | (1 << TXEN0);:启用接收器(RXEN0)和发送器(TXEN0)功能,这是开始通信的前提。 -

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00);:设置数据位为8位(UCSZ02:0 = 0b011),其他位默认为0,即无校验、1停止位。 -

uart_transmit()函数中,先轮询UDRE0标志位,确认发送数据寄存器为空后再写入新数据,防止数据覆盖。 -

uart_receive()函数等待RXC0置位(表示接收完成),然后从UDR0读取数据。

该实现虽为轮询方式,但已具备基本通信能力。在实时性要求较高的系统中,应进一步启用中断机制:

// 使能接收完成中断

UCSR0B |= (1 << RXCIE0);

sei(); // 全局中断使能

ISR(USART_RX_vect) {

uint8_t received_data = UDR0;

// 处理接收到的数据(如放入缓冲区)

}

中断机制的优势在于释放CPU资源,避免持续轮询占用处理器时间。同时可通过环形缓冲区(Ring Buffer)实现高效的数据队列管理,提升通信吞吐效率。

2.2 MAX232芯片的功能与选型依据

尽管现代MCU普遍内置UART模块,但其IO引脚输出的是TTL/CMOS电平,无法直接连接符合RS232标准的设备。MAX232作为一款经典的电平转换芯片,能够实现TTL↔RS232的双向电平转换,广泛应用于工业控制、医疗设备、仪器仪表等领域。深入理解其工作原理及替代方案,有助于在不同电源条件和成本约束下做出合理设计决策。

2.2.1 MAX232的电平转换原理与内部结构

MAX232芯片的核心功能是实现TTL电平与RS232电平之间的相互转换。其内部集成了两个关键子系统:电荷泵电路和驱动器/接收器对。

电荷泵的作用是从单一+5V电源产生±10V左右的正负电压,供RS232电平输出使用。这一设计极大简化了外部供电需求——传统RS232需要±12V双电源,而MAX232仅需单+5V即可工作。电荷泵通过外接四个小型电容(通常为1μF陶瓷电容)构建两级倍压和反相电路,依次生成+10V(V+) 和 -10V(V−)作为驱动电源。

内部结构主要包括:

- 两组TTL→RS232驱动器(T1OUT, T2OUT)

- 两组RS232→TTL接收器(R1IN, R2IN)

- 片上振荡器与电荷泵控制器

- 双电压调节模块

其典型连接方式如下表所示:

| 引脚 | 名称 | 功能说明 |

|---|---|---|

| T1IN | TTL输入1 | 接MCU的TX引脚 |

| T1OUT | RS232输出1 | 接DB9的TD引脚 |

| R1IN | RS232输入1 | 接DB9的RD引脚 |

| R1OUT | TTL输出1 | 接MCU的RX引脚 |

| C1+, C1−, C2+, C2− | 外接电容引脚 | 连接0.1~1μF电容构成电荷泵 |

| V+ / V− | 内部电源输出 | 分别输出+10V和-10V |

| GND | 接地 | 公共参考地 |

工作过程中,当TTL输入为高(5V)时,对应RS232输出为-10V(逻辑“1”);TTL为低(0V)时,RS232输出+10V(逻辑“0”),符合RS232负逻辑规范。接收端则相反,将±10V信号还原为0/5V TTL电平。

2.2.2 常见替代型号比较与选型建议

随着工艺进步,市场上涌现出多种MAX232的改进型与兼容产品,各有优劣。下表对比了几款主流替代芯片的关键参数:

| 型号 | 工作电压 | 是否集成电容 | 最大速率(bps) | 封装 | 备注 |

|---|---|---|---|---|---|

| MAX232 | +5V | 否(需外接4个电容) | 120k | DIP-16/SOIC-16 | 经典型号,通用性强 |

| MAX232A | +5V | 否 | 250k | DIP-16 | 提升速率和ESD保护 |

| MAX3232 | +3.3V/~5.5V | 否 | 1Mbps | TSSOP-16 | 支持宽压,适合低功耗系统 |

| SP3232E | +3~5.5V | 否 | 1Mbps | SOIC-16 | 成本低,性能稳定 |

| ADM232A | +5V | 否 | 250k | DIP-16 | ADI出品,抗干扰强 |

| LTC1348 | +4.5~5.5V | 是(内部集成) | 250k | MSOP-10 | 内置电容,节省空间 |

从选型角度出发,需综合考虑以下因素:

- 供电电压匹配 :若系统使用3.3V MCU,应优先选用MAX3232或SP3232E等支持宽压的型号;

- 通信速率要求 :高速通信(>115200bps)推荐使用MAX3232及以上型号;

- PCB面积限制 :对小型化设计,可考虑LTC1348这类内置电容的集成方案;

- 环境适应性 :工业现场建议选用带增强ESD保护的型号(如MAX232AE);

- 成本敏感度 :消费类电子产品可选用SP3232E等性价比高的国产替代品。

综上所述,MAX232虽为经典,但在新型设计中应结合系统需求灵活选型,兼顾性能、尺寸与可靠性。

2.3 MAX232外围电路设计要点

良好的外围电路设计是保障MAX232稳定工作的关键。尤其在噪声复杂或长线传输环境中,电容选型、电源去耦和PCB布局直接影响通信质量。以下从元件选择到系统稳定性进行全面解析。

2.3.1 电容选型与布局原则

MAX232依赖外部电容构建电荷泵电路,通常需连接四颗电容(C1、C2、C3、C4),分别用于:

- C1、C2:构成第一级倍压电路(+5V → +10V)

- C3、C4:构成反相电路(+5V → -10V)

推荐使用0.1μF至1μF的陶瓷电容(X7R或Y5V材质),耐压不低于16V。优先选择贴片封装(如0805或0603),以减小寄生电感。

布局原则:

- 所有电容应尽可能靠近MAX232引脚放置,走线短而粗;

- 避免在电容路径上串联过孔;

- C1+与C1−、C2+与C2−应成对布线,减少环路面积;

- 不推荐使用电解电容,因其ESR较高,影响电荷泵效率。

错误布局可能导致电压跌落、输出不稳定甚至芯片损坏。

2.3.2 电源去耦与稳定性保障措施

MAX232在电荷泵切换瞬间会产生瞬态电流尖峰,若电源未充分滤波,可能引起系统复位或UART误码。因此必须采取多级去耦策略:

| 滤波层级 | 元件类型 | 容值 | 位置 |

|----------|----------|------|------|

| 主电源入口 | 电解电容 | 10μF | 电源接入端 |

| 芯片附近 | 陶瓷电容 | 100nF | MAX232 VCC引脚旁 |

| 电荷泵节点 | 陶瓷电容 | 1μF | C1-C4位置 |

同时建议在V+和V−输出端各并联一个1μF去耦电容,抑制高频纹波。必要时可在VCC前增加磁珠(如BLM18AG)进一步隔离数字噪声。

最后,绘制一个完整的MAX232典型应用电路图(使用Mermaid模拟示意):

circuitDiagram

title MAX232典型应用电路

signal[VCC +5V] --> capacitor1[10uF]

capacitor1 --> regulator[MAX232 VCC]

regulator --> capacitor2[100nF] --> ground[GND]

regulator --> C1[0.1uF] --> C1plus[C1+]

C1plus --> regulator

regulator --> C2[0.1uF] --> C2plus[C2+]

C2plus --> regulator

regulator --> C3[0.1uF] --> C3minus[C1-]

C3minus --> regulator

regulator --> C4[0.1uF] --> C4minus[C2-]

C4minus --> regulator

mcu[TTL Side MCU] --> T1IN

T1IN --> regulator

regulator --> T1OUT --> rs232pin[DB9 Pin 2]

rs232pin --> R1IN <-- regulator

regulator <-- R1OUT --> mcu

该图虽为简化的文本表示,但仍清晰展示了电源路径、电容连接与信号流向。实际PCB设计中应严格遵循此拓扑结构,确保系统长期稳定运行。

3. RS232接口设计与信号定义解析

在现代嵌入式系统开发中,尽管USB、以太网和无线通信技术日益普及,但RS232串口通信仍因其简单可靠、易于调试而在工业控制、设备维护和单片机程序下载等场景中广泛应用。特别是在不具备复杂操作系统支持的微控制器环境中,通过串口实现固件烧录或日志输出是一种高效且低成本的方式。然而,要确保串口通信稳定可靠,必须深入理解其物理接口的设计原则、信号线的功能分配以及连接方式背后的电气逻辑。

本章聚焦于RS232通信系统的接口设计核心环节——从DB9连接器的引脚定义入手,逐步剖析各关键信号的作用机制,并结合实际应用场景讨论不同接线方式的选择依据。尤其在涉及串口下载功能时,接口定义的准确性直接决定了通信能否建立,因此对TXD、RXD、RTS、CTS等信号的理解至关重要。此外,随着定制化设备增多,自定义串口接口逐渐成为趋势,如何在兼容标准的同时进行合理优化,是硬件工程师必须掌握的能力。

3.1 DB9连接器的引脚定义与功能说明

DB9连接器(又称DE-9)是RS232通信中最常见的物理接口形式之一,广泛应用于PC主板、工控设备及各类通信模块上。它采用9针公头或母头结构,虽然体积较小,但承载了完整的串行通信所需的所有基本信号线。正确理解其引脚定义不仅是电路设计的基础,也是故障排查的关键起点。

3.1.1 标准DB9接口信号分配与电气特性

RS232标准最初由EIA(电子工业协会)制定,定义了一套完整的串行通信协议框架,其中包含了机械接口、电气特性和信号功能三大部分。DB9作为该标准推荐的连接器之一,其引脚功能遵循TIA/EIA-232-F规范。以下是标准DB9母座(常用于设备端)的引脚定义表:

| 引脚号 | 信号名称 | 方向 | 功能描述 |

|---|---|---|---|

| 1 | DCD (Data Carrier Detect) | 输入 | 载波检测,指示远端调制解调器已建立连接 |

| 2 | RXD (Receive Data) | 输入 | 接收数据,来自对方发送端的数据流 |

| 3 | TXD (Transmit Data) | 输出 | 发送数据,本设备向外传输的数据 |

| 4 | DTR (Data Terminal Ready) | 输出 | 数据终端就绪,表明本地设备准备就绪 |

| 5 | GND (Signal Ground) | - | 信号地,所有信号共用的参考电平 |

| 6 | DSR (Data Set Ready) | 输入 | 数据设备就绪,对方设备准备好通信 |

| 7 | RTS (Request To Send) | 输出 | 请求发送,用于硬件流控中的主动请求 |

| 8 | CTS (Clear To Send) | 输入 | 允许发送,响应RTS,表示可接收数据 |

| 9 | RI (Ring Indicator) | 输入 | 振铃指示,多用于拨号调制解调器 |

注:方向以“数据终端设备”(DTE,如计算机)为基准定义。

电气特性分析

RS232采用非对称电压驱动方式,其逻辑电平与TTL/CMOS完全不同。根据规范:

- 逻辑“1” :-3V 至 -15V(负电压)

- 逻辑“0” :+3V 至 +15V(正电压)

这种双极性设计增强了抗干扰能力,允许较长距离传输(典型可达15米)。但在实际应用中,由于现代MCU工作在3.3V或5V TTL电平下,必须通过MAX232类芯片完成电平转换。

flowchart LR

A[TTL UART Output] --> B[MAX232]

B --> C[RS232 DB9 Connector]

C --> D[Remote Device]

D --> E[MAX232]

E --> F[TTL UART Input]

上述流程图展示了完整的双向RS232通信链路:原始TTL信号经电平转换芯片处理后,在DB9接口上传输,再由接收端还原为TTL信号供MCU使用。整个过程依赖于正确的引脚映射和电源支持。

关键信号解释

- GND(第5脚) 是所有信号的公共参考点,任何浮地或接地不良都会导致通信失败。

- DCD与RI 在纯数据通信中通常不使用,主要用于MODEM控制。

- DTR与DSR 构成一对握手信号,可用于唤醒远端设备或确认链路状态。

- RTS/CTS 属于硬件流控信号,在高速或大数据量传输中尤为重要。

3.1.2 接口定义的常见变种与适配方法

尽管存在标准定义,但在实际产品中经常出现非标准的DB9引脚配置,尤其是在专用仪器、医疗设备或老旧系统中。这些“变种”可能出于节省成本、简化布线或兼容特定外设的目的而存在。

常见变种类型

| 类型 | 特征 | 应用场景 |

|---|---|---|

| 简化版(仅保留TXD/RXD/GND) | 只使用3根线,无握手信号 | 单向日志输出、低速通信 |

| 交叉定义(TXD与RXD位置互换) | 第2脚为TXD,第3脚为RXD | 某些工业HMI设备 |

| 自定义信号复用 | 将DCD或DSR用于GPIO控制 | 设备启停触发 |

| 非标准供电引出 | 利用空闲引脚提供+5V或+12V | 外接传感器供电 |

此类变种给系统集成带来挑战,尤其是当需要连接第三方设备时,若未提前确认接口定义,极易造成通信失败甚至损坏接口电路。

适配解决方案

针对接口不一致问题,可采取以下策略:

- 使用万用表测量通断 :最基础的方法是通过蜂鸣档测试两端对应引脚是否导通,并记录实际连接关系。

- 制作转接板(Breakout Board) :将DB9引出为排针,便于灵活跳线或接入示波器监测。

- 软件补偿机制 :某些高级串口驱动支持引脚重映射或虚拟化配置,可在上层屏蔽底层差异。

- 光电隔离+电平转换模块 :增强兼容性的同时提升抗干扰能力。

实际案例:某PLC编程口接线错误分析

一台西门子S7-200系列PLC的编程电缆采用DB9母头,但其内部定义如下:

| 引脚 | 实际功能 |

|---|---|

| 2 | TXD |

| 3 | RXD |

| 5 | GND |

这与标准DTE定义相反(标准应为2=RXD, 3=TXD),因此若使用标准直连线连接PC,则无法通信。解决办法是采用 交叉线 或将MAX232后的TXD/RXD反接。

// 示例:STM32 USART初始化代码片段

void USART1_Init(void) {

RCC->APB2ENR |= RCC_APB2ENR_USART1EN; // 使能USART1时钟

RCC->AHB1ENR |= RCC_AHB1ENR_GPIOAEN; // 使能GPIOA时钟

GPIOA->MODER |= GPIO_MODER_MODER9_1; // PA9 复用模式

GPIOA->AFR[1] |= 0x7 << (1 * 4); // AF7 = USART1_TX

GPIOA->MODER |= GPIO_MODER_MODER10_1; // PA10 复用模式

GPIOA->AFR[1] |= 0x7 << (2 * 4); // AF7 = USART1_RX

USART1->BRR = 0x341; // 波特率115200 @72MHz

USART1->CR1 |= USART_CR1_TE | USART_CR1_RE; // 使能发送与接收

USART1->CR1 |= USART_CR1_UE; // 使能USART

}

代码逻辑逐行解析 :

-RCC->APB2ENR和RCC->AHB1ENR:开启相关外设时钟,否则GPIO和USART无法工作。

-GPIOA->MODER设置PA9和PA10为复用功能模式(0b01 → 输出;0b10 → 复用)。

-AFR[1]寄存器设置复用功能编号,STM32中USART1_TX/RX对应AF7。

-BRR(波特率寄存器)值计算公式为:f_APB / baudrate,此处72MHz下115200对应约625,即0x341。

- 最后启用TE(发送)、RE(接收)和UE(整体使能)。

此代码虽未直接涉及DB9引脚操作,但体现了底层UART配置的重要性。一旦硬件连接因引脚错位导致TXD-RXD反接,即使软件配置正确也无法通信。

3.2 TXD、RXD、RTS、CTS等控制信号的功能分析

串口通信不仅仅是简单的数据收发,还包括一系列用于协调通信双方行为的控制信号。这些信号构成了所谓的“硬件流控”机制,能够在高负载或资源受限环境下有效防止数据丢失。

3.2.1 数据发送与接收信号的工作流程

TXD与RXD的基本工作机制

TXD(Transmit Data)和RXD(Receive Data)是最基本的两条数据线,负责串行比特流的单向传输。它们构成全双工通信的基础,允许两端同时发送与接收。

工作流程如下:

1. 发送方将并行数据写入UART发送缓冲区;

2. UART按设定波特率逐位移出数据至TXD线;

3. 接收方采样RXD线上的电平变化,按相同波特率重组为并行字节;

4. 数据存入接收缓冲区并触发中断(如有使能)。

该过程依赖于严格的时序同步。例如,在115200 bps下,每位持续时间约为8.68μs。若两端波特率偏差超过±2%,可能导致采样错误,引发误码。

电平转换必要性

由于MCU内部UART模块输出为TTL电平(0V/3.3V或0V/5V),而RS232要求±3~15V的摆幅,必须借助电平转换芯片(如MAX232)实现桥接。MAX232内部包含电荷泵电路,能从单一+5V电源生成±10V电压,满足RS232驱动需求。

3.2.2 握手信号的作用与使用场景

握手信号的存在是为了实现流量控制,避免接收方缓冲区溢出。

| 信号 | 控制方向 | 含义 |

|---|---|---|

| RTS (Request To Send) | DTE → DCE | “我准备好发送,请允许” |

| CTS (Clear To Send) | DCE → DTE | “你可以开始发送” |

| DTR (Data Terminal Ready) | DTE → DCE | 终端设备已启动 |

| DSR (Data Set Ready) | DCE → DTE | 通信设备已准备就绪 |

典型握手流程(RTS/CTS)

- 主机(PC)拉高RTS,表示希望发送数据;

- 从机(如MODEM或MCU)检查自身状态;

- 若接收缓冲区有足够空间,拉低CTS(有效为低电平);

- 主机检测到CTS有效后开始发送;

- 若从机缓冲区接近满载,释放CTS(高电平),主机暂停发送。

这种方式称为“硬件流控”,相比软件流控(XON/XOFF),具有更低延迟和更高可靠性。

是否必须使用握手信号?

| 场景 | 是否建议启用 |

|---|---|

| 低速通信(<9600bps) | 否 |

| 固件下载(一次性大量数据) | 是 |

| 日志打印(间歇性小包) | 否 |

| 工业自动化(实时控制) | 是 |

在嵌入式系统中,许多开发者选择忽略RTS/CTS,仅保留TXD/RXD/GND三线通信。这种做法适用于大多数情况,但在高速(≥115200bps)或连续传输场景下,易发生丢包。

实现示例:Linux下启用硬件流控

stty -F /dev/ttyS0 115200 crtscts

该命令在Linux系统中打开ttyS0端口,设置波特率为115200,并启用CRTSCTS(即RTS/CTS流控)。若硬件未连接相应引脚,可能导致通信阻塞。

3.3 串口下载接口的连接方式与线序设计

在单片机开发中,串口常被用作程序下载通道(如STC系列、ESP8266等)。此时接口连接方式直接影响烧录成功率。

3.3.1 直连与交叉连接的区别与适用情况

| 连接类型 | 定义 | 适用场景 |

|---|---|---|

| 直连线 | 同名引脚相连(2→2, 3→3) | DTE-DCE连接(PC-MODEM) |

| 交叉线 | TXD↔RXD互换(2↔3) | DTE-DTE连接(PC-单片机) |

判断方法

- 若两端均为DTE(如PC与开发板),需使用 交叉线 ;

- 若一端为DTE、另一端为DCE(如PC与调制解调器),使用 直连线 。

大多数单片机开发板模拟DCE角色,因此与PC(DTE)连接时应交叉TXD/RXD。

3.3.2 自定义接口设计的注意事项

在紧凑型设备中,常采用JST、PH2.0等小型连接器替代DB9。设计时应注意:

- 明确标注方向 :建议印制“PIN1”标识,防止反插;

- 预留测试点 :在TXD/RXD/GND附近添加焊盘,便于调试;

- 加入保护电路 :TVS二极管防止静电冲击;

- 统一命名规则 :避免混淆“UART1_TX”与“USART2_RX”。

推荐接口布局(4-pin自定义)

| Pin | 信号 | 颜色约定 |

|---|---|---|

| 1 | VCC (+5V) | 红 |

| 2 | TXD | 白 |

| 3 | RXD | 绿 |

| 4 | GND | 黑 |

该设计兼顾供电与通信,适合短距离ISP烧录。

graph TD

PC[PC USB转串口] -->|交叉TXD/RXD| MCU[MCU Bootloader]

MCU -->|响应| ACK[烧录成功提示]

style PC fill:#f9f,stroke:#333

style MCU fill:#bbf,stroke:#333

style ACK fill:#dfd,stroke:#333

该流程图展示了一个典型的串口烧录过程:PC通过串口发送HEX文件,MCU进入Bootloader模式接收数据并写入Flash,完成后返回确认信息。

综上所述,RS232接口设计不仅关乎引脚连接,更涉及电气匹配、协议理解与系统级协同。只有全面掌握信号定义与连接逻辑,才能构建稳定可靠的串口通信链路。

4. PCB设计中的电源管理与信号完整性

在串口通信设备的设计中,PCB(印刷电路板)的电源管理与信号完整性是决定系统稳定性与通信质量的关键因素。RS232通信虽然属于低速通信范畴,但在实际应用中,尤其是在长距离传输或工业环境下,电源噪声、接地不良、信号反射和串扰等问题都会对通信质量产生显著影响。本章将从电源管理设计、地线布局策略、信号完整性优化以及静电与过压保护四个方面,深入探讨在PCB设计中如何保障串口通信系统的稳定性和可靠性。

4.1 串口下载板的电源管理设计

电源管理是PCB设计中最基础但又最关键的部分,尤其是在串口通信板卡中,合理的电源设计可以有效防止电压波动、纹波干扰以及电源不稳定造成的通信异常。

4.1.1 电源输入与电压转换方案

在串口通信设备中,常见的电源输入有USB接口(5V)、外部直流电源(如9V、12V)等。为了适配不同模块的供电需求,通常需要进行电压转换。

以常见的MAX232芯片为例,其工作电压为+5V,而某些外围设备可能提供的是+12V或USB的+5V。此时,需要设计一个DC-DC转换电路或LDO稳压电路来实现电压适配。

// 示例:使用LM1117-5V LDO稳压芯片实现电压转换

VIN = 9V

VOUT = 5V

IOUT = 800mA (典型值)

参数说明与逻辑分析:

-

VIN:输入电压,可以是9V电池或适配器供电; -

VOUT:输出稳定电压,供MAX232芯片和单片机使用; -

IOUT:输出电流能力,需满足系统整体功耗需求; - Cin :输入电容(通常为10uF),用于滤除输入电压的高频噪声;

- Cout :输出电容(通常为10uF或22uF),用于稳定输出电压;

- LDO稳压器适用于低功耗、低噪声的场合,而DC-DC转换器则适合高效率、大电流的应用。

4.1.2 电源滤波与稳定输出设计

为了进一步提高电源质量,通常在LDO前后加入滤波电容和磁珠(Ferrite Bead),形成π型滤波结构。

典型滤波电路结构如下:

| 元件 | 作用 | 值 |

|---|---|---|

| Cin | 输入滤波电容 | 10μF |

| FB | 磁珠 | 600Ω@100MHz |

| Cout | 输出滤波电容 | 22μF |

滤波结构分析:

- Cin 可以滤除来自电源适配器或电池的高频噪声;

- FB 磁珠用于抑制中高频噪声,防止其传导到后续电路;

- Cout 用于稳定输出电压,减少负载突变带来的电压波动;

- 整个π型结构可以有效抑制电源噪声,提升系统稳定性。

4.2 地线布局与参考平面设计

良好的地线设计是确保电路稳定工作的基础。在PCB设计中,不合理的接地方式会导致信号完整性下降、噪声干扰加剧,甚至引发系统不稳定。

4.2.1 单点接地与多点接地的对比分析

| 接地方式 | 特点 | 应用场景 |

|---|---|---|

| 单点接地 | 所有地线汇聚到一个接地点,避免地环路 | 低频、小功率电路 |

| 多点接地 | 每个模块独立接地,降低高频阻抗 | 高频、大功率电路 |

在串口通信板中,由于信号频率较低(通常在115200bps以下),建议采用 单点接地 方式,避免不同模块之间的地电位差导致的共模干扰。

示例电路拓扑结构(Mermaid流程图):

graph TD

A[电源输入] --> B[LDO稳压]

B --> C[主控芯片]

B --> D[MAX232芯片]

C --> E[接地]

D --> E

E --> F[系统接地点]

4.2.2 地平面分割与噪声抑制策略

对于多层PCB设计,通常会保留一个完整的 地平面层(GND Plane) ,用于降低回路面积、减少电磁干扰。

地平面分割建议:

- 对于混合信号电路(如包含模拟和数字部分),应进行地平面分割,避免模拟地和数字地之间的噪声耦合;

- 分割后使用0Ω电阻或磁珠连接两个地平面,以实现单点连接;

- 所有信号线尽量靠近地平面走线,减少回路面积;

- 高速信号线(如UART的TXD/RXD)应优先走表层,并紧邻地平面。

4.3 信号完整性设计要点

虽然RS232通信速率不高,但在实际PCB设计中,仍需考虑信号完整性问题,尤其是在长线传输或高噪声环境下。

4.3.1 高速信号走线的阻抗匹配问题

尽管RS232通信速率较低,但若走线过长或未进行适当的阻抗控制,可能会导致信号反射和失真。

走线长度与频率关系参考表:

| 信号频率 | 最大走线长度(无匹配) |

|---|---|

| 115.2kHz | 100cm |

| 1MHz | 10cm |

| 10MHz | 1cm |

结论: 在115.2kbps通信速率下,走线长度控制在1米以内通常无需阻抗匹配;但若使用更高波特率(如921.6kbps),则需考虑走线特性阻抗匹配问题。

4.3.2 串扰与反射的抑制方法

串扰抑制措施:

- 将敏感信号线与高噪声信号线(如时钟线)保持足够间距;

- 使用带状线结构或微带线结构,减少串扰;

- 信号线与地平面保持平行,降低耦合电容。

反射抑制方法:

- 对于高速信号线,使用端接电阻(如50Ω)进行阻抗匹配;

- 在接收端并联RC吸收电路,抑制信号回弹;

- 减少直角走线,采用45°走线或圆弧过渡,降低高频谐振风险。

示例端接电路:

// 并联端接电阻电路

R_term = 50Ω;

C_term = 100pF;

- R_term :用于匹配传输线特性阻抗;

- C_term :用于吸收高频震荡,稳定信号波形。

4.4 静电防护与过压保护电路实现

RS232接口通常暴露在外部环境中,容易受到静电放电(ESD)和过压冲击的影响,因此必须设计相应的保护电路。

4.4.1 ESD保护器件选型与布放位置

常用ESD保护器件:

- TVS(瞬态电压抑制二极管)

- ESD抑制器(如ON Semiconductor的ESD9B5.0ST5G)

布放原则:

- ESD器件应尽可能靠近接口端子,缩短放电路径;

- 接地路径应尽量短,避免形成地弹(Ground Bounce);

- 通常在TXD、RXD、RTS、CTS等信号线上并联TVS器件。

典型ESD保护电路:

// TVS器件参数

Vbr = 6.8V

Vcl = 12V

- Vbr :击穿电压,略高于正常工作电压(如5V);

- Vcl :钳位电压,确保在静电冲击下不会损坏后级芯片。

4.4.2 过压保护电路的设计与测试

除了ESD,还需考虑长期过压或反接情况对芯片的损害。可采用如下方式:

- 在电源输入端加入自恢复保险丝(PTC);

- 并联TVS用于吸收瞬态高压;

- 使用MOSFET或二极管防止反向电流流入系统。

测试方法:

- 使用ESD发生器对RS232接口施加±8kV空气放电;

- 监测MAX232芯片的输入输出波形是否变形;

- 检查电源输入是否因过压而损坏;

- 使用示波器捕捉信号线上是否出现异常尖峰。

本章从电源管理、地线布局、信号完整性及静电防护四个方面,系统性地讲解了在RS232串口通信板的PCB设计中应关注的关键问题,并通过电路设计、参数说明、流程图、表格等形式进行了详细阐述。这些设计原则不仅适用于RS232通信,也可为其他低速通信接口的PCB设计提供参考。

5. 波特率匹配与通信稳定性优化

在嵌入式系统和工业控制设备中,RS232串口通信虽然结构简单、成本低廉,但其通信的稳定性和数据传输的准确性高度依赖于波特率的精确匹配以及整体通信链路的设计优化。随着现代电子系统对实时性、可靠性的要求不断提高,传统串行通信面临诸如时钟漂移、噪声干扰、线路阻抗不匹配等挑战。因此,深入理解波特率的本质及其对通信质量的影响,并在此基础上实施有效的软硬件协同优化策略,已成为确保串口通信长期稳定运行的关键环节。

本章将围绕“波特率”这一核心参数展开系统性分析,从基本概念出发,逐步揭示其在实际应用中的设置原则与同步机制;随后聚焦于误码率的成因及提升通信可靠性的多种技术手段;最后通过构建真实测试环境,介绍如何科学地评估和调试串口通信系统的稳定性。整个过程不仅涵盖理论推导,还结合典型电路设计、寄存器配置代码和信号完整性分析方法,力求为具备五年以上经验的工程师提供可落地的技术参考。

5.1 波特率的基本概念与设置原则

波特率(Baud Rate)是衡量串行通信中符号传输速率的重要指标,表示每秒传输的信号变化次数,单位为“波特”(Baud)。在RS232通信中,通常采用异步串行传输方式,即发送端与接收端各自使用独立的晶振时钟源进行数据采样,因此双方必须预先约定相同的波特率才能正确解析数据帧。若波特率不一致,会导致采样点偏移,进而引发字符错位或误码。

尽管在大多数情况下,波特率数值上等于比特率(bit/s),但这并非绝对。例如,在多电平调制系统中,一个符号可能携带多个比特信息,此时波特率小于比特率。然而在标准RS232通信中,每个符号仅代表一位二进制数据,故两者数值相等。

5.1.1 波特率与数据传输速率的关系

在典型的8-N-1格式(8位数据位、无校验位、1位停止位)下,每一帧包含起始位(1 bit)、数据位(8 bits)、停止位(1 bit),共10个比特。假设波特率为9600,则每秒可传输的数据字节数为:

\text{有效数据速率} = \frac{9600}{10} = 960 \text{ 字节/秒}

这表明即使物理层支持高波特率,实际有效吞吐量仍受限于协议开销。常见的标准波特率包括:1200、2400、4800、9600、19200、38400、57600、115200等,这些数值源于早期电话线调制解调器的历史沿革,并被广泛固化在各类MCU的UART模块中。

不同应用场景对波特率的选择有明确倾向:

- 低速场景 (如传感器读取):选用9600或更低,以降低功耗和电磁干扰;

- 中高速场景 (如PLC通信):常用19200至57600;

- 高速调试接口 :可达115200甚至更高(需注意信号完整性)。

以下表格列出了常见波特率下的帧时间与最大吞吐量对比:

| 波特率 (bps) | 每帧比特数(8-N-1) | 帧时间 (μs) | 每秒帧数 | 有效数据速率 (B/s) |

|---|---|---|---|---|

| 9600 | 10 | 1041.7 | 960 | 960 |

| 19200 | 10 | 520.8 | 1920 | 1920 |

| 38400 | 10 | 260.4 | 3840 | 3840 |

| 57600 | 10 | 173.6 | 5760 | 5760 |

| 115200 | 10 | 86.8 | 11520 | 11520 |

注:帧时间 = 总比特数 / 波特率 × 10⁶

值得注意的是,当波特率超过115200时,许多老旧设备或长距离电缆可能无法维持稳定通信,主要原因包括:

- 线路分布电容导致边沿畸变;

- 接收端采样窗口缩小,对时钟误差更敏感;

- EMI干扰加剧,增加误判概率。

为此,在选择波特率时应综合考虑通信距离、媒介质量、MCU主频及时钟精度等因素。

波特率计算公式与误差容忍度

大多数微控制器通过设定UART的分频寄存器(如UBRR in AVR系列)来生成目标波特率。其通用计算公式如下:

UBRR = (F_CPU / (16 * BAUD)) - 1;

其中:

- F_CPU :系统主频(Hz)

- BAUD :期望波特率(bps)

- UBRR :需写入的波特率寄存器值

该公式适用于标准模式(U2X=0),若启用双速模式(U2X=1),则分母变为8:

UBRR = (F_CPU / (8 * BAUD)) - 1; // 双速模式

下面以ATmega328P为例,演示在 F_CPU = 16MHz 时配置115200波特率的过程:

#include <avr/io.h>

void uart_init_115200() {

uint16_t ubrr = (16000000UL / (16 * 115200UL)) - 1; // 计算UBRR值

UBRR0H = (uint8_t)(ubrr >> 8); // 高8位

UBRR0L = (uint8_t)ubrr; // 低8位

UCSR0B = (1 << RXEN0) | (1 << TXEN0); // 使能收发

UCSR0C = (1 << UCSZ01) | (1 << UCSZ00); // 8位数据,1位停止

}

逐行逻辑分析:

1. 第4行:利用预定义宏计算UBRR值, UL 后缀防止整数溢出;

2. 第5–6行:将16位结果拆分为高/低字节写入 UBRR0H 和 UBRR0L ;

3. 第7行:设置 RXEN0 和 TXEN0 位使能接收与发送功能;

4. 第8行:配置 UCSZ01 和 UCSZ00 选择8位数据长度(见AVR数据手册)。

执行上述代码后,实际波特率可通过反向计算验证:

\text{Actual Baud} = \frac{F_{CPU}}{16 \times (\text{UBRR} + 1)}

若 UBRR = 8 ,则:

\text{Actual Baud} = \frac{16,000,000}{16 \times 9} ≈ 111,111 \text{ bps}

相对误差为:

\frac{|111111 - 115200|}{115200} ≈ 3.55\%

一般认为,UART通信允许的最大时钟误差为±2%~±3%,否则在帧末尾采样时可能发生滑动偏差。因此此例中误差已超标,可能导致通信失败。

解决方案包括:

- 改用 F_CPU = 14.7456 MHz 晶振(专为标准波特率设计);

- 启用U2X双速模式,提高分辨率;

- 使用分数波特率生成器(如STM32 USART_BRR寄存器支持小数部分)。

5.1.2 不同设备间的波特率同步策略

在跨平台通信中,如PC与单片机、ARM与DSP之间通过RS232互联,由于各自时钟源精度差异(特别是RC振荡器 vs 晶体振荡器),容易出现累积性采样误差。为此,需采取主动同步策略以增强兼容性。

自适应波特率检测机制

某些高端MCU(如NXP LPC系列)支持“自动波特率检测”(Autobaud),其原理是在接收到特定引导字符(如‘U’或0x55)时,测量起始位宽度并动态调整内部分频系数。流程如下图所示:

graph TD

A[开始] --> B[等待起始位下降沿]

B --> C[启动定时器捕获上升沿]

C --> D[计算半个周期时间]

D --> E[估算波特率]

E --> F[配置UART分频寄存器]

F --> G[进入正常通信状态]

实现代码示意(基于LPC1114):

uint32_t detect_baudrate(void) {

uint32_t start_time, stop_time;

while ((LPC_UART->LSR & (1<<0)) == 0); // 等待数据到达

start_time = get_timer_ticks(); // 记录起始位开始

while (LPC_UART->RBR != 0x55); // 等待0x55字符

stop_time = get_timer_ticks();

return estimate_from_time(stop_time - start_time);

}

该方法显著提升了设备互操作性,尤其适用于现场更换主机或固件升级场景。

软件重试协商机制

在不具备硬件Autobaud能力的系统中,可通过软件轮询尝试常见波特率列表:

const uint32_t common_bauds[] = {9600, 19200, 38400, 57600, 115200};

int try_all_baud_rates() {

for (int i = 0; i < 5; i++) {

uart_set_baud(common_bauds[i]);

if (send_and_expect_ack('P')) { // 发送探测包

return common_bauds[i];

}

}

return -1; // 失败

}

该策略常用于Bootloader设计中,极大简化用户配置负担。

综上所述,合理选择并精确配置波特率是保障串口通信成功的前提。工程师应在设计初期充分评估时钟源稳定性、通信负载需求及上下游设备兼容性,必要时引入自适应机制以提升系统鲁棒性。

6. RS232原理图与PCB协同设计与应用实践

6.1 原理图(SchDoc)设计规范与技巧

在RS232串口通信模块的设计中,原理图是整个设计的基础。它不仅决定了电路的逻辑功能,也影响后续PCB布局布线的效率与质量。

6.1.1 元器件符号绘制与标注标准

在Altium Designer等EDA工具中,绘制元器件符号时应遵循以下规范:

- 符号标准化 :使用行业通用的符号图形,如电阻、电容、IC等,避免自定义图形造成误解。

- 引脚编号与功能标注 :每个引脚需明确标注其电气功能(如VCC、GND、TXD等),并使用标准命名。

- 封装关联 :确保每个元器件符号都正确关联到其对应的PCB封装(Footprint),避免后期匹配错误。

例如,MAX232芯片的原理图符号应标注其电源引脚(VCC、GND)、电容连接引脚(C1+、C1-等)和串口信号引脚(T1OUT、R1IN等)。

6.1.2 电气连接的正确性验证方法

完成原理图绘制后,应使用EDA工具的电气规则检查(ERC)功能进行验证:

ERC检查内容包括:

- 未连接的引脚

- 电源与地冲突

- 输入/输出端口不匹配

- 未定义网络标签

此外,可使用“Compile”功能生成编译报告,检查是否存在电气错误。确保所有信号线、电源线和地线正确连接。

6.2 PCB(PcbDoc)布局布线策略

PCB设计是RS232通信模块实现的关键环节,合理的布局与布线直接影响信号完整性与抗干扰能力。

6.2.1 元件布局的合理性与可维护性

布局时应遵循以下原则:

- 模块化布局 :将MAX232芯片、UART接口、DB9连接器等模块集中布局,减少信号线长度。

- 热管理考虑 :高功耗元件应远离敏感模拟电路,避免局部过热影响稳定性。

- 维护与调试便利 :预留测试点,方便后期调试与测量。

例如,MAX232芯片应尽量靠近DB9接口,以减少长距离走线带来的干扰。

6.2.2 关键信号线的走线优化技巧

RS232通信中,TXD、RXD为关键信号线,其走线质量直接影响通信稳定性:

- 走线最短化 :缩短TXD与RXD信号线长度,减少阻抗变化。

- 避免直角走线 :采用45°角或圆弧走线,减少信号反射。

- 地平面处理 :在信号线附近铺设地平面,降低回路面积,抑制噪声。

此外,高速信号线应尽量避免与电源线平行走线,防止串扰。

graph TD

A[原理图设计] --> B[PCB导入]

B --> C[元件布局]

C --> D[布线策略]

D --> E[电源与地线处理]

E --> F[信号完整性优化]

F --> G[设计规则检查]

6.3 Altium Designer工程文件管理与输出

6.3.1 工程文件结构与版本控制

在Altium Designer中,建议采用以下工程文件结构:

RS232_Design/

├── RS232.SchDoc // 原理图文件

├── RS232.PcbDoc // PCB文件

├── RS232.PrjPcb // 工程文件

├── Libraries/

│ ├── MAX232.IntLib // 集成库

│ └── UART_Symbols.SchLib // 原理图符号库

├── Outputs/

│ ├── BOM.csv // 材料清单

│ └── Gerber/ // Gerber文件输出目录

版本控制建议使用Git或SVN工具,结合Altium的版本控制插件,实现设计文件的协同开发与历史回溯。

6.3.2 BOM表生成与Gerber文件输出

在Altium Designer中,生成BOM表的步骤如下:

- 打开原理图文件,点击菜单【Reports】→【Bill of Materials】。

- 选择需要输出的字段,如元件名称、值、封装、数量等。

- 导出为CSV或Excel格式。

生成Gerber文件步骤如下:

- 点击菜单【File】→【Fabrication Outputs】→【Gerber Files】。

- 设置单位、格式、层选择(建议包含Top Layer、Bottom Layer、Silk Screen、Solder Mask等)。

- 点击“OK”生成Gerber文件,并输出到指定目录。

6.4 RS232下载器在单片机开发中的实际应用

6.4.1 下载器与目标板的连接方式

RS232下载器通常通过DB9或自定义接口与目标单片机连接,常见连接方式如下:

| 引脚 | 下载器 | 单片机 |

|---|---|---|

| 2 | RXD | TXD |

| 3 | TXD | RXD |

| 5 | GND | GND |

注意:部分下载器可能还需要RTS、CTS握手信号用于自动下载控制,应根据具体芯片(如STC系列)的烧录协议配置。

6.4.2 常见问题排查与应用案例分享

常见问题及排查方法:

- 无法识别设备 :检查DB9接口连接是否正确,使用万用表测量电压是否正常。

- 通信失败 :检查波特率设置是否与单片机一致,使用示波器观察TXD信号是否正常。

- 烧录中断 :检查MAX232芯片是否损坏,电容是否虚焊。

应用案例:

某项目使用STC89C52单片机,通过RS232下载器进行程序烧录。在实际应用中,因MAX232的C1+电容焊接不良,导致电平转换不稳定,最终通过更换电容解决通信问题。

后续章节将探讨RS232与USB转串口的兼容性设计与调试方法。

简介:RS232串口下载器是嵌入式系统开发中常用的硬件工具,用于实现PC与单片机之间的程序下载和通信。本项目包含完整的“单片机下载口.SchDoc”电路原理图、“单片机下载口.PcbDoc”PCB布局文件及“单片机下载口.PrjPCB”工程管理文件,支持51等系列单片机的稳定固件烧录。通过MAX232电平转换芯片实现TTL与RS232电平兼容,配合DB9接口完成可靠串行通信。该设计涵盖信号完整性、电源管理、保护电路等关键要素,适用于单片机开发、调试与监控,是学习串口通信与硬件设计的理想实践项目。

1677

1677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?