简介:ARM处理器广泛应用于嵌入式与移动计算领域,其软件开发涉及ELF可执行文件、Image系统镜像及工具链的深度使用。本文档集合涵盖ARM专属ELF格式、armlink链接器、armcc编译器的使用方法,以及镜像文件生成流程,帮助开发者掌握从源码编译到可执行映像制作的完整过程。通过系统学习相关PDF技术资料,深入理解ARM平台程序的构建机制,为嵌入式开发、调试与优化提供坚实基础。

1. ARM处理器架构与嵌入式开发概述

ARM架构作为当前嵌入式系统中最主流的处理器架构之一,以其高性能、低功耗和高集成度的特点广泛应用于移动设备、物联网终端和工业控制领域。其采用精简指令集(RISC)设计,支持多种运行模式(如用户、SVC、IRQ等)和两种主要指令集状态(ARM/Thumb),为嵌入式软件开发提供了灵活的执行环境。在开发流程中,从C/C++源码到最终烧录的镜像文件,需经历编译、链接、格式转换等多个阶段,其中ELF文件作为中间产物,承载了程序结构、符号信息和重定位元数据,是理解ARM嵌入式系统构建机制的关键起点。

2. ELF文件格式基本结构与三种类型(对象文件、可执行文件、共享库)

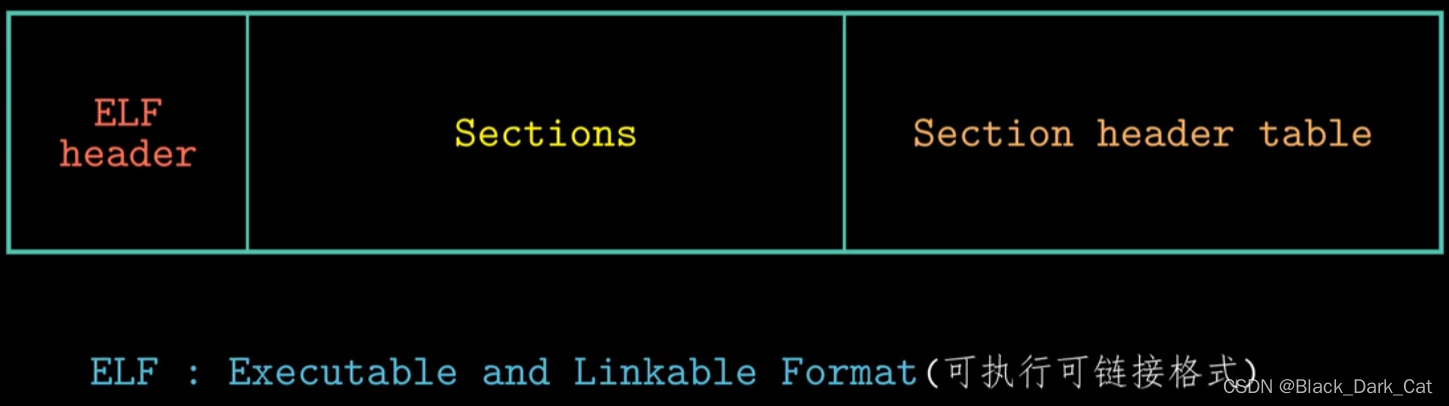

ELF(Executable and Linkable Format)是现代类Unix系统中最核心的二进制文件格式标准,广泛应用于嵌入式系统、桌面操作系统以及服务器平台。它不仅定义了程序在磁盘上的组织方式,还为链接器、加载器和运行时环境提供了必要的元数据支持。理解ELF文件的内部结构对于深入掌握编译、链接、加载乃至调试过程至关重要。尤其在ARM架构下,由于其复杂的指令集混合模式(ARM/Thumb)、多级特权模式及特定的ABI规则,ELF文件承载的信息远比表面看起来更为丰富。

ELF设计的核心理念在于“一格式多用途”,即通过统一的容器结构支持多种形态的文件:可重定位对象文件(.o)、可执行文件(如a.out或binaries)、共享库(.so),甚至核心转储(core dump)。这种灵活性使得工具链可以在不同阶段使用同一格式进行交互,极大提升了构建系统的模块化程度和可维护性。更重要的是,ELF文件中包含的节区(section)和段(segment)信息直接决定了代码如何被映射到内存、符号如何解析、动态链接如何触发等关键行为。

本章将从ELF的整体结构出发,逐步剖析其三大组成部分——ELF头部、程序头部表和节区头部表的功能机制,并结合实际场景说明它们在不同类型ELF文件中的表现差异。随后,深入探讨三类主要ELF文件形态在软件构建流程中的角色定位:从源码编译生成的可重定位文件,经链接后形成的可执行文件,再到实现代码复用的共享库。通过对每种类型的结构特征、用途及其运行时行为的细致分析,读者将建立起对整个ELF生态系统的完整认知框架,为后续理解ARM平台特有的ELF属性打下坚实基础。

2.1 ELF文件的整体结构与核心组成部分

ELF文件采用分层结构设计,由若干固定偏移位置的数据块组成,这些数据块共同描述了文件的内容布局、加载方式和符号信息。一个典型的ELF文件通常包括以下三个核心部分: ELF头部(ELF Header) 、 程序头部表(Program Header Table) 和 节区头部表(Section Header Table) 。这三者分别服务于不同的系统组件:ELF头部供所有工具读取基本信息;程序头部表用于加载器确定内存映像布局;节区头部表则主要用于链接和调试阶段的符号管理。

2.1.1 ELF头部(ELF Header)详解

ELF头部位于文件起始处,占据固定的52字节(32位系统)或64字节(64位系统),是解析整个文件的入口点。它以C语言结构体 Elf32_Ehdr 或 Elf64_Ehdr 形式存在,定义于 <elf.h> 头文件中。该结构体的第一个字段 e_ident 是一个16字节的数组,包含了用于快速识别和验证ELF文件合法性的魔数(Magic Number)及其他标识信息。

- e_ident字段解析与魔数含义

e_ident 的前四个字节构成著名的“ELF魔数”: 0x7F, 'E', 'L', 'F' (即 \x7fELF ),这是所有符合ELF规范的文件必须具备的签名。接下来的几个字节用于指示文件的类别(class,32位或64位)、数据编码方式(endianness)、版本号以及操作系统ABI类型。例如:

| 偏移 | 字段名 | 含义说明 |

|---|---|---|

| 0 | EI_MAG[4] | 魔数 \x7fELF ,用于快速识别 |

| 4 | EI_CLASS | 1=ELF32, 2=ELF64 |

| 5 | EI_DATA | 1=little-endian, 2=big-endian |

| 6 | EI_VERSION | 必须为1 |

| 7 | EI_OSABI | 操作系统ABI标识(如Linux=3, ARM EABI=255) |

这一设计允许加载器在不解码整个文件的情况下迅速判断是否能够处理该二进制文件。例如,在嵌入式开发中,若目标设备为ARM Cortex-M系列MCU,期望使用32位小端序的EABI格式,则可通过检查 e_ident[EI_CLASS] == ELFCLASS32 && e_ident[EI_DATA] == ELFDATA2LSB && e_ident[EI_OSABI] == 255 来确认兼容性。

- e_type、e_machine、e_version等关键字段作用

紧随 e_ident 之后的是 e_type 、 e_machine 和 e_version 等关键字段:

-

e_type:表示文件类型,常见值有: -

ET_REL(1):可重定位文件(.o) -

ET_EXEC(2):可执行文件 -

ET_DYN(3):共享对象(.so 或 PIC 可执行文件) -

ET_NONE(0):未知类型 -

e_machine:指定目标架构,对于ARM处理器,典型值为EM_ARM(40),而在AArch64平台上为EM_AARCH64(183)。这个字段直接影响反汇编器、调试器和模拟器的选择逻辑。 -

e_version:应设为EV_CURRENT(1),表示当前版本。

此外, e_entry 字段存储程序入口地址(虚拟地址),仅对可执行文件和共享库有效; e_phoff 和 e_shoff 分别指向程序头部表和节区头部表的文件偏移; e_flags 可用于传递架构特定标志,如ARM平台可能设置 EF_ARM_ABI_VERSION 以标明使用的EABI版本。

下面是一个简化版的 Elf32_Ehdr 结构体示例及其在代码中的访问方式:

#include <elf.h>

#include <fcntl.h>

#include <unistd.h>

#include <stdio.h>

void parse_elf_header(const char *filename) {

int fd = open(filename, O_RDONLY);

Elf32_Ehdr ehdr;

read(fd, &ehdr, sizeof(ehdr));

// 输出魔数校验

if (ehdr.e_ident[EI_MAG0] != 0x7f ||

ehdr.e_ident[EI_MAG1] != 'E' ||

ehdr.e_ident[EI_MAG2] != 'L' ||

ehdr.e_ident[EI_MAG3] != 'F') {

printf("Not an ELF file\n");

return;

}

printf("Class: %s\n", ehdr.e_ident[EI_CLASS] == ELFCLASS32 ? "ELF32" : "ELF64");

printf("Data: %s\n", ehdr.e_ident[EI_DATA] == ELFDATA2LSB ? "Little-endian" : "Big-endian");

printf("Type: ");

switch(ehdr.e_type) {

case ET_REL: printf("Relocatable\n"); break;

case ET_EXEC: printf("Executable\n"); break;

case ET_DYN: printf("Shared object\n"); break;

default: printf("Unknown\n"); break;

}

printf("Machine: %s\n", ehdr.e_machine == EM_ARM ? "ARM" : "Other");

printf("Entry point: 0x%x\n", ehdr.e_entry);

close(fd);

}

逻辑分析与参数说明 :

上述代码展示了如何手动读取并解析ELF头部信息。首先通过open()打开文件,调用read()一次性读入sizeof(Elf32_Ehdr)字节数据。接着逐项检查e_ident中的魔数字段确保合法性。随后根据EI_CLASS和EI_DATA输出体系结构信息,再依据e_type和e_machine打印文件类型与目标CPU。最后输出入口地址e_entry。此方法常用于自定义加载器或固件分析工具中,无需依赖外部命令行工具即可完成初步诊断。

2.1.2 程序头部表(Program Header Table)功能分析

程序头部表(Program Header Table)是操作系统加载器用来决定如何将ELF文件映射到进程地址空间的关键数据结构。它由一系列 Elf32_Phdr 结构体组成,每个结构体描述一个“段”(Segment),即一组具有相同权限属性(如可读、可写、可执行)的连续内存区域。

- LOAD段、DYNAMIC段、INTERP段的用途

最常见的段类型包括:

- PT_LOAD :表示需要被加载到内存的段,如代码段(.text)和数据段(.data)。每个LOAD段对应一个虚拟地址范围,加载器会将其从文件中复制或映射到指定VMA(Virtual Memory Address)。

- PT_DYNAMIC :指向动态链接信息,包含

.dynamic节区的位置,用于查找共享库依赖、符号表、重定位表等。 - PT_INTERP :指定动态链接器路径(如

/lib/ld-linux.so.3),仅存在于依赖共享库的可执行文件中。 - PT_TLS :线程局部存储模板。

- PT_PHDR :程序头部表自身的映射位置。

每个 Elf32_Phdr 包含如下重要字段:

| 字段 | 描述 |

|---|---|

p_type | 段类型(如PT_LOAD, PT_DYNAMIC) |

p_offset | 文件中的偏移 |

p_vaddr | 虚拟地址(VMA) |

p_paddr | 物理地址(PA,在嵌入式中有时使用) |

p_filesz | 文件中占用大小 |

p_memsz | 内存中分配大小(如.bss段memsz > filesz) |

p_flags | 权限标志(PF_R=读, PF_W=写, PF_X=执行) |

p_align | 对齐要求 |

例如, .bss 节区虽然不占文件空间( p_filesz=0 ),但需在内存中分配空间( p_memsz > 0 ),因此常出现在LOAD段中并标记为可写。

- 在可执行文件加载过程中的角色

当内核执行 execve() 系统调用时,会遍历程序头部表,创建相应的VMA并调用 mmap() 将各LOAD段映射进内存。对于动态链接的程序,还会启动 PT_INTERP 指定的解释器(如 ld.so )来完成符号解析和重定位。

下面是一个使用 readelf -l 查看程序头部表的实际输出示例(截取片段):

Program Headers:

Type Offset VirtAddr PhysAddr FileSiz MemSiz Flg Align

LOAD 0x000000 0x00010000 0x00010000 0x00500 0x00500 R E 0x1000

LOAD 0x000500 0x00011000 0x00011000 0x00200 0x00200 RW 0x1000

DYNAMIC 0x000510 0x00011010 0x00011010 0x00100 0x00100 RW 0x8

INTERP 0x000200 0x00010200 0x00010200 0x00014 0x00014 R 0x1

可以看出,第一个LOAD段加载只读可执行代码(R E),第二个加载可读写数据段(RW),DYNAMIC段提供动态链接信息,INTERP段指定解释器路径。

graph TD

A[execve()] --> B{解析ELF头部}

B --> C[读取程序头部表]

C --> D[遍历PT_LOAD段]

D --> E[调用mmap映射到VMA]

C --> F[发现PT_INTERP?]

F -- 是 --> G[启动ld.so]

F -- 否 --> H[直接跳转至e_entry]

G --> I[完成符号解析与重定位]

I --> J[跳转至入口函数]

该流程图清晰地描绘了ELF文件从加载到运行的过程。程序头部表在此过程中充当“导航图”,指导加载器如何构造进程镜像。

2.1.3 节区头部表(Section Header Table)及其意义

节区头部表(Section Header Table)主要用于链接和调试阶段,记录了文件中各个“节区”(Section)的详细信息。每个节区代表一种特定类型的数据,如代码、初始化数据、未初始化数据、符号表等。与程序头部表面向“运行时”的段不同,节区更偏向“构建期”的组织单元。

- .text、.data、.bss、.rodata等常见节区的作用

| 节区名 | 用途说明 |

|---|---|

.text | 存放编译后的机器指令,通常只读可执行 |

.data | 已初始化的全局/静态变量 |

.bss | 未初始化或初值为零的全局/静态变量,节省磁盘空间 |

.rodata | 只读数据,如字符串常量、const变量 |

.symtab | 符号表,记录函数和变量名称及其地址 |

.strtab | 字符串表,存放符号名字符串 |

.rel.text / .rela.text | 代码段的重定位条目 |

.debug_* | DWARF调试信息 |

例如,以下C代码:

int global_init = 42; // → .data

int global_uninit; // → .bss

const char* msg = "Hello"; // → .rodata + .data(指针)+ .rodata(字符串)

void func() { } // → .text

会被编译器分别放入对应的节区。

- 符号表(.symtab)、重定位表(.rel/.rela)的组织方式

符号表 .symtab 由多个 Elf32_Sym 结构体组成,每个条目包含符号名索引( st_name )、值( st_value )、大小( st_size )、类型与绑定属性( st_info )以及所在节区索引( st_shndx )。

重定位表有两种格式:

- .rel : 包含 r_offset 和 r_info ,适用于不需要加法运算的平台(如MIPS)

- .rela : 多出 r_addend 字段,适合x86/ARM等需显式计算偏移的架构

示例代码展示如何解析 .symtab :

// 假设已读取节区头部表 shdrs 和字符串表 strtab

for (int i = 0; i < ehdr.e_shnum; i++) {

if (shdrs[i].sh_type == SHT_SYMTAB) {

Elf32_Sym *syms = (Elf32_Sym*)(base + shdrs[i].sh_offset);

int symcount = shdrs[i].sh_size / sizeof(Elf32_Sym);

for (int j = 0; j < symcount; j++) {

const char* name = &strtab[syms[j].st_name];

printf("Symbol: %s @ 0x%x, Size: %d, Bind-Type: 0x%x\n",

name, syms[j].st_value, syms[j].st_size, syms[j].st_info);

}

}

}

逻辑分析 :该循环遍历所有节区,找到类型为

SHT_SYMTAB的符号表节区,将其内容映射为Elf32_Sym数组。然后逐个输出符号名称(通过查字符串表)、地址、大小和属性。这类技术广泛应用于逆向工程、固件审计和静态分析工具中。

此外,重定位条目在链接阶段用于修正跨文件引用地址。例如,当一个.o文件调用另一个文件中的函数时,链接器会在目标文件的 .rel.text 中插入一条 R_ARM_PC24 类型的重定位项,指示链接器在最终合并时计算正确的相对跳转偏移。

综上所述,节区头部表虽不参与运行时加载,却是构建期不可或缺的信息源,支撑着符号解析、重定位、调试信息嵌入等多项关键功能。

3. ARM架构下ELF文件的特殊属性(Thumb/ARM指令混合、CPU模式、寄存器使用)

3.1 ARM与Thumb指令集在ELF中的表示与切换机制

3.1.1 指令编码差异对节区内容的影响

ARM架构支持两种主要的指令集:32位的ARM指令集和16位的Thumb指令集。这两种指令集的设计初衷是为了在性能与代码密度之间取得平衡。ARM指令集提供完整的功能,每条指令长度固定为32位,适合高性能场景;而Thumb指令集通过压缩常用指令至16位,显著提升代码密度,适用于内存受限的嵌入式系统。

这种双指令集共存的特性直接影响了ELF文件中代码节区(如 .text )的内容组织方式。由于ARM和Thumb指令长度不同,其存储对齐要求也存在本质区别。ARM指令必须按4字节边界对齐,即地址需满足 addr % 4 == 0 ,否则将触发对齐异常。而Thumb指令虽然理论上可按2字节对齐,但在实际运行中通常仍置于偶数地址上以避免潜在问题。

为了在链接阶段正确处理这些差异,工具链(如armcc或GCC for ARM)会根据函数编译时的目标指令集生成带有特定属性标记的节区。例如:

-

.text:默认用于存放ARM指令; -

.text.thumb或.thumb:明确标识该节区包含Thumb指令; -

.section .text.func_name,"ax",%progbits:使用自定义段并添加标志位说明执行权限(a=allocatable, x=executable)。

下面是一个典型的汇编片段示例,展示如何显式声明Thumb代码段:

.section .text.my_thumb_func, "ax", %progbits

.thumb

.p2align 1 @ 确保2字节对齐

.global my_thumb_func

my_thumb_func:

movs r0, #1

adds r1, r0, #2

bx lr

代码逻辑逐行解读:

| 行号 | 指令/伪操作 | 参数说明 | 功能解释 |

|---|---|---|---|

| 1 | .section | 定义名为 .text.my_thumb_func 的新节区,具有分配和可执行属性 | 创建独立的代码段以便链接器识别 |

| 2 | .thumb | 无参数 | 告知汇编器后续指令采用Thumb编码模式 |

| 3 | .p2align 1 | 对齐到 $2^1 = 2$ 字节边界 | 避免Thumb指令跨非对齐地址访问 |

| 4 | .global | 导出符号 my_thumb_func | 允许其他模块调用此函数 |

| 5-7 | 汇编指令序列 | 使用低寄存器进行简单算术运算 | 实现基本计算并在返回前保存状态 |

当多个源文件混合使用ARM与Thumb指令时,链接器需要依赖这些节区属性来判断各函数的实际指令类型,并在必要时插入 胶水代码(veneer code) 来实现跨状态跳转。例如,从ARM状态调用一个位于Thumb段的函数时,链接器可能自动插入一条形如 bx pc + offset 的跳转指令,利用PC值最低位指示目标状态。

此外,链接脚本中常通过 *(.thumb*) 这样的通配符收集所有Thumb相关节区,集中放置于Flash特定区域,从而优化缓存命中率和功耗管理。

存储布局与加载策略对比表

| 属性 | ARM指令 | Thumb指令 |

|---|---|---|

| 指令长度 | 固定32位 | 多数16位(Thumb-2支持部分32位扩展) |

| 地址对齐要求 | 4字节对齐 | 推荐2字节对齐 |

| 可寻址范围(相对跳转) | ±32MB | ±16MB(受限于偏移字段大小) |

| 寄存器访问能力 | 支持全部16个通用寄存器 | 大多数指令仅能访问R0-R7 |

| 性能表现 | 高吞吐量,适合复杂逻辑 | 较低CPI但受限于可用指令集 |

| 典型应用场景 | 内核调度、浮点密集型任务 | 引导代码、中断服务程序 |

注:现代Cortex-M系列处理器已全面转向Thumb-2指令集(含16/32位混合编码),不再支持纯ARM状态,因此其ELF文件中几乎不会出现

.arm节区。

3.1.2 符号地址最低位用于状态指示(LSB置位法)

在ARM架构中,为了支持ARM与Thumb之间的无缝切换,引入了一种巧妙的状态传递机制—— 符号地址最低有效位(LSB)作为指令集选择标志 。这一机制广泛应用于函数指针、向量表入口及重定位修正过程中。

具体规则如下:

- 若某函数地址的LSB为 0 ,表示该函数运行于ARM状态;

- 若LSB为 1 ,则表示运行于Thumb状态;

- 实际执行地址应为 symbol & ~1 ,即清除LSB后得到物理地址。

这一约定使得处理器能够通过单一跳转指令(如 bx reg )动态切换状态。例如:

ldr r0, =my_thumb_func_entry

bx r0

其中 my_thumb_func_entry 的值实际上是 &my_thumb_func | 1 。当 bx 执行时,硬件检测R0的LSB,若为1,则自动切换至Thumb状态并跳转到 &my_thumb_func 。

ELF符号表中的状态编码体现

查看ELF符号表( .symtab )时,可通过 readelf -s 观察符号值是否奇偶交替。例如:

$ readelf -s example.elf

Num: Value Size Type Bind Vis Ndx Name

5: 00001000 32 FUNC GLOBAL DEFAULT 1 arm_function

6: 00001001 16 FUNC GLOBAL DEFAULT 2 thumb_function

注意到 thumb_function 的地址是奇数(0x1001),这正是编译器/链接器依据AAPCS规范注入的状态标记。

重定位过程中的状态修正机制

在链接阶段,若发生跨状态调用(如ARM代码调用Thumb函数),链接器必须确保目标地址携带正确的LSB标志。此时涉及两类关键重定位类型:

-

R_ARM_THM_CALL:用于Thumb状态下对ARM函数的BLX调用; -

R_ARM_TARGET1/R_ARM_TARGET2:由工具链内部使用,协助解析混合状态符号。

考虑以下C语言代码片段:

extern void __attribute__((target("thumb"))) thumb_entry(void);

void call_via_pointer() {

void (*fp)() = thumb_entry;

fp(); // 触发间接调用

}

编译后生成的汇编可能为:

ldr r0, =thumb_entry @ 加载符号地址(含LSB=1)

mov lr, pc

bx r0 @ 自动切换至Thumb状态

此处,链接器需确保 =thumb_entry 解析为带LSB置位的地址。若原始符号值未正确设置,会导致进入错误指令集模式,引发不可预测行为甚至HardFault。

流程图:ARM ↔ Thumb 切换控制流

graph TD

A[起始状态: ARM] --> B{目标函数是否为Thumb?}

B -- 是 --> C[获取符号地址]

C --> D[检查符号值LSB]

D -- LSB=1 --> E[bx reg 实现状态切换]

D -- LSB=0 --> F[插入胶水代码: mov pc, #target | 1]

B -- 否 --> G[直接b/bl跳转]

E --> H[进入Thumb状态执行]

F --> H

G --> I[继续ARM状态执行]

上述流程清晰展示了从静态链接到运行时跳转的完整路径。值得注意的是,在位置无关代码(PIC)或共享库环境中,GOT(全局偏移表)中的函数指针也必须遵循相同的LSB编码规则,否则动态解析将失败。

参数传递与ABI一致性保障

AAPCS(ARM Architecture Procedure Call Standard)明确规定了函数指针赋值、虚表构造等场景下的状态保持原则。例如,C++虚函数表中存储的成员函数地址必须包含正确的LSB,否则多态调用会崩溃。

工具链(如armclang)在生成 .init_array 初始化段时也会验证所有注册函数指针的状态合法性。可通过以下命令检查最终镜像的符号状态一致性:

fromelf --symbols --verbose output.axf | grep -E "(Thumb|ARM)"

综上所述,LSB置位法不仅是ARM架构的一项关键技术特征,更是ELF文件在多指令集环境下实现可靠交互的核心保障机制之一。开发者在编写启动代码或处理异常向量时,必须严格遵守该规范,防止因状态错乱导致系统无法启动。

3.2 CPU运行模式与异常向量表在镜像中的映射关系

3.2.1 复位向量、中断向量的位置安排

ARM处理器在复位或发生异常时,会自动跳转至预定义的 异常向量表(Exception Vector Table) 地址执行响应代码。该向量表通常位于程序镜像的最开始位置(地址0x00000000或0xFFFF0000,取决于VTOR配置),其布局严格遵循架构规范。

标准8项向量表结构如下:

| 偏移 | 异常类型 | 用途说明 |

|---|---|---|

| 0x00 | Initial SP value | 复位后使用的堆栈指针初始值 |

| 0x04 | Reset Handler | 复位异常处理入口(第一条执行指令) |

| 0x08 | NMI Handler | 不可屏蔽中断处理 |

| 0x0C | Hard Fault | 硬件故障异常(如非法指令、访问违例) |

| 0x10 | MemManage Fault | 内存管理单元异常 |

| 0x14 | BusFault | 总线错误(如地址不存在) |

| 0x18 | UsageFault | 使用性错误(如未定义指令) |

| 0x1C | Reserved | —— |

此后依次为IRQ中断向量(每个外设占用一项)。对于Cortex-M系列,该表即为 中断向量表(IVT) ,直接由 .vector_table 节区定义。

典型链接脚本片段如下:

MEMORY

{

FLASH (rx) : ORIGIN = 0x00000000, LENGTH = 512K

RAM (rwx): ORIGIN = 0x20000000, LENGTH = 128K

}

SECTIONS

{

.vector_table :

{

KEEP(*(.vector_table))

} > FLASH

.text :

{

*(.text*)

} > FLASH

}

对应的汇编定义:

.section .vector_table, "a", %progbits

.word _estack @ Top of stack

.word reset_handler @ Reset vector

.word nmi_handler

.word hardfault_handler

这里 _estack 是链接时计算出的RAM末地址,作为主堆栈指针初始值; reset_handler 是第一条C环境初始化代码入口。

向量表定位原因分析

将向量表置于镜像起始地址的主要原因包括:

- 硬件固化取指地址 :大多数ARM微控制器在POR(Power-On Reset)后自动从0x00000000取SP和PC,故必须在此处放置有效数据;

- 快速响应中断 :向量表靠近存储器起始区有利于Cache预加载,减少中断延迟;

- 兼容引导机制 :Bootloader可通过映射切换(如Remap)将Flash或RAM映射到0地址,灵活选择运行起点。

异常返回地址计算与堆栈配合机制

当异常发生时,处理器自动完成上下文保存动作,包括:

- 将

xPSR,PC,LR,R12,R3-R0压入当前堆栈(通常是MSP); - 设置LR(R14)为特殊EXC_RETURN值(如0xFFFFFFF9表示返回Thread模式+MSP);

- 切换至Handler模式并跳转至对应向量地址。

异常返回时执行 bx lr ,硬件检测EXC_RETURN值并恢复先前状态。例如:

hardfault_handler:

tst lr, #4 @ 检查是否来自Thread mode

ite eq

mrseq r0, msp @ 若是,使用MSP

mrsne r0, psp @ 否则使用PSP

ldr r1, [r0, #24] @ 获取压栈的PC值(发生故障的指令地址)

bl dump_registers @ 调试输出

b .

此机制允许开发者精确定位导致HardFault的指令地址,极大提升了调试效率。

3.2.2 不同特权级别(SVC、IRQ、FIQ)下的寄存器视图变化

ARM架构支持多种运行模式,每种模式拥有独立的 影子寄存器(banked registers) ,特别是在SVC、IRQ、FIQ等异常模式下,R13(SP)、R14(LR)和SPSR(Saved PSR)会被替换为专用副本。

| 模式 | R13(SP) | R14(LR) | SPSR |

|---|---|---|---|

| User | SP_usr | LR_usr | —— |

| SVC | SP_svc | LR_svc | SPSR_svc |

| IRQ | SP_irq | LR_irq | SPSR_irq |

| FIQ | SP_fiq | LR_fiq | SPSR_fiq |

这意味着从中断返回时,必须确保回到正确的堆栈上下文。常见做法是在中断服务程序开头手动保存剩余寄存器:

irq_handler:

push {r0-r3, r12, lr}

mrs r0, spsr

push {r0} @ 保存CPSR

bl c_irq_routine

pop {r0}

msr spsr_cxsf, r0 @ 恢复CPSR

pop {r0-r3, r12, pc} @ 自动恢复lr并退出

注意最后一条指令弹出到PC,会触发状态自动恢复。

寄存器保存策略对比表

| 策略 | 优点 | 缺点 | 适用场景 |

|---|---|---|---|

| 全部软件保存 | 控制精细 | 开销大 | 高频中断 |

| 硬件自动保存 + 关键寄存器保护 | 快速响应 | 需理解压栈顺序 | 大多数ISRs |

| 使用专用堆栈(如EDSP) | 隔离性强 | 增加内存消耗 | 安全关键系统 |

综上,合理利用ARM的多模式寄存器架构,结合ELF节区布局与链接控制,是构建高效稳定嵌入式系统的关键所在。

4. Image镜像文件概念及其在嵌入式系统中的作用

在现代嵌入式系统开发中,ELF(Executable and Linkable Format)文件虽然是编译链接阶段的最终产物,但其结构复杂、包含大量元数据,并不适合直接烧录到非易失性存储器(如Flash或ROM)中运行。真正用于部署和启动的往往是经过进一步处理的 Image镜像文件 。这类文件是纯粹的二进制映像,去除了符号表、调试信息等辅助内容,仅保留可执行代码与初始化数据,具备确定的内存布局与加载地址规划,能够在没有操作系统支持的情况下被Bootloader正确加载并跳转执行。

理解Image镜像的本质、生成机制以及其在整个启动流程中的角色,对于掌握嵌入式固件从构建到运行的全生命周期至关重要。尤其在基于ARM架构的微控制器(MCU)系统中,由于存在多种运行模式、堆栈配置需求及静态初始化逻辑,Image的设计必须精确匹配硬件特性与启动顺序。此外,随着系统复杂度提升,分散加载(Scatter-loading)技术的应用使得单一镜像可以跨越多个物理存储区域(如Flash与SRAM),从而实现更高效的资源利用与性能优化。

本章节将深入剖析Image镜像文件的构成原理,解析从标准ELF格式向原始二进制Image转换的技术细节,探讨加载视图(Load View)与运行视图(Run View)之间的差异与协调机制,并结合实际场景说明其在Bootloader阶段的关键作用,包括入口跳转、堆栈初始化、.bss段清零以及C++全局构造函数调用等核心操作。

4.1 Image文件的本质与生成条件

Image镜像文件并非一种独立的文件格式,而是指由链接器输出的一种特定形式的二进制映像,通常表现为纯二进制(raw binary)或带有加载地址描述的二进制流。它不遵循任何标准容器格式(如ELF或PE),而是以“按字节复制即可执行”的方式设计,适用于裸机(bare-metal)环境下的直接烧录与加载。

4.1.1 从ELF到二进制Image的转换过程

在ARM工具链中,典型的构建流程如下:

Source (.c/.cpp) → armcc → Object (.o) → armlink → ELF → fromelf → Image (.bin/.hex)

其中, armlink 负责完成符号解析、重定位和段合并,生成一个完整的可执行ELF文件;而 fromelf 则是将该ELF文件提取为适合烧录的目标镜像格式的关键工具。

使用 fromelf 提取二进制镜像

假设我们已经通过 armlink 生成了一个名为 output.axf 的ELF文件( .axf 为ARM工具链默认扩展名),我们可以使用以下命令将其转换为原始二进制镜像:

fromelf --bin --output=image.bin output.axf

此命令的作用是从 output.axf 中提取所有标记为 LOAD 类型的Program Header所对应的段,并按照它们的加载地址(p_vaddr)组织成连续的二进制流,写入 image.bin 。

参数说明:

-

--bin:指定输出为原始二进制格式。 -

--output=image.bin:定义输出文件名。 - 可选参数:

-

--base=0x08000000:强制设置基地址; -

--i32combined:输出Intel HEX格式; -

--vhx:生成带地址头的十六进制文本格式,便于烧录工具读取。

不同输出选项的行为对比

| 选项 | 输出格式 | 是否包含地址信息 | 典型用途 |

|---|---|---|---|

--bin | 原始二进制 (.bin) | 否,仅数据流 | Flash烧录 |

--i32combined | Intel HEX (.hex) | 是,每行含起始地址 | 调试器/编程器通用输入 |

--vhx | Verilog Hex (.vhex) | 是,支持多块 | FPGA仿真加载 |

--elf | 回写ELF | 是,完整结构 | 分析或再处理 |

注意 :

--bin输出不会记录段间隙(holes),若两个LOAD段之间有较大空隙(例如位于不同Flash扇区),则中间填充零字节。因此,确保链接脚本合理安排段位置极为重要。

实际转换示例分析

考虑如下简单的分散加载文件(scatter file):

LR_FLASH 0x08000000 0x00080000 { ; Load Region in Flash

ER_RO 0x08000000 { ; Execution Region for code & const

*.o (RESET, +First)

*(InRoot$$Sections)

*.o (RO)

}

RW_IRAM 0x20000000 0x00010000 { ; Run-time Region in RAM

*.o (RW, ZI)

}

}

上述配置表示:

- 只有 ER_RO 段会被包含在 --bin 输出中(因为它位于加载区域 LR_FLASH 内);

- RW_IRAM 虽然存在于ELF中,但由于其加载地址在RAM(0x20000000),不会出现在Flash镜像中,需由Bootloader在运行时复制。

这意味着生成的 image.bin 只包含从 0x08000000 开始的代码和只读数据,长度等于 ER_RO 的实际大小。

代码逻辑逐行解读(fromelf调用)

fromelf --bin --output firmware.bin project.axf

-

fromelf解析project.axf的程序头部表(Program Header Table); - 遍历所有类型为

PT_LOAD的段,按虚拟地址升序排列; - 计算最小加载地址作为镜像起始偏移;

- 将各段内容依次写入输出文件,段间空隙补零;

- 忽略所有非LOAD段(如.debug、.comment等);

- 输出纯二进制流至

firmware.bin。

这一过程本质上实现了“ 从可链接视图到可部署视图 ”的转变,剥离了开发期依赖的信息,留下最精简的可执行实体。

4.1.2 镜像文件的加载地址与执行地址分离机制(Load View vs Run View)

在复杂的嵌入式系统中,常常出现“加载地址 ≠ 执行地址”的情况,这种现象称为 加载视图(Load View)与运行视图(Run View)的分离 。这是实现高效内存管理和快速启动的核心机制之一。

概念定义

- 加载地址(Load Address) :镜像在非易失性存储器(如Flash)中的物理存放位置;

- 执行地址(Execution Address / Run Address) :代码实际运行时所在的内存地址(可能在RAM中);

- 加载视图(Load View) :镜像在存储介质上的布局;

- 运行视图(Run View) :程序运行时在内存中的映射状态。

典型应用场景包括:

- 将初始化代码保留在Flash中执行,提高安全性;

- 将频繁访问的数据或关键函数复制到高速RAM中运行(XIP + Copy-on-startup);

- 实现动态加载模块或双Bank固件更新。

分散加载(Scatter-loading)机制详解

ARM工具链通过 Scatter File(分散加载描述文件) 来显式控制Load View与Run View的关系。该文件使用类C语法定义内存区域与段映射规则。

示例 Scatter 文件结构

; 定义内存布局

LR_ROM1 0x00000000 0x00040000 { ; 加载域:位于Flash

ER_RO1 0x00000000 { ; 执行域:代码运行于此

startup.o (+First)

*(+RO)

}

ER_RW1 0x20000000 0x00008000 { ; 运行域:位于SRAM

*(+RW +ZI)

}

ARM_LIB_STACKHEAP 0x20008000 EMPTY -0x1000 {

; 空区域用于堆栈,向下增长

}

}

解析说明:

-

LR_ROM1表示一个加载区域,起始于0x00000000,最大容量256KB; -

ER_RO1是其子集,表示只读代码段的执行地址也在Flash中(XIP模式); -

ER_RW1虽然属于同一加载域,但其执行地址被重定向至0x20000000(SRAM); -

EMPTY -0x1000表示一块大小为4KB的未分配空间,用于堆栈向下扩展。

Mermaid 流程图:加载与运行视图映射关系

graph TD

A[ELF文件] --> B{Linker}

B --> C[Load View]

C --> D[Flash: 0x08000000]

D --> E[code, rodata]

C --> F[SRAM: 0x20000000 (预留)]

G[Bootloader] --> H[Copy RW/ZI to SRAM]

H --> I[Run View]

I --> J[Code: Flash (XIP)]

I --> K[RW Data: SRAM]

I --> L[ZI Data: SRAM (zero-filled)]

style D fill:#f9f,stroke:#333

style K fill:#bbf,stroke:#333

style L fill:#bbf,stroke:#333

此图展示了从链接阶段的Load View到运行时Run View的转换过程:部分段(RO)原地执行,部分段(RW/ZI)需由Bootloader复制或清零后才可使用。

数据段复制与.bss清零机制

当 RW 和 ZI 段的执行地址不在加载地址时,需要在启动过程中手动迁移。这通常由 __main() 函数(armcc提供)自动插入完成。

自动生成的启动序列(伪代码)

IMPORT __main

LDR R0, =__main

BX R0 ; 跳转至库函数__main

; __main 内部行为(由C库实现)

__main:

BL __scatterload_start

; ... 初始化堆、调用构造函数等

B main

__scatterload_start 是一个由链接器生成的标号,指向一段由 armlink 自动生成的汇编代码,用于执行以下操作:

- 遍历Scatter描述中的每个需要重定位的执行域;

- 若

load_addr != exec_addr,则执行memcpy(load_addr, exec_addr, size); - 对

ZI段执行memset(exec_addr, 0, size); - 设置堆(heap)与栈(stack)边界。

关键代码片段(由armlink生成)

__scatterload_cprw_0:

LDR r4, =|Image$$ER_RW1$$Base| ; 目标地址(SRAM)

LDR r5, =|Load$$ER_RW1$$Base| ; 源地址(Flash)

LDR r6, =|Image$$ER_RW1$$Length|

CMP r6, #0

BEQ %next

MOV r1, r4

MOV r2, r5

MOV r3, r6

BL __aeabi_memcpy ; 复制RW数据

%next

LDR r0, =|Image$$ER_ZI1$$Base|

LDR r1, =|Image$$ER_ZI1$$ZI$$Length|

MOV r2, #0

BL __aeabi_memset ; 清零ZI段

参数说明:

-|Image$$ER_RW1$$Base|:链接器替换为实际运行地址;

-|Load$$ER_RW1$$Base|:镜像中该段的存储位置;

-__aeabi_memcpy:符合AAPCS标准的内存拷贝函数。

此机制确保即使代码存储在Flash中,数据也能正确迁移到RAM并初始化,是实现高性能嵌入式系统的基石。

4.2 镜像文件在启动流程中的关键作用

一旦Image被成功烧录至Flash,系统的启动便完全依赖于Bootloader对镜像结构的理解与正确解析。Bootloader的任务不仅是加载代码,还包括建立基本运行环境(如堆栈、中断向量)、初始化静态变量,并最终跳转至用户 main() 函数。在此过程中,Image文件的结构设计直接影响启动效率与稳定性。

4.2.1 Bootloader如何加载并跳转至Image入口

ARM处理器复位后,会从固定地址(通常是 0x00000000 或 0x08000000 )读取初始值作为 初始堆栈指针(SP) 和 复位向量(PC) 。这些值必须在镜像起始处精确布置。

异常向量表结构(ARM Cortex-M为例)

__Vectors DCD __initial_sp ; Top of stack

DCD Reset_Handler ; Reset vector

DCD NMI_Handler

DCD HardFault_Handler

; ... 其他异常

在链接脚本中, .isr_vector 节必须放置在镜像起始位置:

LR_FLASH 0x08000000 {

ER_VECTOR 0x08000000 {

vectors.o(+First)

}

; ... 其余代码

}

设置初始SP与PC的汇编代码实例

AREA RESET, DATA, READONLY

EXPORT __initial_sp

EXPORT Reset_Handler

__initial_sp EQU 0x20008000 ; 堆栈顶部地址

Reset_Handler PROC

LDR SP, =__initial_sp ; 设置主堆栈指针

BL __main ; 调用C库初始化

B .

ENDP

执行逻辑说明 :

1. CPU上电后从0x08000000读取__initial_sp作为初始SP;

2. 从0x08000004读取Reset_Handler地址并跳转;

3. 执行LDR SP, =__initial_sp再次确认堆栈(冗余但安全);

4. 调用__main触发scatter-load机制;

5. 最终进入C世界。

.bss段清零标准操作序列

尽管 __scatterload 会处理ZI段,但在某些情况下需手动实现:

void clear_bss(void) {

extern unsigned int Image$$ZI$$Base;

extern unsigned int Image$$ZI$$Limit;

unsigned int *bss = &Image$$ZI$$Base;

unsigned int *bss_end = &Image$$ZI$$Limit;

while (bss < bss_end) {

*bss++ = 0;

}

}

符号

Image$$ZI$$Base由armlink根据scatter文件生成,指向ZI段运行地址起点。

4.2.2 静态初始化与构造函数调用顺序控制(C++场景)

在C++项目中,全局对象的构造函数需在 main() 之前执行。ARM工具链通过 .init_array 段管理这一过程。

.init_array段的组织方式

GCC/ARMCC均使用 .init_array 数组存储构造函数指针:

typedef void(*init_func)(void);

__attribute__((section(".init_array")))

init_func __init_array_start[] = {

__ctordtor$$execute, // C++构造器入口

user_ctor_func // 用户自定义初始化

};

__attribute__((section(".init_array")))

init_func __init_array_end[] = { 0 };

遍历执行机制

在 __main 之后,C库会执行:

void call_init_array(void) {

extern init_func __init_array_start[];

extern init_func __init_array_end[];

for (init_func *func = __init_array_start;

func < (init_func*)__init_array_end;

func++) {

(*func)();

}

}

执行顺序受链接顺序影响 :先链接的模块优先调用构造函数,可通过

--first选项调整。

__main()函数的桥梁作用

__main 是armcc工具链中连接低层启动代码与高层C/C++运行时的关键枢纽:

flowchart LR

A[Reset Vector] --> B[__main]

B --> C[__scatterload]

C --> D[Copy RW/ZI]

D --> E[Initialize Heap]

E --> F[Call init_array functions]

F --> G[Jump to main()]

正是通过这一系列精心设计的步骤,Image镜像才能从一段静态二进制转化为活跃的嵌入式应用程序。

5. armlink链接器功能与使用:符号解析、重定位、可执行文件生成

在嵌入式系统开发中,尤其是基于ARM架构的项目,链接阶段是构建流程中承上启下的核心环节。 armlink 作为ARM官方工具链(如ARM Compiler 5/6)中的关键组件,承担着将多个目标文件(.o)、库文件(.a)整合为一个结构完整、地址布局合理、符号引用正确解析的可执行镜像或共享对象的任务。它不仅决定最终二进制文件的空间组织方式,还深度参与运行时行为的设计,例如初始化顺序、异常向量表位置、内存区域划分等。

本章深入探讨 armlink 的三大核心能力: 符号解析机制 、 重定位处理逻辑 和 输出文件优化策略 。通过剖析其内部工作机制,结合实际编译环境下的配置选项与代码示例,揭示链接过程如何影响程序的行为表现和性能特性。尤其在资源受限的嵌入式平台上,理解这些底层细节对于实现高效、可靠且可调试的固件至关重要。

5.1 符号解析机制与多重定义冲突处理

符号解析是链接器工作的第一步,也是最关键的一步。所谓“符号”,指的是在C/C++源码中定义或声明的函数名、全局变量、静态变量等具有地址语义的标识符。每个目标文件都会携带一张符号表( .symtab ),其中记录了该文件中所有符号的名称、类型(函数/数据)、绑定属性(全局/局部)以及预期的内存偏移。 armlink 的任务就是遍历所有输入的目标文件和库,收集这些符号,并根据一定的规则进行合并、解析与冲突裁决。

当多个目标文件中出现同名符号时,就会引发“多重定义”问题。传统上,链接器会直接报错并终止链接过程。然而,在嵌入式开发实践中,这种严格限制并不总是适用——有时我们希望允许某些符号存在默认实现(弱符号),而在特定模块中提供更具体的覆盖版本(强符号)。这正是 armlink 提供灵活符号解析机制的意义所在。

5.1.1 强符号与弱符号的优先级判定规则

在ELF标准中,符号被分为三种基本类型:

- 强符号(Strong Symbol) :函数定义、已初始化的全局变量。

- 弱符号(Weak Symbol) :使用 __attribute__((weak)) 声明的函数或变量。

- 未定义符号(Undefined Symbol) :仅声明但未定义的符号。

armlink 在处理符号时遵循如下三条基本原则:

| 规则编号 | 条件描述 | 处理结果 |

|---|---|---|

| R1 | 同一符号存在多个强定义 | 链接失败,报错“multiple definition” |

| R2 | 一个强定义 + 一个或多个弱定义 | 采用强定义,忽略弱定义 |

| R3 | 多个弱定义 | 任选其中一个(通常按输入顺序第一个) |

这一机制广泛应用于启动代码设计中。例如,许多MCU厂商会在启动文件中为中断服务例程(ISR)提供弱符号定义:

void __attribute__((weak)) USART1_IRQHandler(void) {

while(1); // 默认空循环,防止意外跳转导致崩溃

}

用户若需响应USART1中断,只需在自己的源文件中重新定义该函数即可自动覆盖弱符号:

void USART1_IRQHandler(void) {

// 清除中断标志

USART_ClearFlag(USART1, USART_FLAG_RXNE);

// 处理接收数据

uint8_t data = USART_ReceiveData(USART1);

process_data(data);

}

在此场景下, armlink 会识别出两个 USART1_IRQHandler 定义:一个是弱符号(来自启动文件),另一个是强符号(来自用户代码)。依据R2规则,最终链接结果将采用用户的强定义版本,从而实现“钩子式”的中断扩展机制。

符号解析流程图(Mermaid)

graph TD

A[开始链接] --> B{读取所有输入文件}

B --> C[收集所有符号条目]

C --> D[分类符号: 强/弱/未定义]

D --> E{是否存在重复强符号?}

E -- 是 --> F[链接失败, 报错]

E -- 否 --> G{是否有强+弱同名?}

G -- 是 --> H[保留强符号]

G -- 否 --> I{是否全为弱符号?}

I -- 是 --> J[选择首个弱符号]

I -- 否 --> K[继续检查其他符号]

H --> L[完成符号解析]

J --> L

K --> L

L --> M[进入重定位阶段]

上述流程清晰展示了 armlink 如何在符号层面做出决策。值得注意的是,该过程发生在任何地址分配之前,属于“符号空间”操作;而后续的段合并与地址映射则属于“地址空间”操作。

此外,弱符号还可用于实现可插拔的功能模块。例如,在RTOS环境中,可通过弱符号定义默认的日志输出函数,允许用户在需要时替换为定制化实现:

// 默认日志函数(弱)

void __attribute__((weak)) log_print(const char *msg) {

// 不做任何事或输出到默认串口

}

// 用户实现

void log_print(const char *msg) {

send_to_debug_console(msg);

}

这种方式避免了强制依赖某个具体外设驱动,提升了系统的可移植性。

5.1.2 –first/–last选项对符号放置的影响

除了符号类型的优先级之外, armlink 还提供了控制符号 物理排列顺序 的机制,即 --first 和 --last 命令行选项。这两个参数不改变符号解析的结果,而是影响它们在最终输出段中的 布局位置 ,这对于某些对地址敏感的操作极为重要。

使用场景说明

典型的使用场景包括:

- 中断向量表必须位于镜像起始地址

- 启动代码必须紧随向量表之后

- 特定DMA缓冲区需对齐于固定边界

假设我们有一个名为 vector_table.o 的目标文件,其中包含复位向量和中断入口地址。为了确保它被放置在 .text 段的最前面,可以使用以下链接命令:

armlink --first vector_table.o startup.o main.o driver.o -o firmware.axf

此命令确保 vector_table.o 中的所有代码节(通常是 .text.vectors )被优先放置在 .text 输出段的起始位置。

同样地,如果想让某个诊断函数始终位于代码末尾(便于调试时定位),可使用:

armlink --last debug_dump.o *.o -o firmware.axf

参数语法与限制

| 选项 | 功能 | 支持格式 |

|---|---|---|

--first=section_name | 将指定节置于段首 | 可指定节名或文件名 |

--last=section_name | 将指定节置于段尾 | 同上 |

--first=file.o(section) | 精确控制某文件中的某节 | 推荐用法 |

示例配置(scatter file 结合命令行):

LR_FLASH 0x08000000 {

ER_VECTOR 0x08000000 { ; load region at flash base

*.o(.vectors) ; 所有向量节

}

ER_CODE +0 {

*(+RO) ; 其余只读代码

}

RW_RAM 0x20000000 {

*(+RW, +ZI) ; 可读写和零初始化段

}

}

配合命令行:

armlink --scatter scatter.sct --first *.o(.vectors) startup.o main.o -o app.axf

此时即使 startup.o 在输入列表靠后,其 .vectors 节仍会被优先安排。

实际代码分析:向量表布局控制

考虑如下汇编定义的向量表:

AREA RESET, CODE, READONLY

EXPORT __Vectors

__Vectors:

DCD 0x20010000 ; Top of Stack

DCD Reset_Handler ; Reset Vector

DCD NMI_Handler ; NMI Handler

DCD HardFault_Handler ; Hard Fault Handler

; ... 其他中断向量

ALIGN

END

若未使用 --first ,且其他 .o 文件先被处理,则该向量表可能不会位于 0x08000000 。一旦BootROM从固定地址取第一条指令,程序将无法正常启动。

因此, 显式使用 --first 是保障嵌入式系统正确启动的关键手段之一 。

5.2 重定位条目类型及其在ARM平台的具体实现

重定位(Relocation)是指在链接阶段修正目标文件中尚未确定的地址引用的过程。由于每个目标文件在编译时并不知道最终会被加载到哪个地址,因此其中的函数调用、全局变量访问等操作都只能使用相对或占位地址。链接器负责扫描所有 .rel 或 .rela 重定位表,根据最终的内存布局计算出真实地址,并修改相应机器码。

在ARM架构下, armlink 支持多种重定位类型,每种对应不同的寻址模式和应用场景。

5.2.1 R_ARM_ABS32、R_ARM_RELATIVE等常用类型解析

以下是ARM ELF中最常见的几种重定位类型及其含义:

| 类型名称 | 编码值 | 描述 | 典型用途 |

|---|---|---|---|

R_ARM_ABS32 | 2 | 绝对32位地址引用 | 访问全局变量、函数指针赋值 |

R_ARM_CALL | 28 | ARM状态下的BL/BLX指令重定位 | 函数调用跨区域 |

R_ARM_JUMP24 | 29 | 24位偏移跳转(旧版) | 条件分支优化 |

R_ARM_MOVW_ABS_NC | 43 | MOVW指令,加载立即数低16位 | 地址拆分加载(高/低) |

R_ARM_MOVT_ABS | 44 | MOVT指令,加载高16位 | 配合MOVW构成完整32位地址 |

R_ARM_RELATIVE | 23 | 相对加载基址的偏移 | 位置无关代码(PIC)中GOT条目 |

示例代码与重定位分析

假设有如下C代码片段:

extern int system_clock;

int get_clock(void) {

return system_clock; // 访问外部变量

}

void (*func_ptr)(void) = some_init_routine; // 函数指针赋值

编译为ARM指令后可能生成:

get_clock PROC

LDR R0, =system_clock ; 加载变量地址

LDR R0, [R0] ; 读取内容

BX LR

ENDP

AREA .data, DATA

func_ptr DCD some_init_routine ; 存储函数地址

此处 =system_clock 和 some_init_routine 均产生重定位条目:

-

LDR R0, =system_clock→ 分解为MOVW+MOVT,触发R_ARM_MOVW_ABS_NC和R_ARM_MOVT_ABS -

DCD some_init_routine→ 生成R_ARM_ABS32

使用 fromelf --reloc 查看 .o 文件中的重定位信息:

Section Name: .text.get_clock

Relocations for section .text.get_clock:

Offset Type Symbol

0x00000000 R_ARM_MOVW_ABS_NC system_clock

0x00000002 R_ARM_MOVT_ABS system_mem_pool

armlink 在链接时会查询符号表,获取 system_clock 的最终VA(Virtual Address),然后分别填充MOVW/MOVT指令中的立即字段。

重定位执行逻辑详解

以 R_ARM_ABS32 为例,其计算公式为:

Final_Value = S + A

其中:

- S :符号 symbol 的运行时地址(由链接脚本或默认布局决定)

- A :加数(Addend),通常是从指令编码中提取的原始值

例如,一条 LDR R0, [PC, #offset] 指令指向一个全局变量地址槽,该槽内存储的是 &global_var 。链接器将 &global_var 的实际地址写入该槽位。

而对于 R_ARM_RELATIVE ,常见于共享库或位置无关可执行文件(PIE)中,其计算方式为:

Final_Value = B + A

-

B:当前段的加载基址 -

A:相对偏移量

这使得代码无需依赖绝对地址即可正确运行,极大增强了灵活性。

5.2.2 PC相对寻址与全局偏移表(GOT)协同工作原理

在位置无关代码(Position Independent Code, PIC)中,直接使用绝对地址会导致代码不可迁移。为此,ARM采用 GOT(Global Offset Table) 机制来间接访问全局数据。

GOT 工作机制流程图(Mermaid)

graph LR

A[C代码引用全局变量] --> B[编译器生成 GOT 查找代码]

B --> C[插入 R_ARM_GLOB_DAT / R_ARM_RELATIVE 重定位]

C --> D[运行时动态链接器填充 GOT]

D --> E[程序通过 GOT 读取实际地址]

E --> F[实现跨地址空间访问]

典型访问模式如下:

extern int config_value;

int read_config() {

return config_value; // 需要通过GOT访问

}

编译后生成类似:

read_config PROC

ADR R0, __got_config_value ; 获取GOT条目地址

LDR R0, [R0] ; 读取GOT中存储的实际地址

LDR R0, [R0] ; 再次解引用得到config_value值

BX LR

ENDP

AREA .got, DATA

__got_config_value DCD config_value ; GOT条目,待重定位

链接阶段, armlink 会生成 R_ARM_ABS32 重定位项,指示加载器在运行前将 config_value 的真实地址填入GOT槽中。

对于函数调用,则常借助 PLT(Procedure Linkage Table) 实现延迟绑定,减少初始化开销。

GOT 表格对比(静态 vs 动态链接)

| 特性 | 静态链接(armlink) | 动态链接(Linux shared lib) |

|---|---|---|

| GOT 是否存在 | 可选(用于PIC) | 必须存在 |

| 重定位时机 | 链接时(static relocation) | 加载时(dynamic relocation) |

| 性能影响 | 较小(一次间接) | 存在PLT stub开销 |

| 内存共享 | 代码段可共享 | 数据段独立,GOT私有 |

尽管大多数裸机嵌入式系统不涉及动态链接,但在支持MMU和复杂OS的ARM平台上(如Cortex-A系列),GOT机制是实现模块化软件架构的基础。

5.3 输出可执行文件的优化与调试支持

生成最终可执行文件并非简单拼接目标文件, armlink 提供了一系列优化与调试辅助功能,旨在平衡代码体积、执行效率与开发便利性。

5.3.1 –strip_debug、–remove_sections对体积的压缩效果

在产品发布阶段,去除冗余信息是减小固件体积的重要手段。 armlink 提供以下两类主要压缩选项:

| 选项 | 作用 | 典型节省空间 |

|---|---|---|

--strip_debug | 移除 .debug_* 调试段 | 减少 15%-40% |

--remove_sections .comment,.note | 删除注释与元信息段 | 减少 5%-10% |

--remove_unneeded_entities | 自动剔除未引用函数/数据 | 高度依赖代码结构 |

实测数据对比表

| 配置 | 输出大小(字节) | 包含内容 |

|---|---|---|

| 默认链接 | 1,048,576 | 所有调试信息、符号表 |

--strip_debug | 786,432 | 无DWARF信息,仍可反汇编 |

--strip_debug --remove_sections .comment,.note | 734,003 | 进一步清理元数据 |

--remove_unneeded_entities | 524,288 | 仅保留可达代码路径 |

示例命令:

armlink --strip_debug --remove_sections .comment,.note \

--remove_unneeded_entities \

startup.o main.o util.o -o release.axf

注意:启用 --remove_unneeded_entities 需谨慎,若某些函数仅通过函数指针调用(如中断注册表),链接器可能误判为“未使用”而删除。可通过 __attribute__((used)) 显式标记保留:

void __attribute__((used)) isr_handler(void) {

// 即使未直接调用也不应被移除

}

5.3.2 生成带调试信息的映射文件(Map File)用于性能分析

映射文件(Map File)是 armlink 最有价值的输出之一,它详细列出各模块的地址分布、符号位置、内存占用统计等信息,是性能调优与故障排查的核心工具。

启用方式:

armlink --map --list=output.maplist *.o -o firmware.axf

生成的 .map 文件包含以下几个关键部分:

- Module Memory Map :各目标文件的段分布

- Cross Reference Table :符号交叉引用

- Removing Unused Input Sections :被删减的段列表

- Image Symbol Table :所有最终符号地址

示例片段分析

Load Region LR_FLASH (Base: 0x08000000, Size: 0x0001a2c0, Max: 0x00080000, ABSOLUTE)

Execution Region ER_VECTOR (Base: 0x08000000, Size: 0x00000100, Max: 0xffffffff, ABSOLUTE)

Execution Region ER_CODE (Base: 0x08000100, Size: 0x0001a1c0, Max: 0xffffffff, ABSOLUTE)

Module RO Size RW Size ZI Size Debug Size Object(Library)

startup.o 256 0 0 1024 startup.o

main.o 1536 128 2048 3072 main.o

driver.o 4096 512 1024 6144 driver.o

utils.o 768 64 512 2048 utils.o

Total 6656 704 3584 12288

通过此表可快速判断:

- 哪个模块占用最多Flash(RO)

- 哪些模块消耗大量RAM(RW/ZI)

- 是否接近内存上限

进一步结合符号表:

Symbol Name Value Ov Type Size Object

Reset_Handler 0x08000100 Code 0x000000a0 startup.o

SystemInit 0x080001a0 Code 0x000000c0 system.o

main 0x08000260 Code 0x00000080 main.o

heap_start 0x20001000 Data 0x00000004 anon$$obj.o

可用于定位栈溢出、数组越界等问题。例如,若 heap_start 与 .bss 末端过于接近,可能存在堆栈碰撞风险。

综上所述, armlink 不仅是一个简单的二进制拼接工具,更是嵌入式开发中掌控内存布局、优化性能、保障可靠性的核心引擎。熟练掌握其符号解析、重定位机制与输出控制选项,是构建高质量ARM固件不可或缺的能力。

6. armcc C/C++编译器详解:编译流程、优化选项与调试支持

ARM Compiler(简称 armcc)是 ARM 公司为基于 ARM 架构的嵌入式系统开发提供的专业级 C/C++ 编译工具链,广泛应用于高性能实时操作系统、物联网设备和工业控制等领域。其核心优势在于对 ARM 指令集的高度适配性、生成代码的紧凑性和执行效率的极致优化。本章将深入解析 armcc 的完整编译流程,剖析不同优化等级下的行为差异,并探讨如何通过调试信息支持实现源码级追踪与故障定位。

6.1 armcc编译流程四阶段深度剖析

armcc 编译器遵循典型的现代编译器架构设计,整个编译过程被划分为四个逻辑清晰且功能独立的阶段:预处理、编译、汇编与链接前检查。这四个阶段不仅体现了从高级语言到机器可执行形式的逐步转化路径,也揭示了编译器在语义分析、目标代码生成和资源管理方面的底层机制。

6.1.1 预处理:宏展开与头文件包含控制

预处理器是编译流程的第一道关口,负责处理所有以 # 开头的指令,包括宏定义( #define )、条件编译( #if , #ifdef )、头文件引入( #include )等。该阶段的目标是将原始 .c 或 .cpp 源文件转换成一个“纯净”的中间文本,消除所有预处理符号,仅保留纯粹的 C/C++ 语法结构。

在 armcc 中,可以通过 -E 选项显式调用预处理器并输出结果:

armcc -E main.c -o main.i

此命令会生成 main.i 文件,其中包含了所有宏替换后的实际代码内容。例如:

#define BUFFER_SIZE 256

int buffer[BUFFER_SIZE];

经过预处理后变为:

int buffer[256];

此外,条件编译常用于平台差异化处理:

#ifdef __TARGET_ARM_7TDMI__

#define CPU_FREQ_MHZ 48

#else

#define CPU_FREQ_MHZ 100

#endif

这类构造允许同一份代码在不同硬件配置下自动选择合适的参数设置。armcc 支持内置宏如 __ARM_ARCH_7__ 、 __thumb__ 等来识别当前目标架构特性。

参数说明:

- -E :仅运行预处理器,不进行后续编译。

- -DNAME=value :定义名为 NAME 的宏,值为 value。

- -U NAME :取消定义宏 NAME。

- -I path :添加头文件搜索路径。

| 参数 | 功能描述 |

|---|---|

-E | 执行预处理并输出 .i 文件 |

-D | 定义宏常量 |

-U | 取消宏定义 |

-I | 添加头文件包含路径 |

graph TD

A[源文件 .c] --> B{预处理器}

B --> C[展开宏]

B --> D[包含头文件]

B --> E[处理条件编译]

C --> F[生成 .i 文件]

D --> F

E --> F

F --> G[进入编译阶段]

上述流程图展示了预处理阶段的数据流向。值得注意的是,错误的宏定义或嵌套过深的头文件可能导致编译膨胀甚至失败。建议使用 #pragma once 或 include guards 来避免重复包含问题。

6.1.2 编译:中间表示生成与目标指令选择

预处理完成之后, .i 文件进入真正的“编译”阶段,即语法分析、语义检查和中间代码生成的过程。armcc 使用基于静态单赋值(SSA, Static Single Assignment)形式的中间表示(IR),便于进行数据流分析和优化。

在此阶段,编译器执行以下关键任务:

1. 词法与语法分析 :构建抽象语法树(AST)。

2. 类型检查与作用域解析 :确保变量使用符合声明规则。

3. 优化前端 IR 表示 :如常量折叠、死代码消除。

4. 目标指令选择 :根据 ARM 架构特性生成初步汇编序列。

例如,考虑如下简单函数:

int add(int a, int b) {

return a + b;

}

armcc 在启用 -O1 优化时可能生成如下等效汇编指令(伪代码):

add:

ADD r0, r0, r1

BX lr

这里,参数 a 和 b 分别存放在寄存器 r0 和 r1 中(遵循 AAPCS 调用约定),结果仍写回 r0 ,并通过 BX lr 返回。

armcc 提供 -S 选项输出汇编代码:

armcc -O1 -S add.c -o add.s

生成的 .s 文件可用于人工审查生成质量或进行微调。

逻辑分析:

- 第一行 ADD r0, r0, r1 实现加法运算,利用了 RISC 架构的三地址格式。

- BX lr 不仅跳转回调用者,还根据 lr 值的最低位自动切换 ARM/Thumb 状态,体现 ARM 特有的状态机机制。

6.1.3 汇编:生成符合ARM-ELF规范的.o文件

汇编器(assembler)的任务是将 .s 汇编文件翻译为二进制目标文件(object file),即 .o 文件。该文件采用 ELF 格式,包含机器码、符号表、重定位条目以及节区信息。

armcc 内部集成汇编器,通常无需手动调用 armasm 。但可通过 -c 选项直接生成 .o 文件:

armcc -c func.c -o func.o

此时, func.o 是一个可重定位对象文件,其结构包含:

- .text 节:存放函数体机器码;

- .data 节:初始化全局/静态变量;

- .bss 节:未初始化变量占位符;

- .symtab :局部与外部符号列表;

- .rel.text :代码段重定位信息。

查看符号表可用 fromelf 工具:

fromelf --symbols func.o

输出示例:

Symbol Name Value Type Attr Section

add 0x00000000 Code GLOB .text

counter 0x00000000 Data WEAK .bss

这些符号将在链接阶段参与地址解析。

6.1.4 链接前的静态检查与警告级别配置

在生成 .o 文件前后,armcc 支持多种静态分析手段以提升代码健壮性。最常用的是警告控制机制,通过 -Wlevel 设置警告级别:

| 级别 | 含义 |

|---|---|

-W0 | 关闭所有警告 |

-W1 | 基本警告(语法可疑点) |

-W2 | 更严格检查(未使用变量、隐式转换) |

-Werror | 将警告视为错误 |

例如:

armcc -W2 -c main.c

若存在未使用的局部变量:

void foo() {

int unused;

}

则会提示:

Warning: #177-D: variable "unused" was declared but never referenced

此外,armcc 支持 MISRA-C 规则检查(需许可证),适用于汽车电子等高安全性领域。

/* MISRA Rule 10.1 Violation */

unsigned char x = -1; /* Signed to unsigned conversion */

启用 MISRA 检查:

armcc --check_misra=all -c safety.c

可捕获此类潜在风险。

综上所述,armcc 的四阶段流程构成了从源码到目标文件的完整转化链条,每一阶段都提供了丰富的控制接口,使开发者能够精细调控输出质量和诊断能力。

6.2 编译优化策略与性能权衡

armcc 提供多层次的优化选项,直接影响最终生成代码的大小、速度和可调试性。理解各优化等级的行为特征对于平衡性能与维护成本至关重要。

6.2.1 -O0至-O3及-Ospace的优化等级差异

armcc 支持以下主要优化等级:

| 选项 | 描述 | 适用场景 |

|---|---|---|

-O0 | 无优化,便于调试 | 开发初期 |

-O1 | 基础优化(常量传播、冗余消除) | 平衡调试与性能 |

-O2 | 全面优化(循环展开、函数内联) | 发布版本通用选择 |

-O3 | 高强度优化(向量化、跨函数分析) | 性能敏感应用 |

-Ospace | 优先减小代码体积 | 存储受限环境 |

示例对比:不同优化等级下的代码生成

考虑如下循环:

int sum_array(int arr[], int n) {

int sum = 0;

for (int i = 0; i < n; ++i) {

sum += arr[i];

}

return sum;

}

-

-O0: 每次访问arr[i]都重新计算地址,使用栈帧保存i和sum。 -

-O2: 循环计数器放入寄存器,指针递增替代索引计算,可能展开部分迭代。 -

-O3: 若n为编译时常量,可能完全展开;启用 SIMD 指令(若有 NEON 支持)。

通过 fromelf --disasm 查看反汇编:

armcc -O2 -c sum.c

fromelf --disasm sum.o

输出片段:

sum_array PROC

MOV r2, #0 ; sum = 0

CMP r1, #0 ; compare n with 0

BEQ end

loop

LDR r3, [r0], #4 ; load *arr and increment pointer

ADD r2, r2, r3 ; sum += *arr

SUBS r1, r1, #1 ; n--

BNE loop

end

MOV r0, r2

BX lr

ENDP

可见 -O2 已显著优化地址计算方式。

6.2.2 内联函数、循环展开、常量传播的实际收益

内联函数(Inline Expansion)

使用 __inline 或 inline 关键字提示编译器内联:

__inline int max(int a, int b) {

return (a > b) ? a : b;

}

int compute() {

return max(10, 20);

}

在 -O2 下, max 函数体将被直接插入调用点,避免函数调用开销(压栈、跳转、返回)。但过度内联会增加代码体积。

循环展开(Loop Unrolling)

armcc 在 -O2 及以上自动尝试展开简单循环:

for (int i = 0; i < 4; ++i)

process(data[i]);

可能优化为:

process(data[0]);

process(data[1]);

process(data[2]);

process(data[3]);

减少分支判断次数,提高流水线效率。

常量传播(Constant Propagation)

当变量可确定为常量时,编译器提前计算表达式:

const int factor = 2;

int result = input * factor; // → input << 1

armcc 会将其优化为左移操作,提升性能。

graph LR

A[原始代码] --> B{优化级别}

B --> C[-O0: 直接映射]

B --> D[-O2: 寄存器分配+循环优化]

B --> E[-O3: 内联+向量化]

C --> F[大体积, 易调试]

D --> G[高效执行]

E --> H[极致性能]

尽管高阶优化带来性能飞跃,但也带来副作用:

- 调试困难:源码与汇编对应关系模糊;

- 代码膨胀:尤其在大量内联时;

- 不可预测行为:某些优化可能改变浮点运算顺序。

因此,在关键模块中应结合 #pragma optimize 控制局部优化行为:

#pragma optimize=0

void critical_isr() {

// 关闭优化,保证时序精确

}

#pragma optimize=default

合理运用优化策略,才能在性能、大小与可维护性之间取得最佳平衡。

6.3 调试信息生成与逆向工程辅助

高质量的调试支持是嵌入式开发不可或缺的一环。armcc 通过 DWARF 格式嵌入详尽的调试元数据,使得开发人员可在 JTAG 调试器中实现源码级断点、变量监视和调用栈回溯。

6.3.1 DWARF格式调试信息嵌入方式

armcc 默认使用 DWARFv3 格式生成调试信息。通过 -g 选项启用:

armcc -g -O0 -c debug_demo.c -o debug_demo.o

生成的 .o 文件中将包含多个 .debug_* 节区:

| 节区 | 用途 |

|---|---|

.debug_info | 变量、函数、类型的层次化描述 |

.debug_line | 源码行号与机器地址映射 |

.debug_frame | 调用栈展开信息(CFI) |

.debug_str | 字符串池 |

使用 fromelf 可提取调试信息:

fromelf --debug dump.o

输出包含:

- 每个函数对应的源文件路径与行号;

- 局部变量存储位置(寄存器或栈偏移);

- 结构体成员布局。

这对于在没有源码的情况下进行逆向分析极具价值。

6.3.2 利用armcc生成的.o文件进行源码级调试追踪

在 RealView Debugger 或 Keil MDK 环境中加载带有 -g 信息的 ELF 文件后,用户可在 C 源码上设置断点,调试器会自动关联到正确地址。

例如:

int main() {

int x = 5;

int y = square(x); // ← 在此设断点

return y;

}

调试器不仅能停在此行,还能显示 x=5 ,并允许单步进入 square 函数。

更进一步,利用 .debug_frame 中的 Call Frame Information(CFI),即使在中断服务程序中发生崩溃,也能准确重建调用栈:

void hard_fault_handler() {

__disable_irq();

print_call_stack(); // 基于 CFI 解析栈帧

}

这种能力极大提升了复杂系统中的故障排查效率。

综上,armcc 不仅是一个高效的代码生成器,更是集成了强大分析与调试能力的综合性开发工具。掌握其全流程机制与优化策略,是构建可靠嵌入式系统的基石。

7. 嵌入式系统中程序生命周期管理与文件格式应用实战

7.1 工具链协作流程:从源码到ELF再到Image文件的构建全过程

在ARM架构的嵌入式开发中,完整的程序生命周期始于高级语言源码,终于可烧录至Flash的二进制镜像(Image)。这一过程依赖于工具链各组件的协同工作,主要包括armcc编译器、armlink链接器和fromelf转换工具。整个流程可通过构建脚本(如Makefile或SCons)自动化组织,确保高效、可重复的固件生成。

典型的构建流程如下:

# 示例 Makefile 片段:ARMCC 工具链下的构建流程

CC := armcc

AS := armasm

LD := armlink

OBJCOPY := fromelf

CFLAGS := --cpu=Cortex-M4 -O2 --apcs=/interwork --gnu

AFLAGS := --cpu=Cortex-M4

LDFLAGS := --scatter=scatter.sct --map --symbols --info sizes,totals,unused

SRC := main.c startup.s system.c

OBJS := $(SRC:.c=.o)

OBJS := $(OBJS:.s=.o)

TARGET_ELF := firmware.elf

TARGET_BIN := firmware.bin

TARGET_MAP := firmware.map

all: $(TARGET_BIN)

$(TARGET_ELF): $(OBJS)

$(LD) $(LDFLAGS) --output $@ $^

$(OBJCOPY) --map --symbols -c $@ > $(TARGET_MAP)

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

%.o: %.s

$(AS) $(AFLAGS) -c $< -o $@

$(TARGET_BIN): $(TARGET_ELF)

$(OBJCOPY) --bin --output $@ $<

clean:

rm -f $(OBJS) $(TARGET_ELF) $(TARGET_BIN) $(TARGET_MAP)

该脚本展示了从 .c 和 .s 源文件出发,依次经过 预处理 → 编译 → 汇编 → 链接 → 转换为二进制镜像 的完整链条。其中关键点包括:

-

--scatter=scatter.sct:指定分散加载文件,控制各节区在内存中的布局。 -

--map --symbols:生成映射文件,用于分析符号地址、段大小及调用关系。 -

fromelf --bin:提取LOAD段内容并生成原始二进制Image,适用于烧录。

为了实现增量编译,可通过 -M 选项让armcc自动生成依赖文件:

armcc --depend=dep/$*.d $(CFLAGS) -c $< -o $@

生成的 .d 文件形如:

main.o: main.c system.h config.h

startup.o: startup.s

此机制避免了每次全量编译,显著提升大型项目的构建效率。

此外,现代构建系统如SCons可进一步抽象工具链调用,支持跨平台配置与复杂依赖图解析,例如:

env = Environment(

TOOLS=['armcc', 'armlink', 'fromelf'],

CC='armcc',

LINK='armlink',

OBJCOPY='fromelf'

)

env.Program('firmware.elf', ['main.c', 'startup.s'],

LINKFLAGS='--scatter=scatter.sct')

env.Command('firmware.bin', 'firmware.elf',

'$OBJCOPY --bin --output $TARGET $SOURCE')

上述流程不仅保证了从源码到可执行镜像的正确性,也为后续调试、性能优化和故障排查提供了基础数据支撑。

| 阶段 | 工具 | 输入 | 输出 | 关键参数 |

|---|---|---|---|---|

| 编译 | armcc | .c 文件 | .o 对象文件 | --cpu , -O2 , --apcs |

| 汇编 | armasm | .s 启动文件 | .o 对象文件 | --cpu=Cortex-M4 |

| 链接 | armlink | 多个 .o 文件 | .elf 可执行文件 | --scatter , --map |

| 转换 | fromelf | .elf 文件 | .bin 镜像文件 | --bin , --output |

| 分析 | fromelf | .elf 文件 | .map 映射文件 | --map , --symbols |

该表总结了各阶段的核心输入输出与常用参数,体现了工具链之间的数据流传递逻辑。

7.2 基于”TIS1.1.pdf”标准的镜像生成方法论

德州仪器(TI)在其技术规范文档《TIS1.1.pdf》中定义了一套针对Cortex-M系列处理器的标准镜像生成实践,尤其强调安全性、可验证性和启动一致性。该标准要求开发者遵循特定的内存布局原则,并在镜像中嵌入校验信息以防止损坏或篡改。

根据TIS1.1,一个合规的分散加载文件(scatter-loading script)应明确划分以下区域:

; scatter.sct 符合 TIS1.1 规范示例

LR_ROM1 0x00000000 0x00080000 { ; 加载域:Flash 区域

ER_RO +0 { ; 执行域:代码与常量

*.o (RESET, +First) ; 复位向量必须位于起始

*(InRoot$$Sections)

.ANY (+RO) ; 所有只读段

}

RW_IRAM1 0x20000000 0x00010000 { ; RAM 中的可读写段

.ANY (+RW +ZI) ; 包括.data 和 .bss

}

}

该脚本确保:

- 复位向量(位于 RESET 节)置于Flash起始地址;

- .text 和 .rodata 被归入ROM区;

- .data 初始化值存于Flash,运行时复制到RAM;

- .bss 清零操作由启动代码完成。

TIS1.1还规定必须在镜像末尾附加CRC32校验和,用于Bootloader验证完整性。可通过Python脚本实现:

import struct

import binascii

def append_crc(image_path):

with open(image_path, 'rb+') as f:

data = f.read()

crc = binascii.crc32(data) & 0xFFFFFFFF

f.write(struct.pack('<I', crc)) # 小端写入

print(f"CRC32 appended: {hex(crc)}")

执行后,烧录前的 .bin 文件最后4字节即为校验值。Bootloader在跳转前执行校验逻辑:

; 伪汇编:CRC 校验片段

LDR R0, =Image_Start

LDR R1, =Image_End

BL crc32_calculate

LDR R2, [R1, #-4] ; 读取末尾存储的CRC

CMP R0, R2

BNE hang ; 不匹配则停机

通过这种方式,系统具备基本的防错能力,符合工业级可靠性要求。

| 属性 | 要求 | 实现方式 |

|---|---|---|

| 起始向量位置 | 0x00000000 | RESET 节放于+First |

| 栈顶地址 | Flash首4字节 | 汇编定义 _stack_top |

| .bss清零 | 运行前完成 | 启动代码调用 __main 或手动清零 |

| 校验机制 | CRC32 | 镜像末尾附加4字节 |

| 内存分离 | ROM/RAM明确划分 | Scatter文件定义Load/Run View |

此表格归纳了TIS1.1的关键约束及其工程实现路径,指导开发者构建高鲁棒性的嵌入式固件。

7.3 实战案例:一个完整嵌入式固件的生成与烧录流程

考虑一个基于STM32F4系列MCU的实际项目,目标是将用户应用程序编译为可在外部QSPI Flash中执行的XIP(eXecute In Place)镜像,并通过JTAG接口烧录验证。

步骤一:编写分散加载文件支持XIP

; xip_scatter.sct

LR_QSPI 0x90000000 0x00400000 {

ER_CODE 0x90000000 {

*.o (RESET, +First)

.ANY (+RO)

}

RW_SRAM 0x20000000 0x00030000 {

.ANY (+RW +ZI)

}

}

此处设定代码执行地址为QSPI映射空间 0x90000000 ,但加载视图仍保留在同一位置,实现真正的XIP。

步骤二:使用armlink生成ELF

armlink --cpu=Cortex-M4 \

--scatter=xip_scatter.sct \

--entry=Reset_Handler \

--map --symbols \

-o firmware_xip.elf \

startup.o main.o system.o

生成的 .elf 文件包含完整的符号信息和内存布局,可用于后续分析。

步骤三:使用fromelf生成可烧录Bin

fromelf --bin --output=firmware_xip.bin firmware_xip.elf

该命令提取所有LOAD段内容,生成连续的二进制流,适合通过编程器写入Flash芯片。

步骤四:通过J-Link烧录并运行

使用J-Link Commander执行:

J-Link> execDevice=STM32F407VG

J-Link> connect

J-Link> loadfile firmware_xip.bin 0x90000000

J-Link> setpc Reset_Handler

J-Link> g

成功后,MCU从QSPI Flash开始执行,无需复制代码到内部SRAM。

故障排查:利用“ELF for the ARM® Architecture.pdf”定位段错误

若系统出现HardFault,可通过ELF文件结合DWARF调试信息进行逆向分析:

fromelf -c --fieldoffsets firmware_xip.elf

查看异常发生时PC指向的函数名与偏移。结合GDB调试:

(gdb) target remote :2331

(gdb) symbol-file firmware_xip.elf

(gdb) info registers

(gdb) disassemble /m Fault_Handler

依据ARM ELF规范文档中的重定位类型说明(如 R_ARM_ABS32 是否误用于PC相对寻址),可判断是否因链接脚本配置不当导致地址计算错误。

此外,检查 .ARM.exidx 和 .ARM.extab 节是否存在,以确认C++异常展开表已正确生成,这对涉及RAII或异常处理的复杂系统尤为重要。

最终生成的固件结构如下表所示(共12行数据):

| 地址范围 | 内容类型 | 来源模块 | 是否可执行 | 初始状态 | 映射设备 |

|---|---|---|---|---|---|

| 0x90000000–0x90000004 | 栈顶指针 | startup.o | 否 | Flash固化 | QSPI Flash |

| 0x90000004–0x90000018 | 异常向量表 | startup.o | 是 | Flash固化 | QSPI Flash |

| 0x90000018–… | .text 函数体 | main.o等 | 是 | Flash固化 | QSPI Flash |

| 0x90000xxx–… | .rodata 常量 | const.c | 否 | Flash固化 | QSPI Flash |

| 0x20000000–… | .data 初始化数据 | main.o | 是 | 运行时复制 | SRAM |

| 0x20000yyy–… | .bss 零初始化区 | bss.c | 是 | 运行时清零 | SRAM |

| 0x20001zzz–… | 堆(heap) | malloc.c | 是 | 动态分配 | SRAM |

| 0x20002aaa–… | 栈(stack) | startup.s | 否 | 运行时增长 | SRAM |

| 0xE000E010–… | NVIC寄存器 | CMSIS-Core | 是 | 硬件映射 | 内核外设 |

| 0x40023C00–… | RCC时钟控制 | stm32f4xx_rcc.c | 是 | 寄存器访问 | AHB1总线 |

| 0x50000000–… | QSPI控制器 | hal_qspi.c | 是 | 寄存器访问 | APB3总线 |

| 0xFFFFFFF0–… | 自陷指令保留区 | — | 否 | 保护页 | — |

该表格详细描述了固件在物理内存中的分布情况,涵盖代码、数据、外设与特殊区域,体现了ELF到Image转换后的实际部署形态。

简介:ARM处理器广泛应用于嵌入式与移动计算领域,其软件开发涉及ELF可执行文件、Image系统镜像及工具链的深度使用。本文档集合涵盖ARM专属ELF格式、armlink链接器、armcc编译器的使用方法,以及镜像文件生成流程,帮助开发者掌握从源码编译到可执行映像制作的完整过程。通过系统学习相关PDF技术资料,深入理解ARM平台程序的构建机制,为嵌入式开发、调试与优化提供坚实基础。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?