简介:Makefile是Linux环境下的自动化构建工具,通过定义规则来编译和测试程序。本文将介绍Makefile的基本结构和常用指令,帮助初学者掌握如何编写和使用Makefile。通过一个简单的示例,我们将展示Makefile的组成和工作原理,并解释如何通过依赖关系的检查来更新目标文件。掌握Makefile是成为Linux开发者的必备技能,而这个简化版的Makefile能够为学习者提供构建管理的入门知识。

1. Makefile概念与重要性

在现代软件开发中,自动化构建工具扮演着至关重要的角色。作为其中的佼佼者,Makefile是一个包含了程序编译规则的文件,它告诉make程序如何编译和链接程序。Makefile在软件的构建过程中,能够自动化编译过程,提高开发效率,并确保构建的一致性与可靠性。

Makefile的必要性:

- 自动化构建: 定义编译、链接等规则,减少重复劳动。

- 依赖跟踪: 只编译修改过的文件,避免不必要的重复编译。

- 扩展性: 易于维护和扩展,适应项目变化。

理解Makefile的这些核心价值,是掌握其使用与优化的基石,为深入学习后续章节打下基础。在本章中,我们将首先探讨Makefile的基本概念与它在项目构建中的关键作用。随后,我们将深入到Makefile的结构、规则以及它在自动化构建和依赖管理方面的应用。

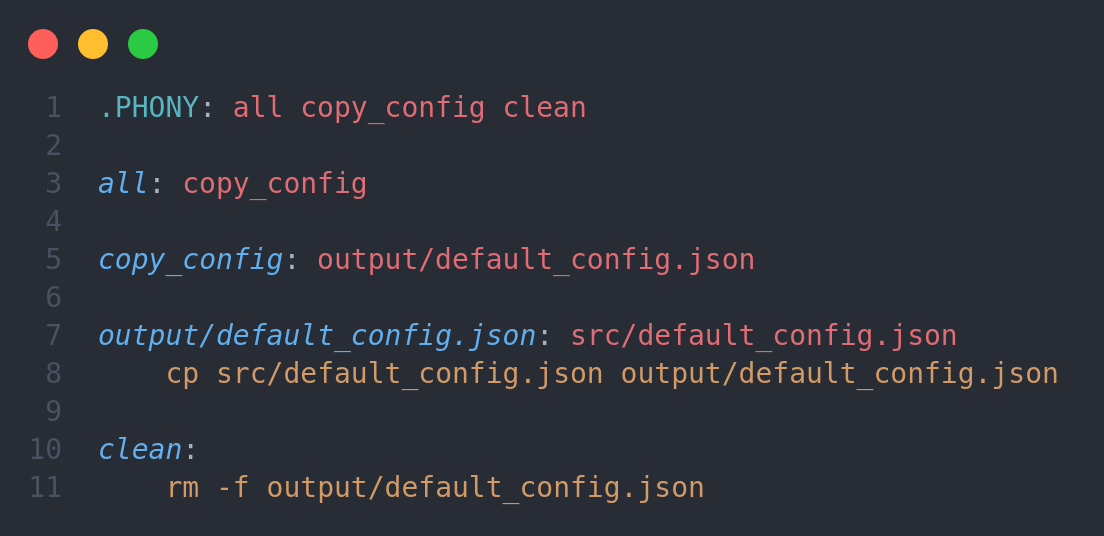

# 示例:简单的Makefile文件

CC=gcc

CFLAGS=-Wall

# 定义目标

all: hello

# 定义依赖和命令

hello: hello.o

$(CC) $(CFLAGS) -o hello hello.o

hello.o: hello.c

$(CC) $(CFLAGS) -c hello.c

clean:

rm -f *.o hello

以上示例展示了Makefile的基本结构,它包括了编译器设置、编译标志、目标和依赖定义以及编译和清理命令。通过这个简单的例子,我们可以初窥Makefile的魔力,而这仅仅是一个开始。随着文章的深入,我们将解锁更多Makefile的高级特性和最佳实践。

2. Makefile基本结构和组成

2.1 Makefile的规则

2.1.1 规则的基本语法

Makefile规则(rules)是构建过程的核心,它们定义了文件间的依赖关系,并指定了当依赖文件被更新时需要执行的命令。一条典型的Makefile规则包含三个部分:目标(target)、依赖(dependencies)和命令(commands)。

target: dependencies

commands

- 目标(target) 通常是需要生成的文件名,或者是一个执行的动作。

- 依赖(dependencies) 是生成目标所需的输入文件或其他目标。

- 命令(commands) 是一系列在依赖条件满足时执行的shell命令。

示例 :

app: main.o utils.o

gcc -o app main.o utils.o

上述规则声明了一个名为 app 的目标,它的依赖为 main.o 和 utils.o ,当这些依赖文件有更新时,会执行 gcc -o app main.o utils.o 命令来生成目标文件 app 。

2.1.2 通配符的使用

在Makefile中,通配符(wildcards)使得构建规则更加灵活和通用。常用的通配符包括 * 、 ? 和 [] 。

-

*匹配任意数量的字符。 -

?匹配任意单个字符。 -

[]匹配括号内的任意一个字符。

例如,如果你想编译当前目录下所有的 .c 文件为 .o 文件,可以使用如下规则:

objects = *.o

app: $(objects)

gcc -o app $(objects)

当添加或删除 .c 源文件时, *.o 会自动匹配到对应的 .o 文件,这样可以大大减少修改Makefile的工作量。

2.2 Makefile的内置变量

2.2.1 常用内置变量

Makefile提供了一些内置变量(built-in variables),这些变量可以在Makefile中直接使用,提高构建脚本的可移植性和可维护性。一些常用的内置变量包括:

-

CC:编译器的名称,默认为cc。 -

CFLAGS:传递给C编译器的选项。 -

CPPFLAGS:传递给C预处理器的选项。 -

LDFLAGS:传递给链接器的选项。 -

TARGET_ARCH:指定目标架构。

例如:

CC=gcc

CFLAGS=-Wall -g

LDFLAGS=-lm

app: main.o utils.o

$(CC) -o $@ $^ $(LDFLAGS)

在这个例子中, $@ 代表目标文件的名称, $^ 代表所有依赖文件的名称, $(LDFLAGS) 使用了内置变量。

2.2.2 变量的赋值与引用

在Makefile中,变量的赋值可以使用两种语法:递归赋值和简单赋值。

- 递归赋值 使用

=,值为变量引用的最终结果。 - 简单赋值 使用

:=,值为变量引用时的初始值。

此外,使用 ?= , 如果变量没有被赋值,那么它将被赋予指定的值。

示例 :

objects := main.o utils.o

app: $(objects)

gcc -o app $(objects)

这里, objects 使用了简单赋值, $(objects) 在使用时将被替换为 main.o utils.o 。

2.3 Makefile的模式规则

2.3.1 模式规则的定义与应用

模式规则(pattern rules)允许你为一组类似的目标文件定义单一的规则。一个模式规则看起来像是一个普通的规则,但是它的目标包含一个或多个 % 字符,这表示模式匹配。

格式 :

% : %.c

gcc -c $< -o $@

在这个模式规则中, % 代表任意的文件名, %.c 匹配任何 .c 文件, $< 表示第一个依赖, $@ 表示目标。

示例 :

%.o : %.c

gcc -c $< -o $@

这条规则定义了如何从 .c 文件编译出 .o 文件, % 匹配任意文件名。

2.3.2 模式规则与自动化变量

自动化变量是Makefile中的一个特殊变量,用于简化命令的书写,并使得规则更加通用。常用的自动化变量包括:

-

$@:目标文件的名称。 -

$<:第一个依赖文件的名称。 -

$^:所有的依赖文件的名称,以空格分隔。 -

$?:所有比目标新的依赖文件的名称,以空格分隔。

示例 :

%.o : %.c

gcc -c $< -o $@

在这个例子中, $< 代表第一个依赖的 .c 文件, $@ 代表生成的 .o 文件。当我们有多个 .c 文件需要编译时,这个模式规则会自动将每个 .c 文件编译成对应的 .o 文件。

main.o: main.c

gcc -c main.c -o main.o

utils.o: utils.c

gcc -c utils.c -o utils.o

如果没有模式规则,你将需要为每个 .c 文件编写一个目标和命令。模式规则大大简化了这个过程。

3. 目标(target)、依赖(dependencies)和命令(commands)

3.1 目标(target)的定义

3.1.1 目标文件的概念

目标是Makefile中的一个核心概念,它通常指代了需要生成的文件,比如编译过程中生成的可执行文件或库文件。Makefile中的每个目标都有一个名字,并且可以和依赖项以及命令相关联。目标的真正作用是定义了一组规则,告诉make如何根据依赖文件的更新情况来创建或更新它。

目标分为显式目标和模式目标:

- 显式目标 :通常是特定的文件名,如

clean或all等,显式目标可以是实际文件名,也可以是不对应任何文件的伪目标(phony target)。 - 模式目标 :通过模式规则定义,可以匹配一类文件,例如

%.o可以匹配所有以.o结尾的文件。

目标的定义遵循以下基本语法:

target: dependencies

[command]

[command]

...

这里, target 是目标的名称, dependencies 是目标所依赖的文件列表, [command] 是生成目标需要执行的命令序列。

3.1.2 多目标的定义与实践

在Makefile中定义多个目标是一个常见的实践,它允许多个目标文件共享相同的依赖和命令。这对于创建多个可执行文件或库文件时,可以节省重复代码,使Makefile更加清晰和易于维护。

多目标定义的示例:

all: prog1 prog2 prog3

prog1: prog1.o utils.o

cc -o prog1 prog1.o utils.o

prog2: prog2.o utils.o

cc -o prog2 prog2.o utils.o

prog3: prog3.o utils.o

cc -o prog3 prog3.o utils.o

在这个例子中, all 是一个伪目标,它依赖于三个程序文件 prog1 、 prog2 和 prog3 。每个程序文件都有相应的依赖文件和编译命令。 all 目标允许我们通过简单地调用 make all 来编译所有程序。

3.2 依赖(dependencies)的管理

3.2.1 依赖关系的建立

依赖关系是Makefile中用于定义目标更新规则的另一种重要方式。依赖关系能够描述出目标的生成过程,其中依赖项代表目标生成所需的所有输入文件。当一个目标依赖的某个文件更新后,目标也会被认为是过时的,需要重新生成。

依赖关系的定义遵循以下格式:

target: dependency1 dependency2 ...

依赖项可以是其他目标,也可以是普通的文件。如果目标是最新的,那么make不会执行任何命令;如果任何依赖项比目标更新,make将执行与目标相关联的命令。

3.2.2 自动依赖检测技巧

自动依赖检测是Makefile中用于简化构建过程的一个高级技巧。它能够减少维护者对依赖关系更新的手动干预,特别是在大型项目中,手动维护依赖关系可能会非常繁琐。

自动依赖检测的实现通常会借助一些工具,如gcc的 -M 或 -MM 参数,这些参数可以让编译器自动分析源文件所依赖的头文件。另外,一些现代的构建系统如CMake、Meson等,也提供了更加强大的依赖检测和管理机制。

示例代码:

CFLAGS += -I./include

CFLAGS += -MMD -MP

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

这里,我们使用了 -MMD (生成 .d 文件)和 -MP (为每个目标生成一个占位符目标)选项,这样make可以通过读取 .d 文件来自动生成依赖关系。

3.3 命令(commands)的执行

3.3.1 命令的书写规则

Makefile中的命令用于实际执行构建过程,它们通常被放置在目标下,并且以Tab字符作为开头。命令会按顺序执行,除非出现错误,一旦命令执行失败,make会停止执行后续的命令。

书写规则:

- 命令必须以Tab字符开头。

- 每条命令都独立于新行。

- 命令可以使用make内置的变量和函数。

- 一个目标下的多条命令是顺序执行的,如果需要并行执行,可以使用

make -j参数。

3.3.2 命令的执行顺序与错误处理

在Makefile中,同一目标下的多个命令是顺序执行的。如果目标正在执行第一个命令时出现错误,make将不会执行后续的命令,而是将该目标视为未成功构建。

错误处理可以通过特殊的变量或特殊符号来实现,例如使用 - 前缀可以让make忽略命令的错误:

target:

-command1

-command2

...

如果 command1 或 command2 失败,make不会停止,它会继续执行列表中的其他命令。

表格与代码块

下面的表格展示了Makefile中常见的一些命令及其作用:

| 命令 | 作用 |

|---|---|

cc | 调用C编译器 |

gcc | 调用GCC编译器 |

ar | 创建静态库 |

rm | 删除文件 |

echo | 打印信息 |

下面是一个简单的Makefile代码块,它展示了如何编译一个C程序:

CC=gcc

CFLAGS=-Wall

main: main.o utils.o

$(CC) -o main main.o utils.o

main.o: main.c utils.h

$(CC) $(CFLAGS) -c main.c -o main.o

utils.o: utils.c utils.h

$(CC) $(CFLAGS) -c utils.c -o utils.o

clean:

rm -f main main.o utils.o

在这个例子中, main 是最终要生成的可执行文件,它依赖于 main.o 和 utils.o 。而这两个 .o 文件又各自依赖于相应的 .c 源文件和 utils.h 头文件。 clean 是一个伪目标,用于清理编译生成的文件。

mermaid流程图

下面是一个简单的mermaid格式流程图,它展示了Makefile的基本执行流程:

graph LR

A[开始] --> B[检查目标]

B --> C[读取Makefile]

C --> D[执行命令]

D --> E[生成目标]

E --> F[结束]

这个流程图简要地描述了make执行时会经历的主要步骤,从开始到结束,包括检查目标、读取Makefile、执行命令以及最终生成目标文件。

4. 实例解析Makefile实例

4.1 基本Makefile实例解析

4.1.1 单个源文件的编译

为了理解Makefile在实际项目中的基本应用,让我们从一个简单的例子开始:单个源文件的编译。这将帮助我们理解Makefile如何组织和自动化编译过程。

假设我们有一个名为 hello.c 的C语言源文件,我们想要编译它生成可执行文件。下面是一个简单的Makefile实例:

all: hello

hello: hello.o

gcc hello.o -o hello

hello.o: hello.c

gcc -c hello.c

clean:

rm -f hello.o hello

在这个Makefile中,我们定义了三个目标: all 、 hello 和 hello.o 。 all 是一个伪目标,常用于作为默认目标,以便在没有指定目标时执行。 hello 目标负责将 hello.o 对象文件链接成最终的可执行文件。 hello.o 目标则负责将源文件 hello.c 编译成对象文件。

clean 目标是一个典型的清理目标,用于删除所有编译生成的文件,以便我们可以重新开始一个干净的编译过程。

4.1.2 多文件项目的构建

对于包含多个源文件的项目,Makefile需要列出所有依赖关系,并且自动识别和编译那些被修改过的文件。以一个简单的C语言项目为例,该项目包括两个源文件 main.c 和 utils.c ,以及一个头文件 utils.h 。

CC=gcc

CFLAGS=-Wall

OBJ=main.o utils.o

TARGET=project_name

all: $(TARGET)

$(TARGET): $(OBJ)

$(CC) -o $(TARGET) $(OBJ) $(CFLAGS)

main.o: main.c utils.h

$(CC) -c main.c $(CFLAGS)

utils.o: utils.c utils.h

$(CC) -c utils.c $(CFLAGS)

clean:

rm -f $(OBJ) $(TARGET)

在这个Makefile中,我们使用变量 CC 来指定编译器, CFLAGS 用于传递编译选项,如开启所有警告,而 OBJ 变量用于存储所有的对象文件。 $(TARGET) 是我们要生成的最终可执行文件。

每个 .o 目标都依赖于相应的 .c 源文件和 .h 头文件。注意,使用 -c 标志告诉编译器我们想要生成对象文件,而不是直接链接成可执行文件。

现在,如果 utils.c 被更新了,只需运行 make 命令,Makefile将只会重新编译 utils.c 和相关的头文件,然后链接更新后的对象文件来生成新的可执行文件。这比手动编译每个文件要高效得多。

4.2 复杂Makefile实例解析

4.2.1 条件编译与配置

在复杂的项目中,可能需要根据不同的条件来编译源代码,例如不同的操作系统、编译器选项或者调试标志。Makefile支持条件判断,这可以在Makefile中实现条件编译。

下面是一个使用条件判断的例子,该例子根据不同的操作系统定义了不同的编译参数:

# 检测操作系统

UNAME := $(shell uname)

ifeq ($(UNAME), Linux)

CFLAGS += -DLINUX

else ifeq ($(UNAME), Darwin)

CFLAGS += -DOSX

else

CFLAGS += -DOTHER

endif

all: my_program

my_program: main.o

gcc main.o $(CFLAGS) -o my_program

main.o: main.c

gcc -c main.c $(CFLAGS)

clean:

rm -f main.o my_program

在这个Makefile中,我们首先使用 uname 命令来获取当前的操作系统信息,并将其存储在 UNAME 变量中。然后,使用 ifeq 指令来设置不同的 CFLAGS 。这些标志可以在源代码中被检测,从而允许条件编译。

4.2.2 库文件的链接与使用

在许多项目中,我们不仅需要编译源代码,还需要链接一个或多个库文件。Makefile能够处理库文件链接,并且可以指定库文件的搜索路径。

以下是一个使用静态库 libutils.a 的Makefile示例:

CC=gcc

CFLAGS=-Wall -I./includes

LDFLAGS=-L./libs

LDLIBS=-lutils

OBJ=main.o

TARGET=program

all: $(TARGET)

$(TARGET): $(OBJ)

$(CC) $(LDFLAGS) -o $(TARGET) $(OBJ) $(LDLIBS)

main.o: main.c utils.h

$(CC) $(CFLAGS) -c main.c

clean:

rm -f $(OBJ) $(TARGET)

在这个Makefile中, LDFLAGS 变量用于指定库文件的搜索路径,而 LDLIBS 变量用于指定要链接的库。在这个例子中,我们假设有一个名为 libutils.a 的静态库文件位于 ./libs 目录下,它在链接时需要被指定。

当运行 make 命令时,Makefile会确保 main.o 被编译,并且链接了 libutils.a 库,生成名为 program 的可执行文件。

通过这些实例解析,我们可以看到Makefile在自动化编译和链接过程中如何发挥作用,以及如何在复杂项目中管理和组织构建过程。在下一章节中,我们将探讨如何利用Makefile实现更高级的自动化构建和依赖检查。

5. 自动化构建与依赖检查

5.1 自动化构建的流程与策略

5.1.1 自动化构建的概念

自动化构建是将代码从版本控制系统检出到生成最终产品(如可执行文件、软件包等)的整个过程自动化。通过自动化工具,如Makefile,可以减少重复劳动,提高开发效率,并减少人为错误。自动化构建流程通常包括代码清理、编译、链接、测试、打包等多个步骤。

5.1.2 自动化构建的实现步骤

实现自动化构建通常需要遵循以下步骤:

1. 环境准备 :确保构建环境满足软件运行的所有依赖要求。

2. 源码获取 :从版本控制系统中检出最新的源代码。

3. 依赖处理 :解析Makefile中声明的外部依赖,并自动下载或更新。

4. 编译构建 :使用编译器根据Makefile中的规则生成目标文件。

5. 链接生成 :将目标文件链接成最终的可执行文件或库文件。

6. 自动化测试 :运行测试用例,确保代码质量符合预期。

7. 产品打包 :将编译生成的产品进行打包,生成部署包。

8. 部署 :将打包的产品部署到测试或生产环境。

5.2 Makefile中的依赖检查

5.2.1 依赖检查的重要性

依赖检查是自动化构建的核心部分之一,它确保所有的依赖都是最新的,从而避免在构建过程中使用过时或不完整的目标文件。依赖检查通常在Makefile中通过比较依赖文件和目标文件的时间戳来执行,如果依赖文件比目标文件新,那么就会执行相关的构建命令。

5.2.2 依赖检查的高级技巧

依赖检查可以使用一些高级技巧来优化构建过程:

1. 使用自动化变量 :利用 $< (第一个依赖)、 $@ (目标文件)等自动化变量简化命令。

2. 条件判断 :使用 ifeq 或 ifneq 进行条件判断,根据不同的条件执行不同的命令。

3. 伪目标 :定义伪目标 .PHONY 来强制执行特定的构建规则,即使存在同名的文件。

4. 模式规则 :使用模式规则来定义通用的构建规则,减少规则的重复编写。

例如,以下是一个使用模式规则和自动化变量进行依赖检查的Makefile片段:

# 定义编译器和编译选项

CC=gcc

CFLAGS=-Wall

# 定义目标文件和依赖文件

objects = main.o utils.o

target = myprogram

# 定义伪目标,强制重新构建

.PHONY: all

# 使用模式规则简化编译命令

%.o: %.c

$(CC) $(CFLAGS) -c $< -o $@

# 链接目标文件生成最终程序

all: $(target)

$(target): $(objects)

$(CC) $(objects) -o $@

# 清理中间文件的规则

clean:

rm -f $(objects) $(target)

# 默认构建目标

default: all

通过这个Makefile片段,我们可以看到如何使用模式规则来简化对每个源文件的编译命令,并定义了 clean 伪目标来清除构建过程中的中间文件。这样的自动化构建过程大大提高了开发效率,并确保了构建的一致性和可重复性。

简介:Makefile是Linux环境下的自动化构建工具,通过定义规则来编译和测试程序。本文将介绍Makefile的基本结构和常用指令,帮助初学者掌握如何编写和使用Makefile。通过一个简单的示例,我们将展示Makefile的组成和工作原理,并解释如何通过依赖关系的检查来更新目标文件。掌握Makefile是成为Linux开发者的必备技能,而这个简化版的Makefile能够为学习者提供构建管理的入门知识。

337

337

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?