周末也发一天

一、九大PCB设计规则

随着信号上升沿时间的减小及信号频率的提高,电子产品的EMI问题越来越受到电子工程师的关注,几乎60%的EMI问题都可以通过PCB设计来解决,以下是九大规则:

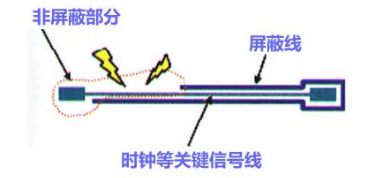

规则一:高速信号走线屏蔽规则

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

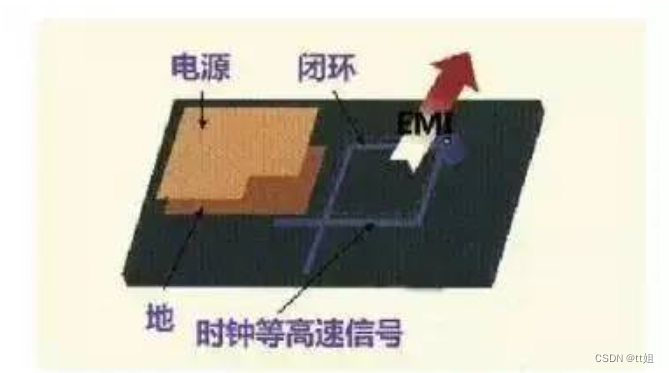

规则二:高速信号的走线闭环规则

由于PCB板的密度越来越高,很多PCB LAYOUT工程师在走线的过程中,很容易出现一种失误,即时钟信号等高速信号网络,在多层的PCB走线的时候产生了闭环的结果,这样的闭环结果将产生环形天线,增加EMI的辐射强度。

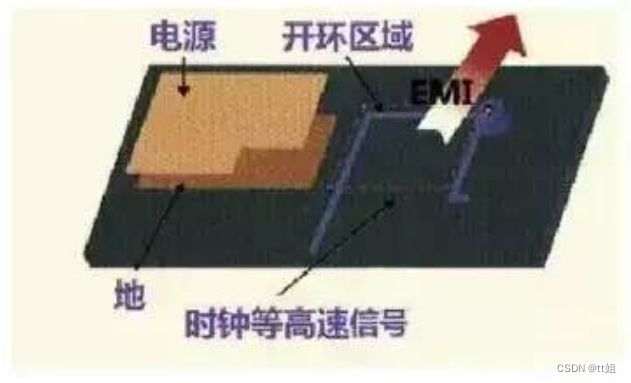

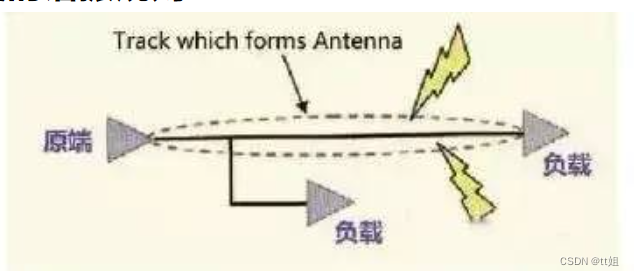

规则三:高速信号的走线开环规则

规则二提到高速信号的闭环会造成EMI辐射,然而开环同样会造成EMI辐射。

时钟信号等高速信号网络,在多层的PCB走线的时候一旦产生了开环的结果,将产生线形天线,增加EMI的辐射强度。

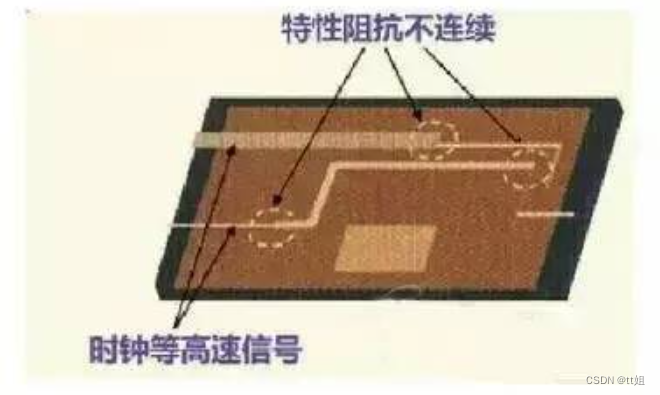

规则四:高速信号的特性阻抗连续规则

高速信号,在层与层之间切换的时候必须保证特性阻抗的连续,否则会增加EMI的辐射。也就是说,同层的布线的宽度必须连续,不同层的走线阻抗必须连续。

规则五:高速PCB设计的布线方向规则

相邻两层间的走线必须遵循垂直走线的原则,否则会造成线间的串扰,增加EMI辐射。

简而言之,相邻的布线层遵循横平竖垂的布线方向,垂直的布线可以抑制线间的串扰。

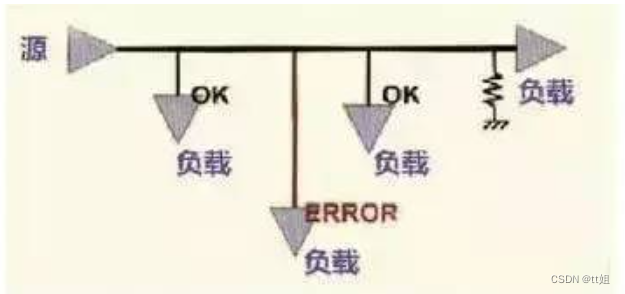

规则六: 高速PCB设计中的拓扑结构规则

在高速PCB设计中,线路板特性阻抗的控制和多负载情况下的拓扑结构的设计,直接决定着产品的成功还是失败。

图示为菊花链式拓扑结构,一般用于几Mhz的情况下为益。高速PCB设计中建议使用后端的星形对称结构。

规则七:走线长度的谐振规则

检查信号线的长度和信号的频率是否构成谐振,即当布线长度为信号波长1/4的时候的整数倍时,此布线将产生谐振,而谐振就会辐射电磁波,产生干扰。

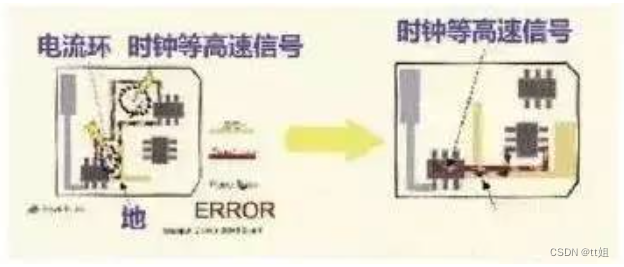

规则八:回流路径规则

所有的高速信号必须有良好的回流路径。尽可能地保证时钟等高速信号的回流路径最小。否则会极大的增加辐射,并且辐射的大小和信号路径和回流路径所包围的面积成正比。

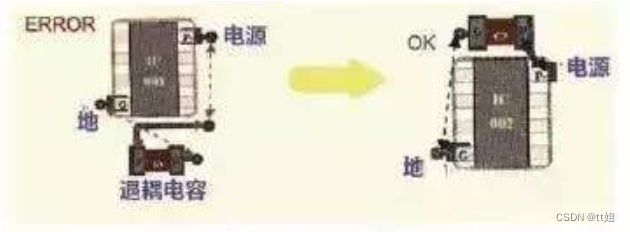

规则九:器件的退耦电容摆放规则

退耦电容的摆放的位置非常的重要。摆放不合理根本起不到退耦的效果。其原则是:靠近电源的管脚,并且电容的电源走线和地线所包围的面积最小。whaosoft aiot http://143ai.com

二、用STM32来DIY示波器

示波器是我们工程师的眼睛,首先我们要知道被我们“眼睛”观察的对象 - 电信号是什么?都有哪些不同的形式?就像我们人还需要用“大脑”对“眼睛”看到的现象做分析,我们也需要对用示波器看到的电信号做分析,进而判断出电路的性质,这就要求我们知道不同的电信号各有哪些典型特征?了解了这些,我们才可以通过现象看本质。

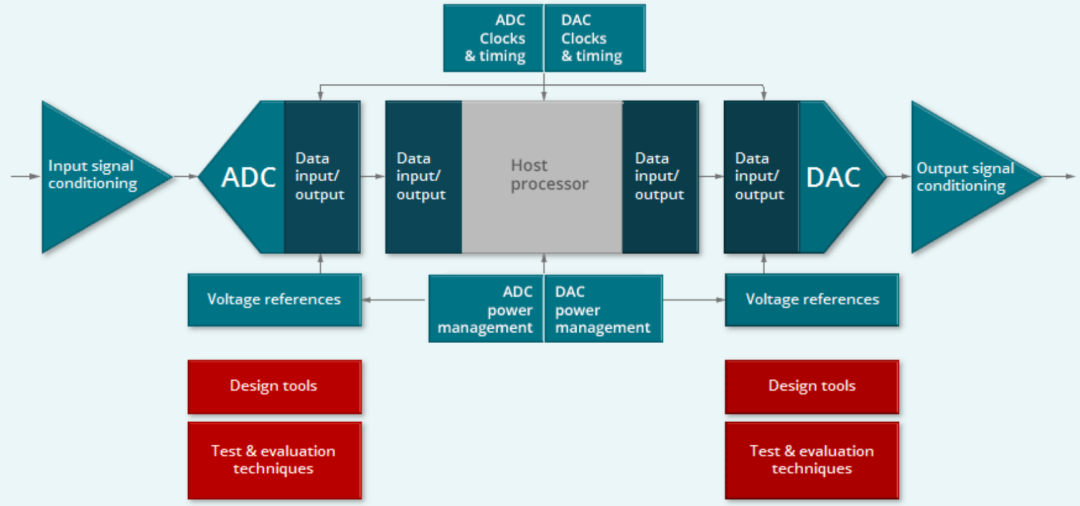

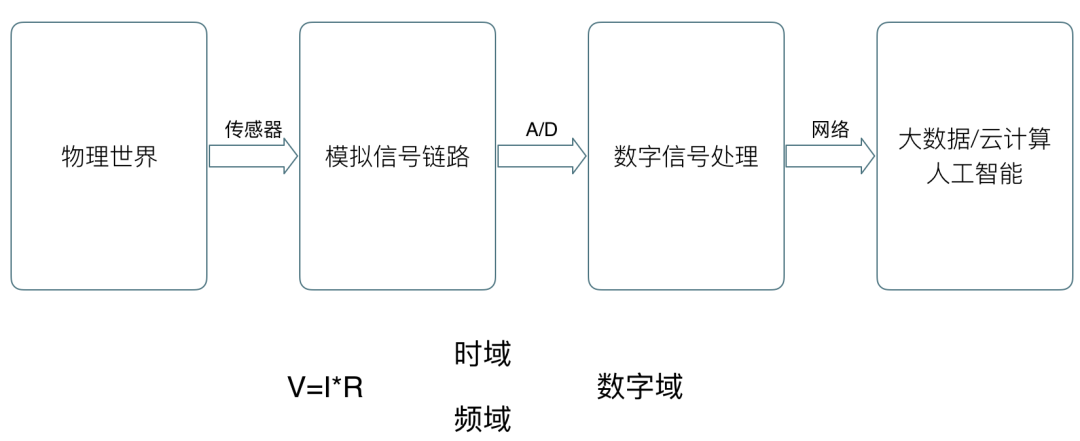

这是一个典型的电子产品系统:

在这个系统的每个环节都是通过电信号来表达和传递信息:

在A/D之前,电信号是以连续的模拟量的方式存在 - 它的幅度和频率都在传递信息,在A/D之后,电信号以分立的数字量的方式存在。

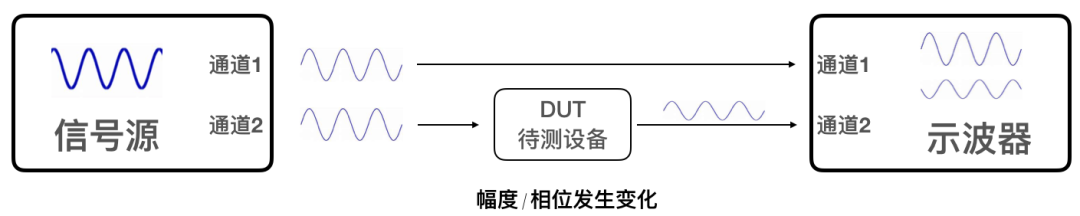

作为一个“诊断”电信号的仪器,示波器主要通过对比信号源的某种信号经过“待测设备(DUT)”之后的形态和不经过这个待测设备的形态之间的差异 - 比如某些成分的幅度发生了变化、相位/频率发生了变化,进而判断“待测设备”是否工作正常,以及定标待测设备究竟会起到什么作用。

因此,信号源也是测试测量系统的必备,即便平时在我们的测试中没有用到信号源,实际上我们也是假设了已经有信号源的存在,比如检测时钟是否工作正常,信号源已经在PCB板上;检测3.3V的电源电压是否正常,是否有纹波,信号源就是那个能够产生3.3V电压的LDO或开关稳压器。

当然,多数情况下我们需要对被测试的电路提供一个激励信号,比如:

- 提供模拟波形 - 正弦波(最常用)、三角波、方波

- 某种模式的数字信号

- 调制信号

- 刻意产生的噪声

通过这些激励信号能够:

- 检查每一级电路的增益、频率响应,对接收端进行校准

- 提供用于测试电路的各种波形,一般来讲都是低功率的

- 验证( Verification) - 分析数字调制

- 定标(Characterization)- 测试D/A和A/D转换器

- 压力/临界点 测试 - 通信接收机的压力测试

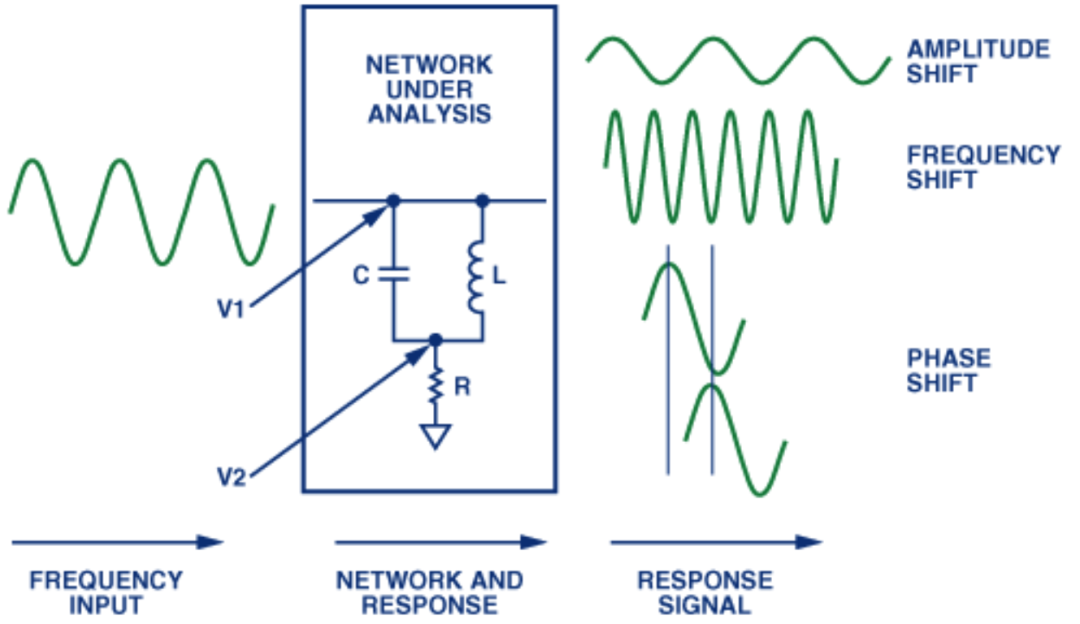

其实原理非常简单,下面的一张图就能直观表达出来:

信号源提供一个单频的电信号送给被测试的电路网络,用示波器观察经过这个网络以后的电信号,跟信号源的激励信号对比,就可以分析出被测电路的特性,单频的电信号只有两个参量 - 电压和相位(或频率),通过计算这两个参量的变化就可以推算出电路中的阻抗、感抗、容抗,而使用不同频率、不同幅度的信号就能够分析出被测的电路网络的全貌 - 对整个频段的响应、对不同大小信号的反应。

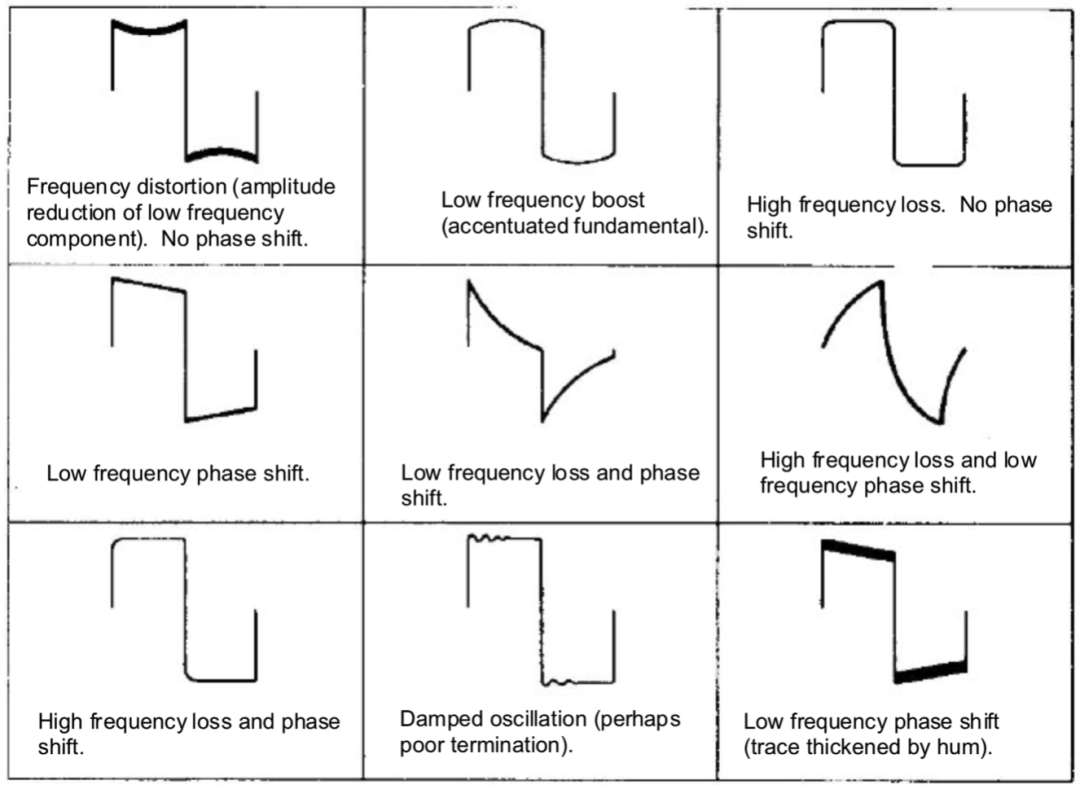

比如,将一个理想的方波信号送到一个电路网络,在示波器上可以看到下面的波形,我们通过波形的形状就可以分析出电路的特性:

不同特性的电路网络对理想方波信号的响应

不同的波形揭示了电路的不同特性

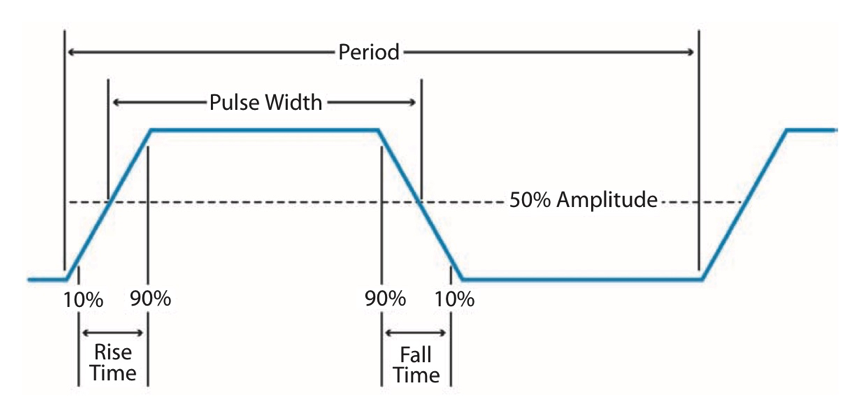

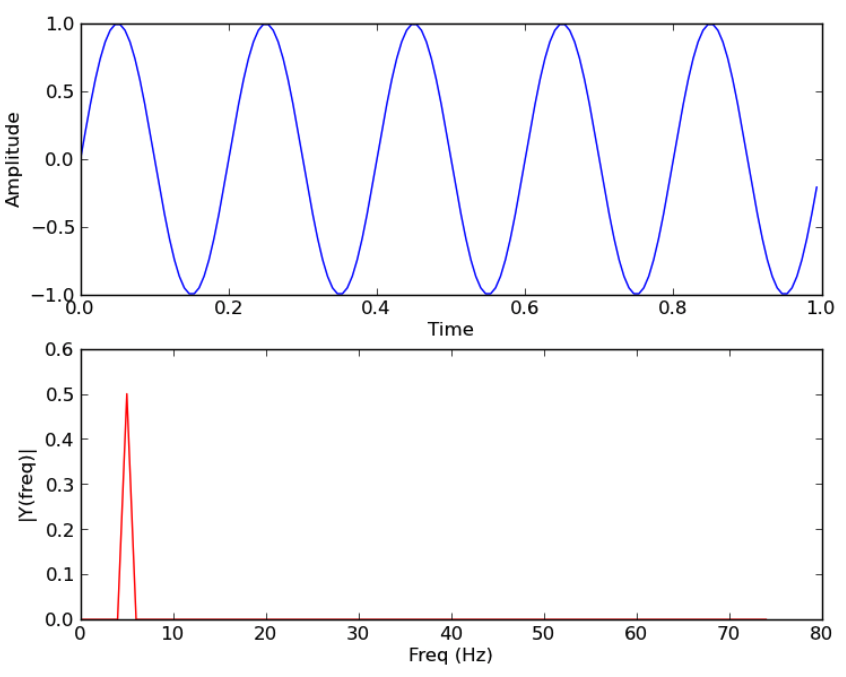

任何实际的电信号都是多种频率电信号的叠加:

我们在时域上看到的非正弦波形的信号,以及那些不规则波形的信号,都可以分解成多个不同幅度的单频正弦波信号的叠加 - 感谢傅立叶!

方波信号的构成

因此,对采集到的电信号进行FFT变换,从频域对电信号进行观察和分析也成了示波器的标配分析功能,虽然简单的FFT变换相对于专业的频谱分析仪显得很初级,但它毕竟是一种性价比非常高的观察方式。

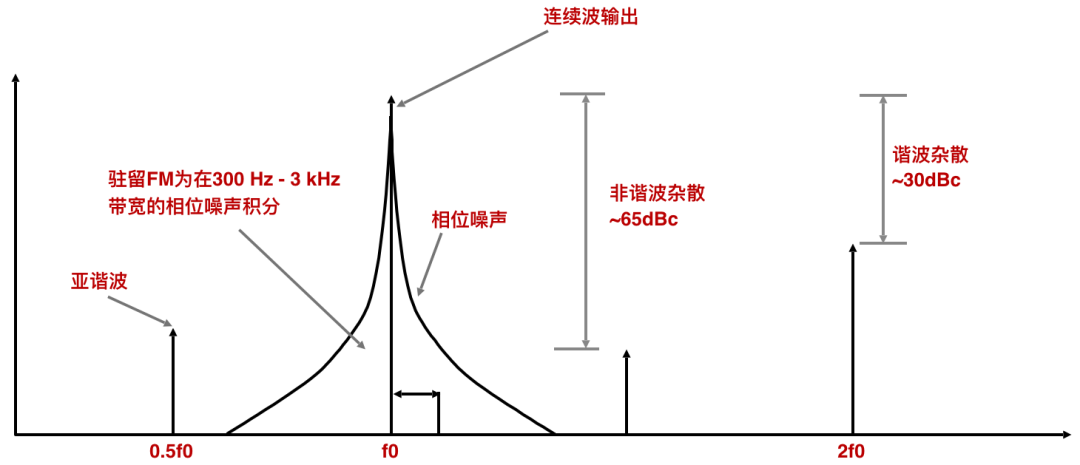

无论示波器的FFT还是专业的频谱仪,只是把一根根谱线给我们显示出来了,如何解读还需要工程师自己的“大脑”,当然是基于对信号的理解,比如下图中的多个谱线来源于电路的不同特性,从每个谱线的大小就可以判断电路是否存在串扰、失真、电源噪声等,往往通过示波器的时域波形很难判断出来,因为它们都叠加在一起,一粒芝麻粘在西瓜皮上是很难分辨出来的。

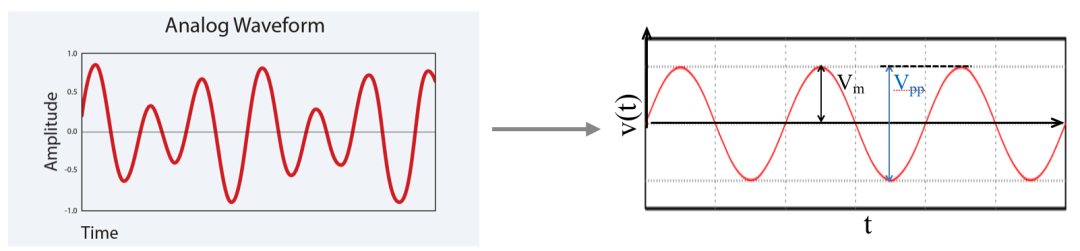

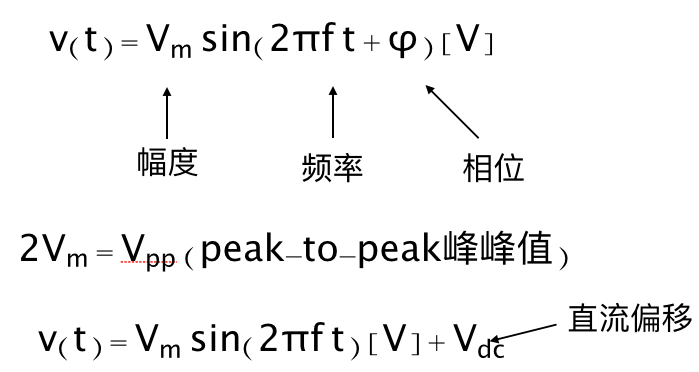

我们做研究最重要的是化繁为简,刚才讲过无论多复杂、多奇怪的电信号波形,我们都可以把它们分解成多个单频信号,而每个单频信号都可以用下面的几个特征参量来表示:

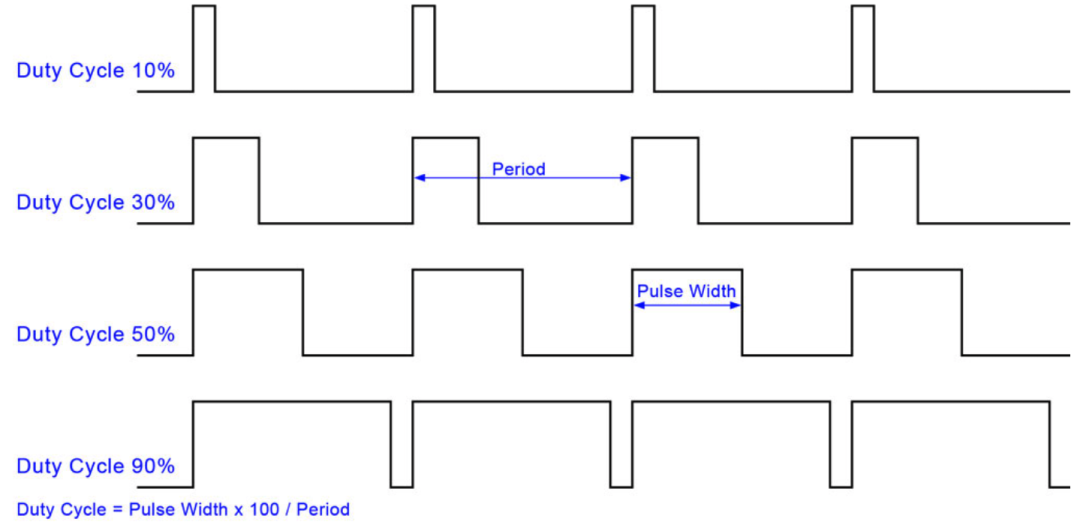

对于脉冲信号,其特征:

- 上升时间:脉冲边沿从低电平到高电平的时间

- 下降时间:脉冲边沿从高电平到低电平的时间

- 脉冲宽度:脉冲从低到高,再从高到低的时间,以全电压的50%为测量基准

- 脉冲信号占空比/延时

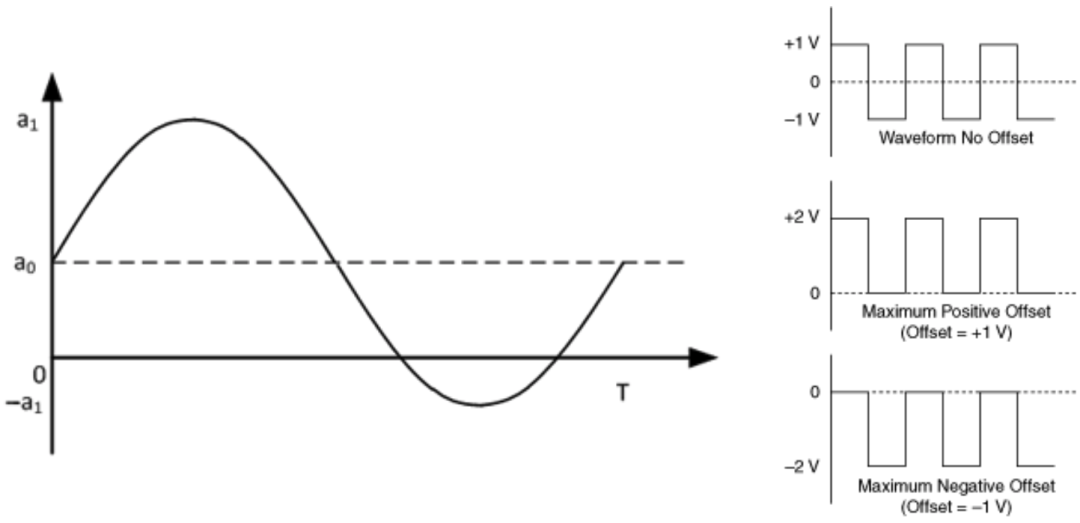

信号幅度特征:

参数:

- 幅度 - 准确度、调节的分辨率

- 动态范围 - 从最小信号到最大信号的跨度(dB)

- 直流偏移 - 在交流信号上叠加的直流分量

- 输出阻抗 - 一般为50

与幅度测量相关的一些指标:

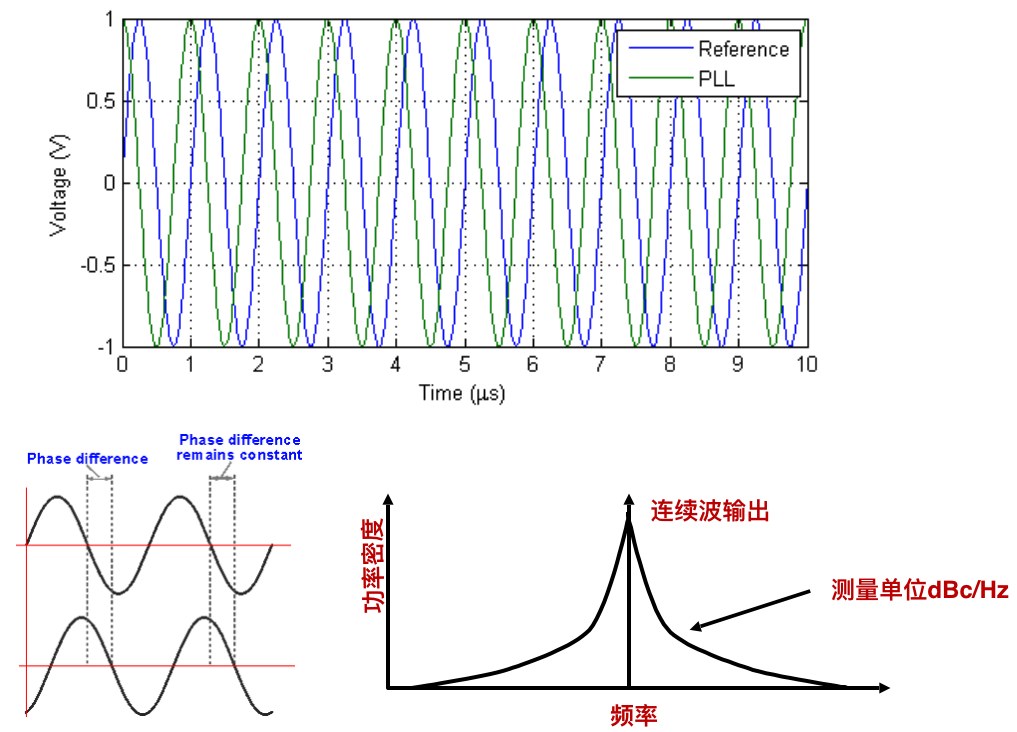

与信号时间特性相关的一些指标:周期/频率/相位

- 频率范围

- 频率准确度

- 频率稳定度

- 可调频率精度

信号时间特性-相位

信号的差分传输:

- 差分信号抗共模干扰能力强,

- 但要注意走线,否则会导致脉冲噪声

我们也会测试一些复合信号:

- 调制波形:

- 模拟调制

- 数字调制

- 脉宽调制

- 正交调制

- 数字模式和格式

- 伪随机数据流

以上简单总结了一下我们用示波器观察的常用的电信号的主要参数以及类型,在下一节的课程中,我们来看一下一个能够观测这些信号的标准的示波器是如何构成的?

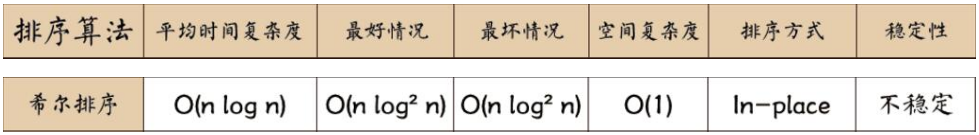

三、C语言的希尔排序

希尔排序是插入排序的一种,又称“缩小增量排序”,希尔排序是直接插入排序算法的一种更高效的改进版本

希尔排序的基本思想

设等待排序等元素序列有n个元素,首先取一个整数increment(小于n)作为间隔将全部元素分为n/increment个子序列,所有距离为increment的元素放在同一个子序列中,在每一个子序列中分别实行直接插入排序,然后缩小间隔increment,重复上述子序列划分和排序工作,直到最后取increment=1,将所有元素放在同一个子序列中排序为止,该方法实质上是一种分组插入方法.

关于增量(increment)的取值

希尔排序的复杂度和增量序列是相关的,一般的初次取序列长度的一半为增量,以后每次减半,直到增量为1,希尔排序中对于增量序列的选择十分重要,直接影响到希尔排序的性能,一些经过优化的增量序列如Hibbard经过复杂证明可使得最坏时间复杂度为O(n3/2) 。

{1,2,4,8,...}这种序列并不是很好的增量序列,使用这个增量序列的时间复杂度(最坏情形)是O(n^2)。

Hibbard提出了另一个增量序列{1,3,7,...,2^k-1},这种序列的时间复杂度(最坏情形)为O(n^1.5)。

Sedgewick提出了几种增量序列,其最坏情形运行时间为O(n^1.3),其中最好的一个序列是{1,5,19,41,109,...}。

代码实现

while里面的代码其实和插入排序的代码没多大区别,就是在两个for循环外面套了一个while再修改了一下内部的for循环,可以对照看一下下面列出来的插入排序的for循环。

排序过程

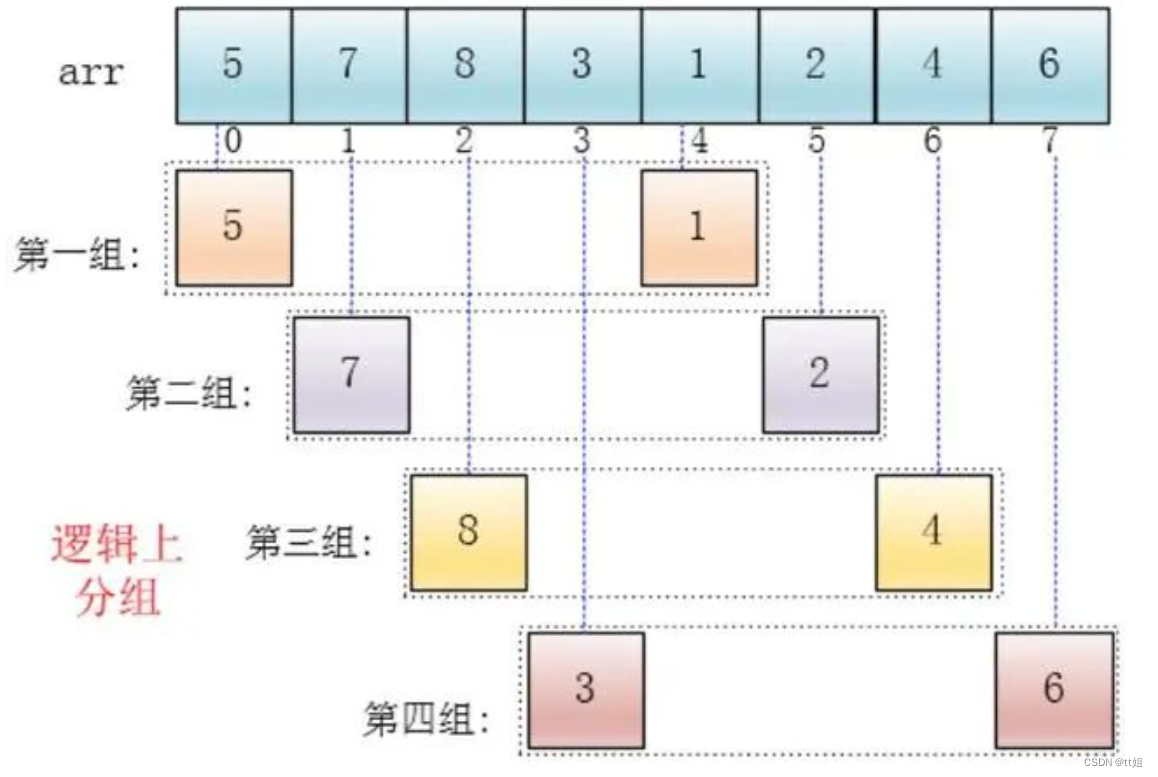

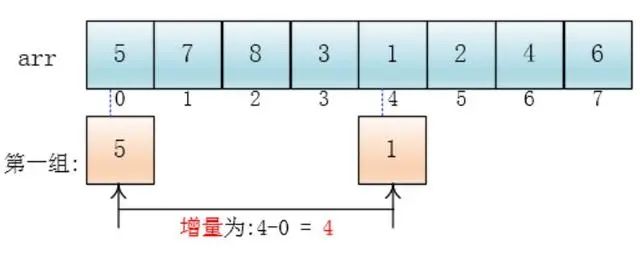

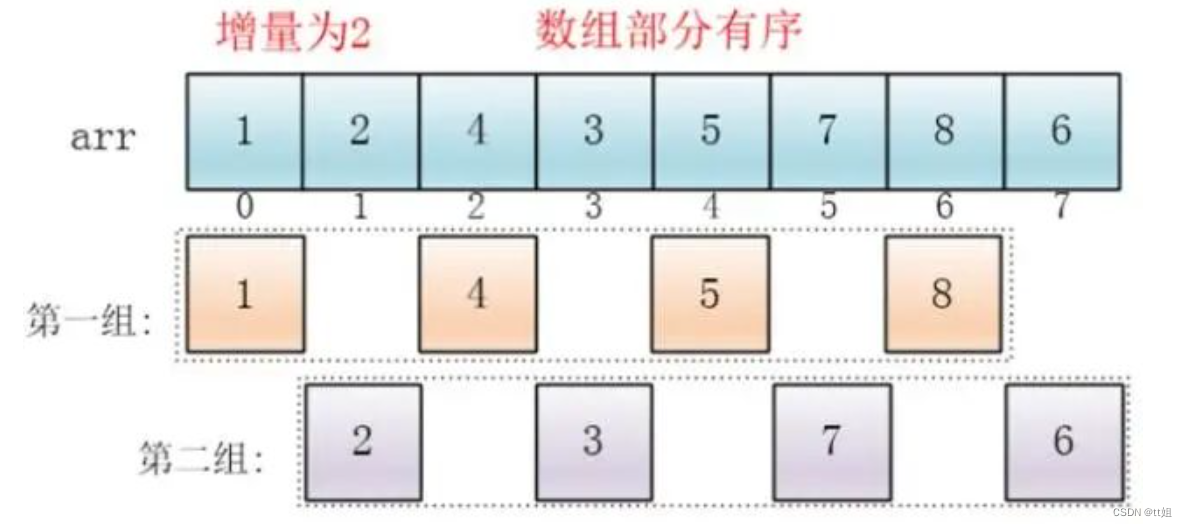

以5,7,8,3,1,2,4,6为例。

下面有颜色的是逻辑上的分组,并没有实际地进行分组操作,在数组中的位置还是原来的样子,只是将它们看成这么几个分组(逻辑上分组)。

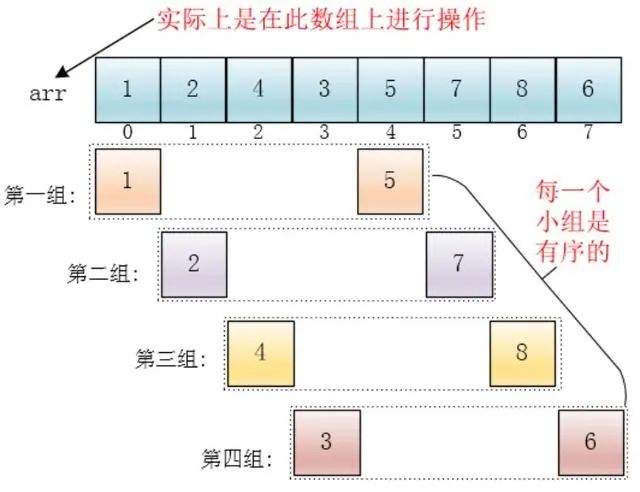

每个分组进行插入排序后,各个分组就变成了有序的了(整体不一定有序)。

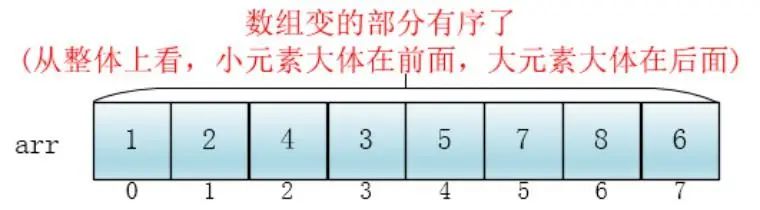

此时,整个数组变的部分有序了(有序程度可能不是很高)。

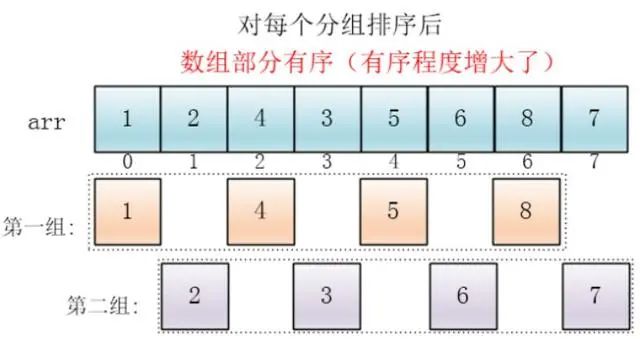

然后缩小增量为上个增量的一半:2,继续划分分组,此时,每个分组元素个数多了,但是,数组变的部分有序了,插入排序效率同样不高。

同理对每个分组进行排序(插入排序),使其每个分组各自有序。

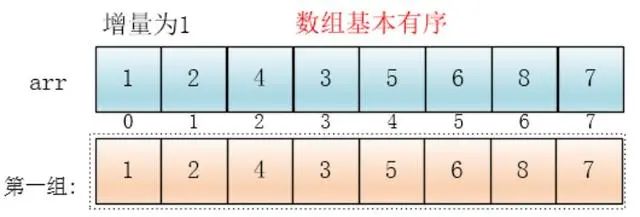

最后设置增量为上一个增量的一半:1,则整个数组被分为一组,此时,整个数组已经接近有序了,插入排序效率高。

同理,对这仅有的一组数据进行排序,排序完成。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?