看了不少时序分析的一些文章,觉得建立时间很好理解,不过没深刻明白那个保持时间的意义是什么,终于搞懂了,觉得学习要不能只拘泥于定义,不理解所以然,所以要追本溯源,结构联系定义,明白深意。

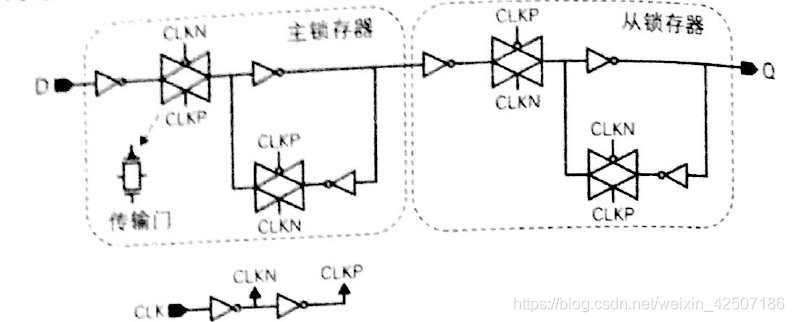

在之前的博客有讲到FPGA内部D触发器的结构是下图这样的

以前的理解:

建立时间是采样时钟的采样边沿来临之前,被采样数据要持续的时间。那么FPGA内部由非阻塞赋值综合出的D触发器是主从俩级锁存器构成的,我想,既然建立时间满足条件了,那么时钟的上升沿(假设采样边沿是上升沿)到来了,那么主断从有效,数据就能稳定到Q端啦,为什么多此一举,还会有什么保持时间的条件呢?意义何在呢?

理解偏差原因:

只知道根据时序图与定义来研究为何会要有建立保持时间这样,不知到要根据触发器结构深入理解定义的提出原因。

正确理解:

要想数据能够在采样边沿被正确锁存起来,那么根据D触发器的结构

要想Q端能够得到正确的数据,要满足俩个条件:

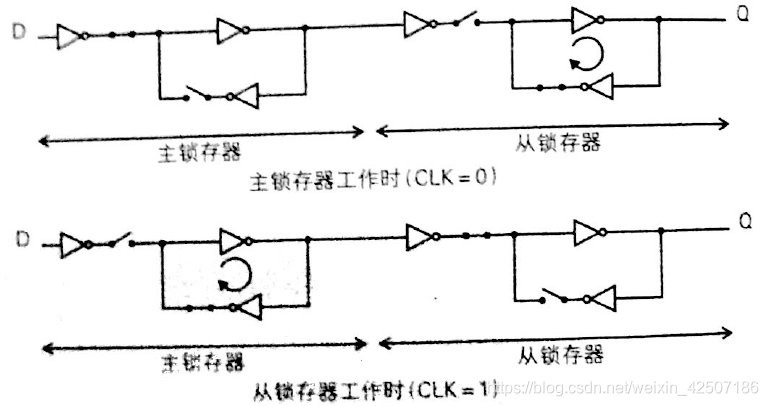

1 在主锁存器传输门关闭后,保证主锁存器的反相器环路能够稳定,即主传输门D的数据沿着反相器环路已经走了一圈。(当CLK为1时,前级反相器环路中保存的数据会传输到后级,同时输入的D信号会被隔离在外,此时如果前级反相器环路中的信号没有循环一圈以上,就会出现0和1之间摇摆的中间电位,这就是亚稳态。亚稳态时间比延迟时间长时,在该阶段读取数据就会引入错误,所以我们引入建立时间来约束在时钟上升沿到来前输入D保持稳定的时间。)

2 当被采样数据使主反向器环路稳定后,而主传输门关闭前,D端数据不能有变化。注意的是,时钟上升沿的时刻不能代表传输门就是关闭了,所以要有保持时间,我理解的这个保持时间就是关于传输门的参数,这个时间是要使传输门彻底的关闭,这样才是理论上的后级锁存器不受前级影响了,能稳定锁存。

那么这时候再说说Tco(时钟上升沿到数据输出到Q端的时间)。由此可看出Th < Tco是必须要如此的,总不能你D端数据在经过主反相器环路后一圈后,然后数据流到Q端,你的主传输门还没有彻底关闭(因为Th的时间还没满足),这样就不是稳定的状态,那么我们的设计就是豪无意义的了。

再解释一下,如果输入D在传输门关闭前就发生变化,那么本该在下一个周期读取的数据就会提前进入锁存器,从而引起反相器环路震荡或产生亚稳态,因此在CLK=1之后也需要输入D维持一定的时间,我们称之为保持时间约束。

我们决定使用哪款FPGA,从工艺上来讲,也就意味着建立和保持时间也就确定了,因为我们的设计受限于数字器件能够稳定工作的必要前提。Xillinx的建立时间基本都在0.04ns的量级,保持时间基本在0.2ns的量级,不同器件有所差异。具体要根据手册的DC and AC Switching Characteristics了。

有人会说,我们都在设计时,会说这个被采样数据要建立时间与保持时间要满足各自最小的要求时间。那Th又为啥要小于Tco呢????要注意,Th < Tco这里我们都是从器件的角度分析,意味着我们用的FPGA,包括芯片设计者,他们传输门关闭的时间要小于数据到达Q端的时间,针对器件设计者而言,而我们写代码做设计开发时,只要你能满足主反相器环路与传输门能正确稳定工作的要求时间就行了,所以你的D端数据维持稳定的时间大于Th,很正常啊。

以上为自己的理解,若有不对的地方,望指正

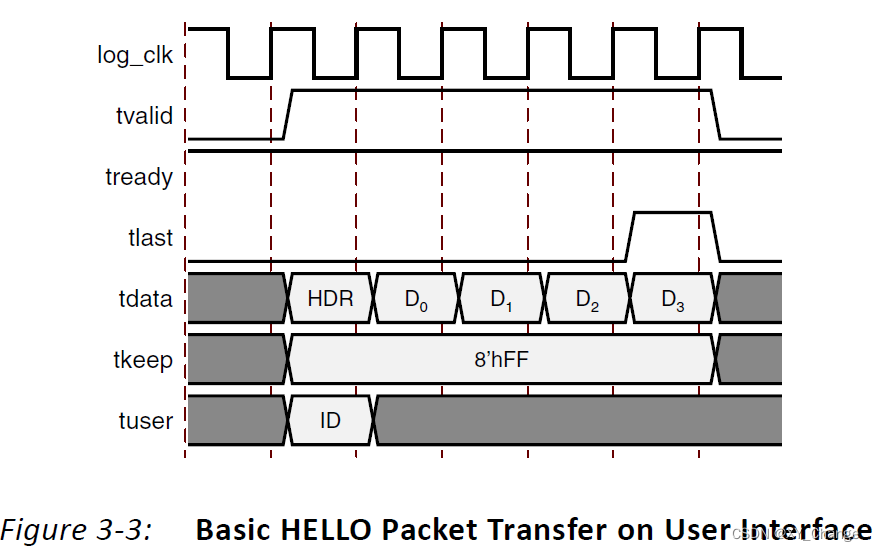

前端时间做项目用到SRIO协议,然后在生成SRIO IP核后生成官方例程工程。发送发送端代码,对val_ireq_tdata是在时钟上升沿进行打数据进入发送端IP核。那我当时迷惑了。记得刚入门fpga时写的第二个代码就是SPI协议通信,当时记得当上升沿捕获数据时,对于主机来说下降沿进行发送数据,对于从机来说,上升沿进行锁存数据。所以我看了xillinx的关于SRIO协议手册pg007(79页时序)

我当时看了这个时序觉得,既然上升沿锁存数据,那么不是应该下降沿往IP核里打数据嘛?可是官方例程里人家为什么用上升沿打数据呢?

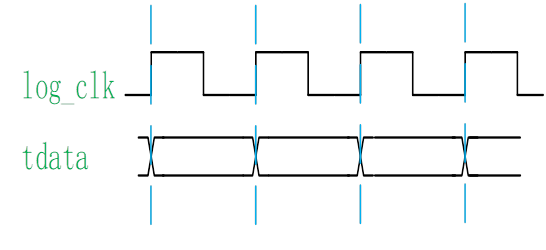

我会觉得用上升沿打数据,IP接收端的数据与时钟应该如下图:

我当时想,若是这样是肯定不满足建立时间。但是我错了。用下降沿发送肯定没问题,不过这里用上升沿打数据也没有问题,而且pg007的文档给出的时序其实就是上升沿打数据的时序。那只能是我想的时序是错的。根据分析确实如此,上升沿打数据,别忘了对D触发器有一个Tco,所以pg007的数据才会较时钟上升沿往右偏一些,又因为Tco是大于Thd的,所以保持时间肯定满足了。所以我们用上升沿打数据是没有问题的。我所画的时序图很明显是纯拍脑袋的,没有考虑到延迟。所以记录下此次思考。

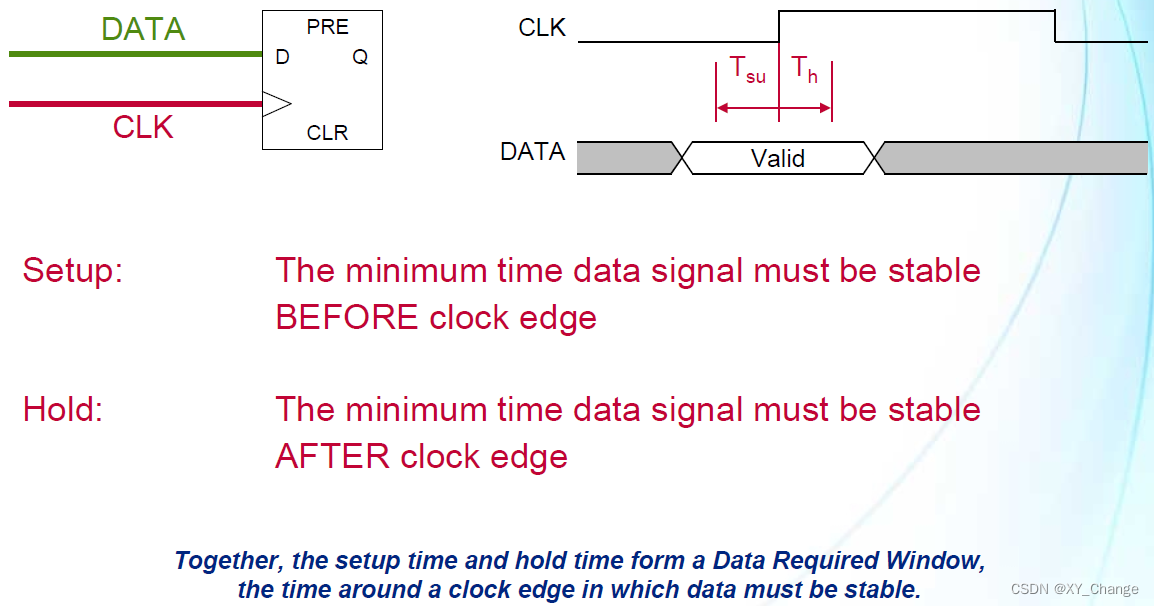

Setup Time:即建立时间,在时钟上升沿之前数据必须稳定的最短时间。若不满足setup time,数据无法进入寄存器:Tsu < Tclk + Tskew – Tco。

Hold Time:即保持时间,在时钟上升沿之后数据必须稳定的最短时间。若不满足hold time,数据无法进入寄存器:Th < Tco。Th 限制了数据传输的速度。如果Tco延时太短导致上一级寄存器锁存的数据侵占了下一级寄存器正在锁存数据的保持时间,那么下一级寄存器就无法有效的锁存数据,系统时序也就无法达到要求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?