Verilog有两种基本数据类型:变量(reg)和网线(wire),这是四态的数据类型(0、1、X、Z)。

RTL代码使用变量(reg)存储组合逻辑和时序逻辑的数值,可以是标量

向量(reg[7:0] bus_addr)

有符号数32位变量(integer)

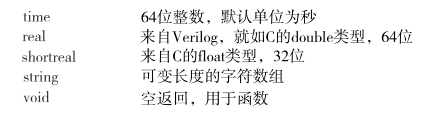

无符号数64位的变量(time)

浮点数(real)

变量也可以用来定义一个固定大小的数组

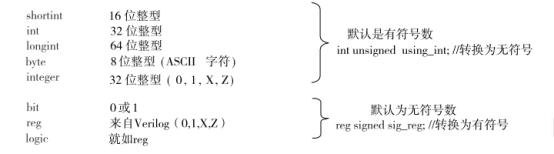

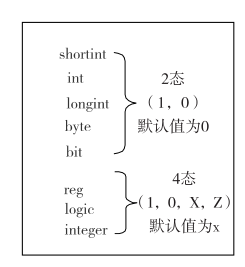

两态(1/0)数据类型:

SystemVerilog中的两态数据类型减少了仿真器对内存的使用和提高仿真的运行效率。其中,bit是无符号数,shortint、int、longint、byte是有符号数。

基本数据类型

整数数据类型

如:

bit a; //两态,单比特bit[31:0] b32; //两态,32比特无符号数Int c32; //两,32比特有符号数byte d8; //两态,8比特有符号数shortint e16; //两态,16比特有符号数longint f32; //两态 ,32比特有符号数

这篇博客介绍了Verilog中的两种基本数据类型:变量(reg)和网线(wire),以及它们在组合逻辑和时序逻辑中的应用。SystemVerilog对数据类型进行了扩展,包括了两态和四态数据类型,如bit、int、longint等,并引入了logic类型。文中还强调了在数据运算中注意有符号和无符号数据类型的区别,并提到了reg类型在SystemVerilog中的新特性。

这篇博客介绍了Verilog中的两种基本数据类型:变量(reg)和网线(wire),以及它们在组合逻辑和时序逻辑中的应用。SystemVerilog对数据类型进行了扩展,包括了两态和四态数据类型,如bit、int、longint等,并引入了logic类型。文中还强调了在数据运算中注意有符号和无符号数据类型的区别,并提到了reg类型在SystemVerilog中的新特性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?