欢迎FPGA工程师加入官方微信技术群

点击蓝字关注我们FPGA之家-中国最好最大的FPGA纯工程师社群

ModelsIm是FPGA仿真中最常见的软件之一。可以单独利用Modelsim来仿真或者通过开发工具调用来联合仿真。至于用哪一种方法呢?那就取决于个人的喜好了,经过一段时间的对比,目前我比较趋向于利用开发工具联调来仿真。主要有以下优势:

联调仿真分析,操作简单。你几乎不需要手动敲Tcl指令就可以进行仿真,自动化程度更高。

与单独用Modelsim建立工程仿真相比,联调仿真一般在仿真是所需要调用的库,软件会自动分析,不需要自己筛选仿真所需的库文件,且不容易出错。这一优势在你仿真工程中带有大量IP核、原语的时候,会体现得淋漓尽致。

在仿真时候,多个测试用例仿真时,层次结构更加清晰。

本文就如何利用vivado联合modelsim仿真进行简要说明。

1.仿真前具体设置

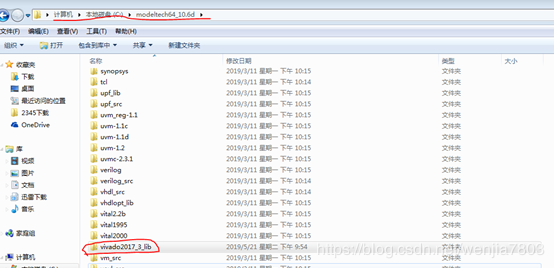

利用vivado先编译好modelsim仿真所需要的库。存放在某个文件夹中,方便以后调用。我的习惯一般将库放到modelsim的安装目录下,新建一个文件夹来存放新编译的库。如下图所示文件夹叫vivado2017_lib。方便区分,我就以我用的vivado版本来命名。

修改modelsim.ini文件,将库添加到modelsim的启动中。具体做法在介绍modelsim仿真一文有详细说明,这里不展开。

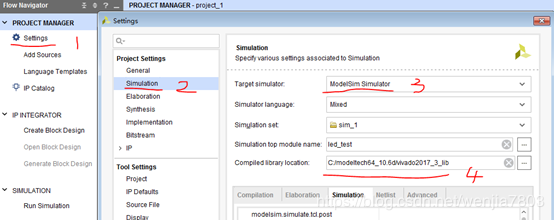

接Vivado的相关设置。主要包含以下4步,其中第4步是把仿真库指向前一个步骤编译出来的库文件。第5步是指向modelsim启动程序的路径。

以上即做好了联合仿真前的准备设置工作了。

2.仿真步骤

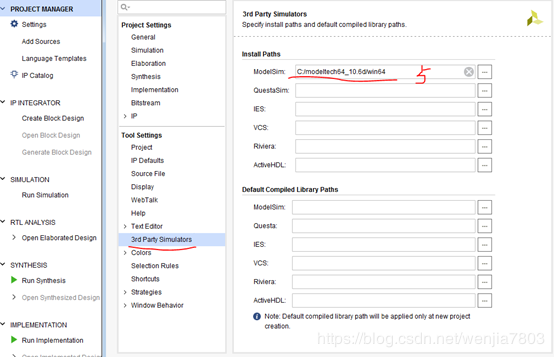

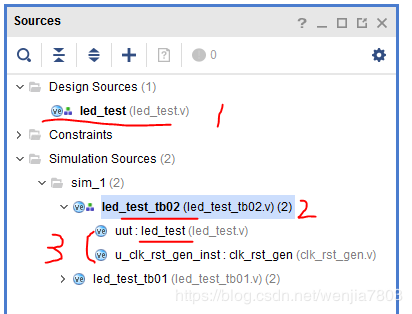

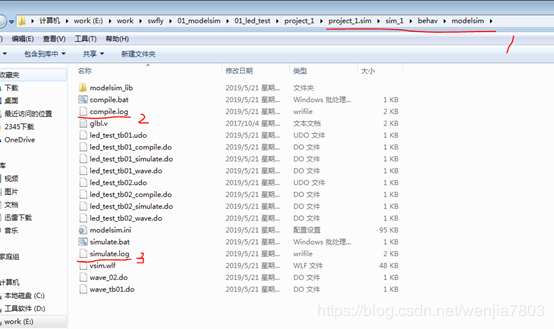

工程准备完毕后,添加好仿真所需文件(testbench/仿真激励模块)。例如下图中,1是我准备要仿真的工程。2是仿真的顶层文件即测试用例,3是仿真包含的内容,包括需要仿真的文件(UDT),仿真激励,例如时钟以及复位产生文件等。其中UDT即仿真对象是可综合的文件。

激活当前仿真的测试用例,就可以开始仿真了。

问题1:如何保留我这一次的观察信号设置?

具体操作步骤如下:

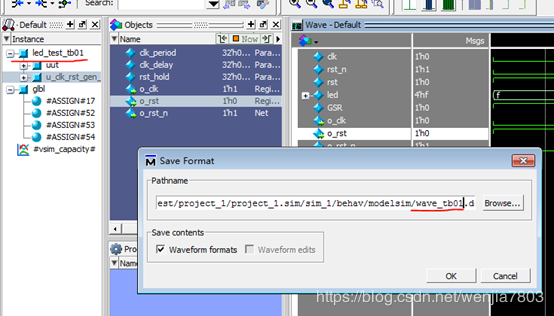

为了方便保留这一次仿真中的一些观察信号以及设置,我们可以把它保存下来。在modelsim软件呢中,点击保存,想这次的相关设置保存好do文件。注意:为例避免被覆盖掉,一般不能取默认的命名,建议将do文件命名与对应的测试用例对应上。

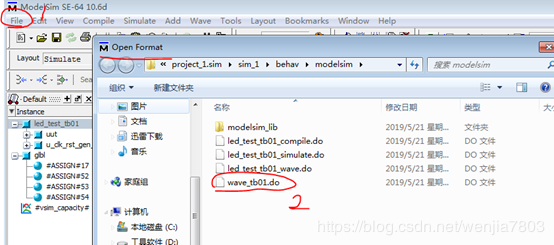

问题2:怎样还原上一次的仿真波形等设置?

在下一次启动modelsim的时候,选择File—>LoadàMacro_File,然后选择上一次保留的设置文件即可。

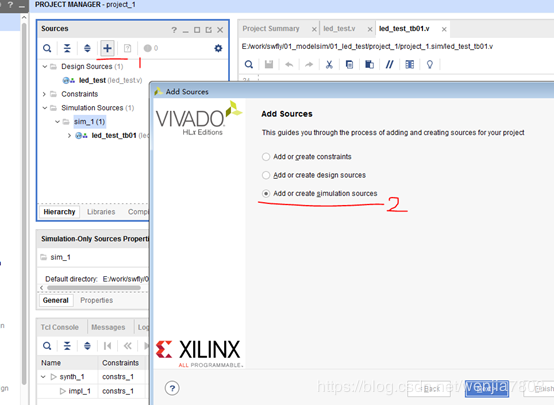

问题3.如何添加多个测试用例文件?

通过下述步骤添加仿真文件。例如不同的testbench等。

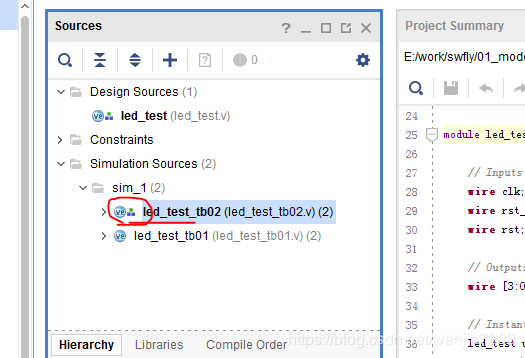

针对多个testbench的情况,通过设计set_as_top选择来激活当前testbench,从而决定该次仿真的测试用例。如下图的工程中,包含了2个测试用例,当前激活的是tb02。

3.可能出现的问题

联合仿真的时候,有时候并不像单独利用modelsim仿真的那样,会弹出错误日志方便你定位。有时候有些错误(例如语法错误,编译顺序的问题,中文路径或者缺乏某个文件导致没能仿真成功)会导致vivado一直卡住了,没能够走到调用modelsim的不骤。那么碰到这种情况,我们可以去哪找到日志呢?

以我建的工程为例,一般在vivado存放仿真工程的路径中,可以找到compile.log和simulate.log这两个日志文件,方便定位。

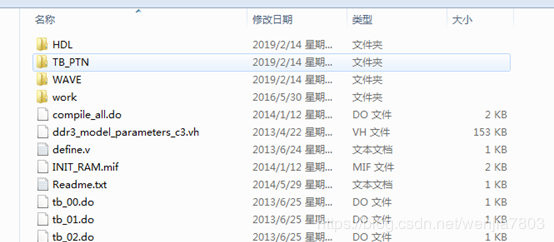

4.仿真文件管理建议

一个好的仿真文件管理习惯,有助于快速还原当初的仿真环境,有助于定位问题。

最起码可以在仿真文件中包含以下几个子文件夹,其中HDL用于存放仿真是所编写的一些文件,例如仿真的时钟产生模块、外围芯片模型等;TB_PTN用于存放不同的测试用例,即不同的testbench。Wave文件用于存放针对不同testbench下观察信号的设置等等。

欢迎通信工程师和FPGA工程师关注公众号

全国第一大FPGA微信技术群

欢迎大家加入全国FPGA微信技术群,这个群体拥有数万工程师、一群热爱技术的工程师,这里的FPGA工程师相互帮助,相互分享,技术氛围浓厚!赶紧叫上小伙伴一起加入吧!!

用手指按住就可以加入FPGA全国技术群哦

FPGA之家元器件芯城

优势元器件服务,有需求请扫码联系群主:金娟 邮箱:293580331@qq.com 欢迎推荐给采购

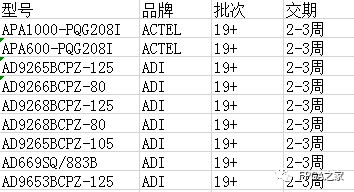

ACTEL、AD部分优势订货(经营全系列):

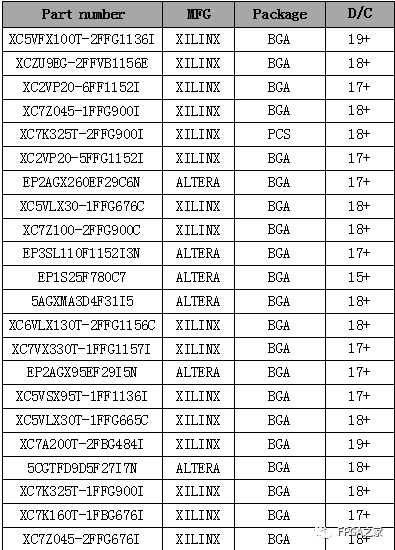

XILINX、ALTERA优势现货或订货(经营全系列):

(以上器件为部分型号,更多型号请咨询群主金娟)

服务理念:FPGA之家元器件自营芯城,旨在方便工程师快速方便购买器件服务,经过数年竭诚服务,我们的客服遍布国内大型上市公司、军工科研单位、中小企业、最大的优势是强调服务至上的理念、并且做到快速交货、价格优惠!

直营品牌:Xilinx ALTERA ADI TI NXP ST E2V、镁光 等百余元器件品牌,尤其擅长欧美对华禁运器件,欢迎工程师朋友把我们推荐给采购或者亲自咨询我们!我们将一如既往提供业内最佳服务!

FPGA技术群官方鸣谢品牌:Xilinx、 intel(Altera)、microsemi(,Actel)、LattIC e,Vantis,Quicklogic,Lucent等

1616

1616

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?