添加除法 IP核的方法和之前的BRAM方法相同,在IP Catalog → Math Functions → Divider Generator。

其中常用的关键选项配置解释如下:

Algorithm Type:选择不同的算法模式,其中Radix2为常用的模式,LutMult当时数较小的时候使用,High Radix是当数很大的时候使用。常用的是Radix2,此处也是选择的为Radix2.

Dividend Width:被除数的位数。

Divisor Width:除数的位数。

Remainder Type:选择余数的模式。有两种模式:Remainder:余数,以及Fractional分数模式。Remainder模式的余数模式位数固定,由系统根据除数自动设定,如上图中的就是5位,即Fractional Width那一栏。而选择Fractional Width模式,则可以在Fractional Width那一栏选择自己想要的余数位数。常用模式为Remainder模式。

以上就是需要主要设置的配置。常用情况下,其他设置可以不用配置。

同时我们发现作图的端口图上的被除数、除数以及结果的位数与我们设定的并不相同,所以我们以左边端口图的位数为准,来测试下,我们设置的位数与左边端口图位数的关系。

Testbench的代码如下:

module test_1(

);

reg clk;

reg s_axis_divisor_tvalid;

reg [7:0] s_axis_divisor_tdata;

reg s_axis_dividend_tvalid;

reg [15:0] s_axis_dividend_tdata;

wire m_axis_dout_tvalid;

wire [23:0] m_axis_dout_tdata;

always #5 clk = ~clk;

initial

begin

clk = 0;

s_axis_divisor_tvalid = 0;

s_axis_dividend_tvalid = 0;

s_axis_divisor_tdata = 0;

s_axis_dividend_tdata = 0;

#1000 s_axis_divisor_tvalid = 1;

#0 s_axis_dividend_tvalid = 1;

#0 s_axis_divisor_tdata = 13;

#0 s_axis_dividend_tdata = 96;

#10 s_axis_divisor_tvalid = 0;

#0 s_axis_dividend_tvalid = 0;

end

div_gen_0 div_gen_0(

.aclk (clk),

.s_axis_divisor_tvalid (s_axis_divisor_tvalid),

.s_axis_divisor_tdata (s_axis_divisor_tdata),

.s_axis_dividend_tvalid (s_axis_dividend_tvalid),

.s_axis_dividend_tdata (s_axis_dividend_tdata),

.m_axis_dout_tvalid (m_axis_dout_tvalid),

.m_axis_dout_tdata (m_axis_dout_tdata)

);

endmodule

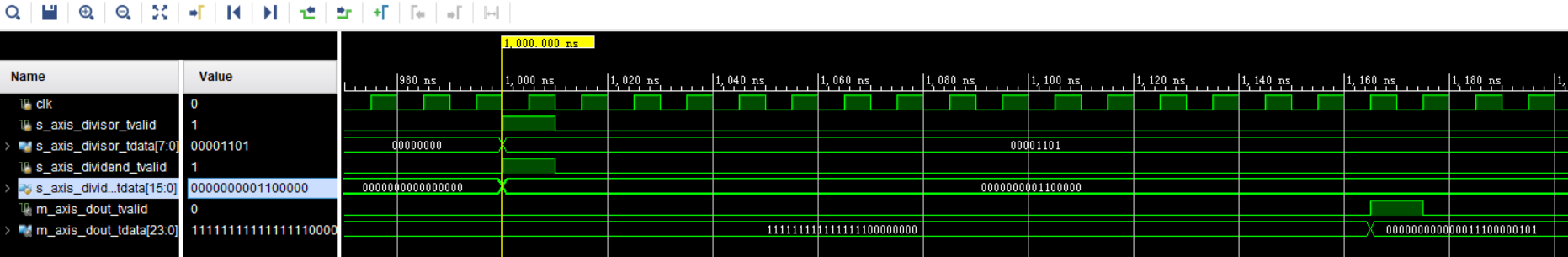

使用该IP核时,在数据送达时,被除数与除数的使能信号也要同时送达,从而才能输出结果,如功能仿真图所示(96/13):

从上图可以看出,96/13所得到的结果即m_axis_dout_tdata的值并不是7,可以分析出,m_axis_dout_tdata的低八位是余数5,而剩下的第8到第23位是结果7.

所以我们可以得到结论,除法的IP核的设置是以8位为单位的,如在此设置中我们设置的被除数为15位。但是可以看出在左边的模块图中,系统自动将被除数位数设置为16位,同理若我们将被除数设置为23位的话,那么系统会将被除数位数设置为24位,即8位的3倍。同理除数的5位,系统自动设置为了8位,然后结果就是24位,后八位(对应除数的位数)是余数,剩下的16位(对应被除数的位数)为商。所以我们在写verilog代码时,我们设置的位数,需要根据在设置界面左侧的电路显示的位数为准才可以。

综上也就是说,当我们在使用除法的IP核时,我们可以先将除数与被除数的位数拓宽为8的整数倍的位数,如23→24,6→8等,即输出的位数要与除法IP核的位数相同,才能得到正确的结果。

本文介绍了如何在Vivado 2017.1中配置和使用除法IP核,重点讲解了Algorithm Type、Dividend Width、Divisor Width和Remainder Type等关键选项。通过测试bench验证,得出结论:除法IP核的位数以8位为单位,实际输出位数需与IP设置的左侧端口图一致,以确保计算正确。

本文介绍了如何在Vivado 2017.1中配置和使用除法IP核,重点讲解了Algorithm Type、Dividend Width、Divisor Width和Remainder Type等关键选项。通过测试bench验证,得出结论:除法IP核的位数以8位为单位,实际输出位数需与IP设置的左侧端口图一致,以确保计算正确。

1171

1171

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?