总体概述

该芯片是一款典型的大容量NAND Flash存储颗粒,支持Open NAND Flash Interface (ONFI) 2.1的接口标准,采用ONFI NANDFlash的操作协议。该芯片采用Multiple-level Cell (MLC)技术,根据不同的容量,一个芯片内部封装了多个DIE(LUN),每个DIE由两个Plane构成,一个Plane可以分成2048个Block,每个Block由256页组成,一个页的大小为8KB+448B的组织结构方式。

在性能方面,一个Page页的读延迟在50us左右,页编程时间为900us,块擦除时间长达3ms。每个块的标称擦除寿命达到5000次。

芯片接口及信号

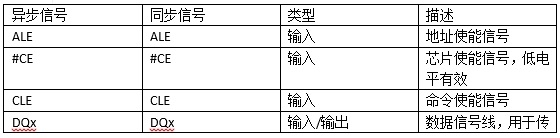

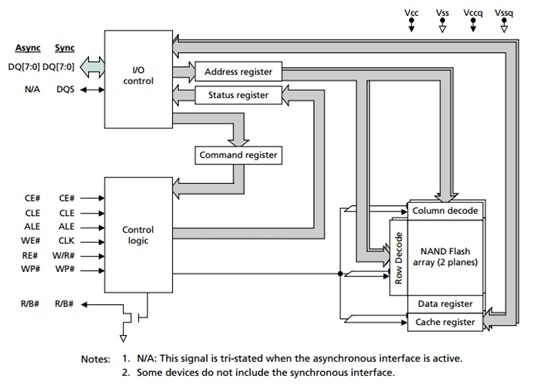

镁光的芯片支持同步和异步两种接口模式。在异步接口模式下,采用5个控制信号,分别为#CE,CLE,ALE,#WE和#RE,另外#WP用于控制芯片的写保护,R/#B用于检测芯片的当前状态。在同步操作模式下,#WR引脚为时钟输入信号,#RE信号为读写方向指示信号。

NAND Flash的接口信号具体定义如下:

一个NAND Flash物理芯片可以由多个DIE(或者称之为LUN)的单元构成,每个DIE会有一套独立的上述提及的控制信号线。一个DIE中会存在若干个Plane,每个Plane有许多Block单元组成,一个Block单元是一个最小的擦除单位,并且有数量较多的Page页构成,每次写的最小单元就是一个Page页。对于容量较小的芯片,芯片厂商只会封装一个DIE,每个DIE的内部结构如下图所示:

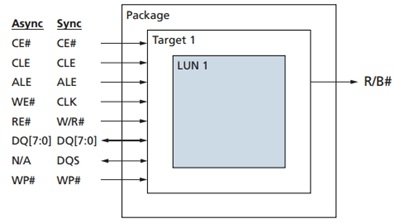

对于镁光512Gb芯片,一个DIE内部集成了两个Plane,通过一套控制信号线和寄存器控制内部的两个Plane同时并发工作。值得一提的是,多个DIE(LUN)可能会共享一套控制信号线,因此,在物理上多个DIE会被封装成一个Target。需要注意的是,同一个Target内部的DIE虽然共享了物理信号线,但是寄存器都是相互独立的。因此,从结构上来看,一个NAND Flash的内部架构可以只由一个DIE(LUN)构成,如下图所示:

</

</ 最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2482

2482

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?