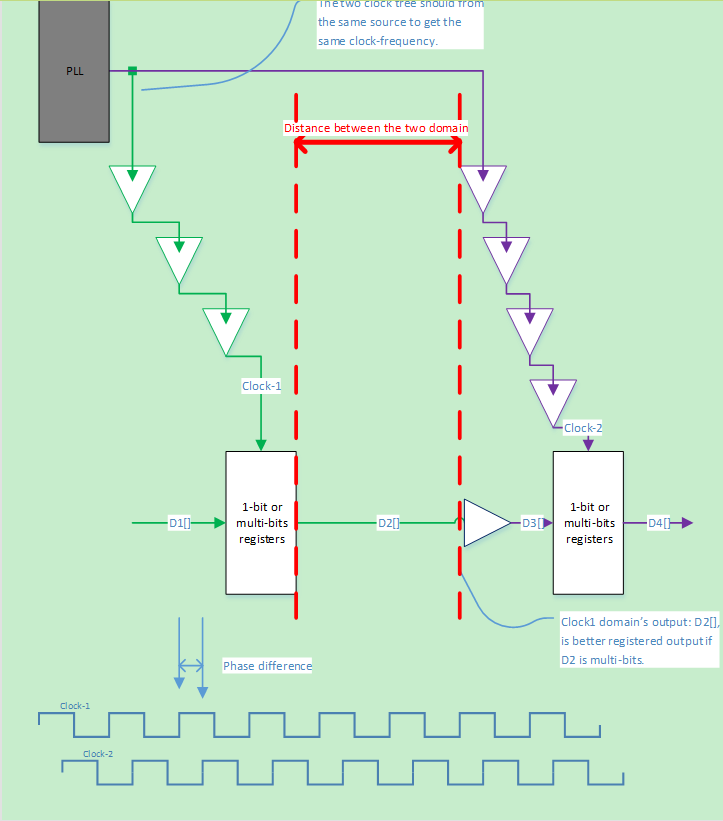

Data Synchronization with Two Same-frequency/Different Phase Clock domains

When data is transferred from one clock domain to another clock domain, and the two clock domains are at the same clock-frequency, and are different clock phase for the two clock domain has different clock tree as show below.

From the figure, there are several important points to be highlighted.

- The two clock domain's clock tree should be the same source;

- Same PLL's output;

- Different PLL, but same clock reference;

- If D is multi-bits data, D should be better registered-output from clock domain-1 (thus it is easier for backend to balance the timing of D2[] and D3[] by adding less buffers);

- From experience, there is no must-to-have such requirement if D1 and D4 are nearer in the floorplan of the design;

- If there is registers for D2[], then the two clock domain can have long distance location, thus the clock tree for the two clock domain will have clean boundary for dynamic clock management and without introducing much power of buffers for clock-tree's balance.

- Between D2[] and D3[], balance buffer are added to meet the timing requirement for clock-2;

This method is benefit area comparing to a-sync-FIFO (the depth should be larger than 8) strategy for both 1-bit and multi-bits width data-synchronization. But the synthesis constraint should be put to the top-level of the 2 clock domains; and timing analysis should be very focus on this.

本文探讨了在两个相同频率但不同相位的钟域间进行数据同步的方法。重点介绍了通过使用相同的PLL输出或不同的PLL但相同的参考时钟来实现这一目标的技术细节。此外还讨论了多比特数据在不同钟域之间的平衡与约束。

本文探讨了在两个相同频率但不同相位的钟域间进行数据同步的方法。重点介绍了通过使用相同的PLL输出或不同的PLL但相同的参考时钟来实现这一目标的技术细节。此外还讨论了多比特数据在不同钟域之间的平衡与约束。

1712

1712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?