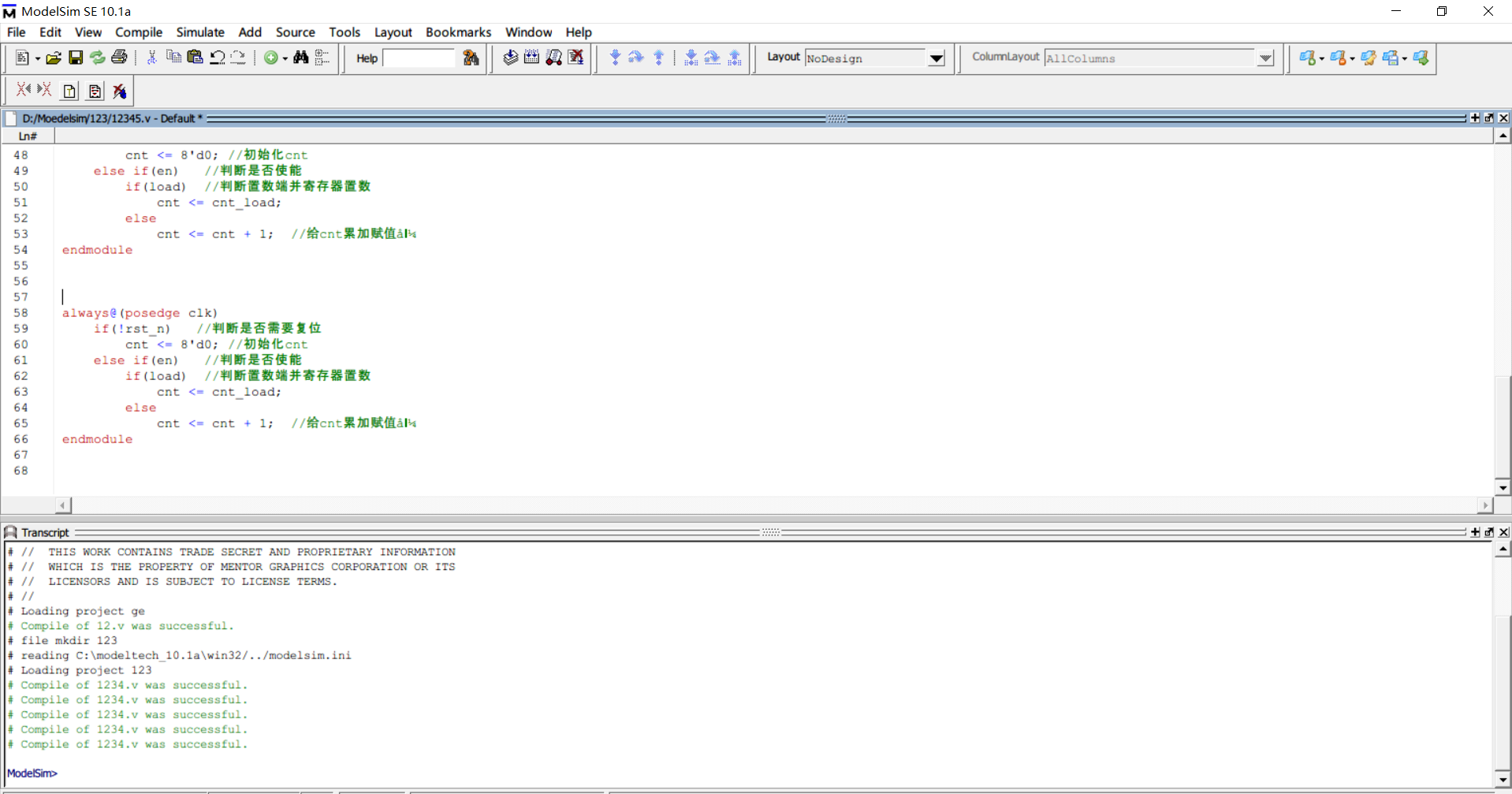

注释都加上了

由于参考网上的代码,其实现了置数 ,使能等功能,一并加上了

编译结果能通过

百度网盘文件下载:https://pan.baidu.com/s/1IVTD19NRk-s2dKBXtATkAA

module counter( rst_n, //复位 clk, //时钟 en, //使能 load, //置数 cnt_load, cnt ); parameter CNT_SIZE =60; input rst_n; //复位 input clk; //时钟 input en; //使能 input load; //置数 input [59: 0] cnt_load; output [ 59: 0] cnt; reg [59: 0] cnt; //带有同步复位、使能、置数端的计数器 always@(posedge clk) if(!rst_n) //判断是否需要复位 cnt <= 8'd0; //初始化cnt else if(en) //判断是否使能 if(load) //判断置数端并寄存器置数 cnt <= cnt_load; else cnt <= cnt + 1; //给cnt累加赋值 endmodule

参考的 资料也有,这边贴一下链接,可以去看一下

六位 十位进制计数器

本文介绍了一个基于Verilog的计数器模块设计,包括同步复位、使能及置数功能。提供了完整的代码实现,并附有参考资料链接,便于读者理解和实践。

本文介绍了一个基于Verilog的计数器模块设计,包括同步复位、使能及置数功能。提供了完整的代码实现,并附有参考资料链接,便于读者理解和实践。

1229

1229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?