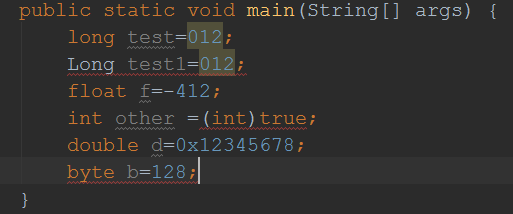

选ABD

A和B中long和float,正常定义需要加l和f,但是long和float属于基本类型,会进行转化,所以不会报出异常。AB正确

boolean类型不能和任何类型进行转换,会报出类型异常错误。所以C错。

D选项可以这样定义,D正确。

E选项中,byte的取值范围是-128—127。报出异常: cannot convert from int to byte.所以E选项错误。

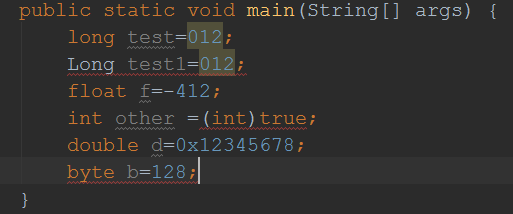

选ABD

A和B中long和float,正常定义需要加l和f,但是long和float属于基本类型,会进行转化,所以不会报出异常。AB正确

boolean类型不能和任何类型进行转换,会报出类型异常错误。所以C错。

D选项可以这样定义,D正确。

E选项中,byte的取值范围是-128—127。报出异常: cannot convert from int to byte.所以E选项错误。

转载于:https://my.oschina.net/u/3847203/blog/3017527

511

511

1454

1454

1603

1603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?