功能介绍

您可以在控制台clone一个安全组,进而快速创建安全组和添加安全组规则,但这个功能有个限制是无法跨region使用。为此ECS控制台开发了安全组规则导入导出功能,使用这个功能您可以把一个安全组下所有规则导出成json文件,这样就可以方便地在另外一个region的安全组内导入这些规则,进而实现跨region快速设置安全组规则的目的。

使用方法

导出规则

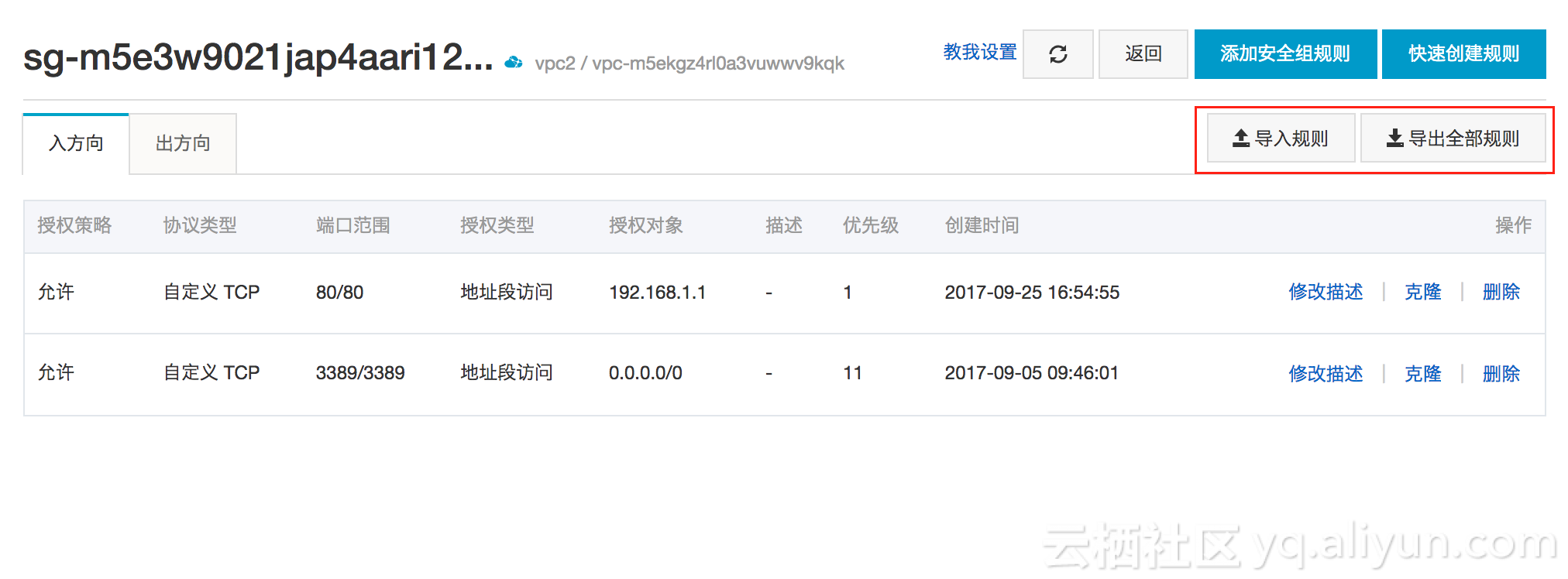

- 找到要导出规则的安全组并进入规则配置详情页

- 点“导出全部规则”按钮完成规则导出,截图如下:

导出成功后,会在您本地看到保存当前安全组所有规则的json文件,此文件命名规则如下:ecs_${region_id}_${安全组ID}.json 假设region_id是cn-qingdao, 安全组ID是sg-123,那么文件名是 ecs_cn-qingdao_sg-123.json

导入规则

- 找到要导入规则的安全组并进入规则配置详情页(截图如上)

- 点“导入规则”选择之前导出的规则文件,比如就是ecs_cn-qingdao_sg-m5exxx.json

- 系统会对要导入的规则做某些必要的检查并给出预览,截图如下:

在预览页面您可以看到:

- 要导入的规则数

- 规则详情以及初步检查结果,如果检查失败,光标移到警告图标上会有具体的提示信息

- “导入全部规则”的checkbox,默认选中。如果您要导入的规则优先级>100,选中“导入全部规则”ECS控制台会强制把优先级调整为100,否则这样的规则不会导入

- 点“开始导入”按钮

- 系统开始导入,完成后会展示导入结果,截图如下:

- 在列表的第1列显示当前规则导入是否成功,如果失败,光标移到警告图标上会显示错误信息

- 显示导入规则数- 点“导入结束,关闭”按钮结束本次导入,此时可查看当前安全组内规则已经发生变化

本文介绍了一种在不同地域间快速配置阿里云ECS安全组的方法,通过导出和导入JSON文件,实现安全组规则的批量迁移。

本文介绍了一种在不同地域间快速配置阿里云ECS安全组的方法,通过导出和导入JSON文件,实现安全组规则的批量迁移。

1857

1857

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?