一. 拓扑

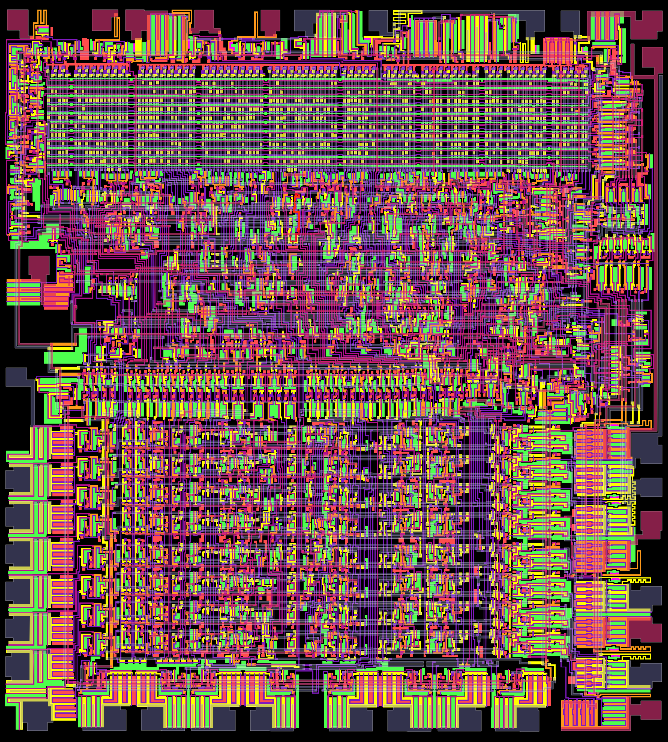

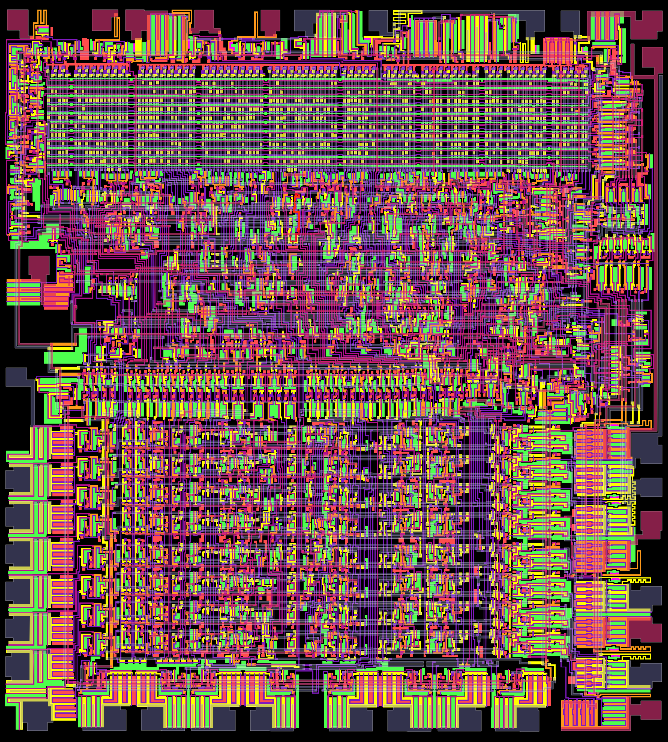

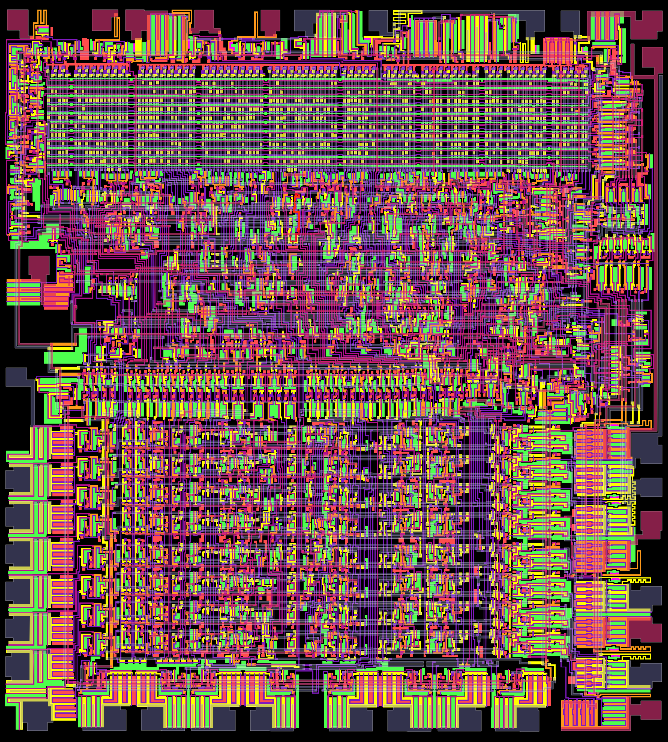

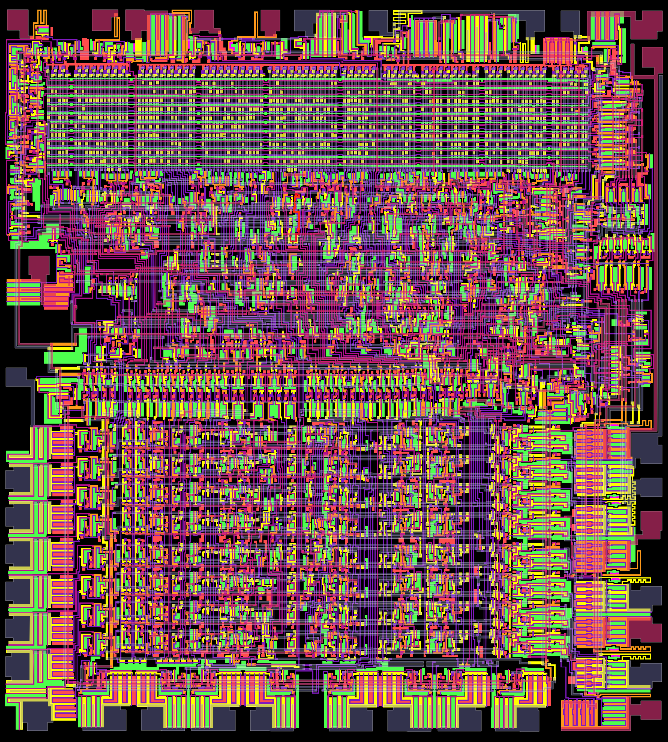

数字电路的拓扑抽象出来之后比较简单,就是线(Wire)和开关(Switch),门(Gate)也由开关组成。

线多了之后,看上去像网,所以Verilog里面的wire的Data Type为net。如果线是网,那么一个个开关及开关组成的门、门组成的寄存器,则可以看出是抽象的节点(Node)。

只有两点:

1.线串接各个节点;

2.节点上带有input/output/inout三种类型的接口(Port),供线连接;

二. 值的流动(Propagation)

拓扑是静态的,动态的是值的流动。数字电路关注最多的值是0和1,其他还有未知x和高阻z。

值经过线,流到连接的节点。根据节点的状态,值会发生反转、减弱,产生延迟传递到节点的输出线。或者被阻断,传不到下一条。或者输出值未改变,下一条未发现变化。等等。

三. 事件驱动

输入值的变化,根据自身状态,引起输出值的变化。此节点的输出值又作为下一节点的输入值,如此不停的传播。

每一个值的变化,即为一个事件,一个事件的发生,触发了对该事件的处理,该事件的处理,又产生新的事件。

如此,静态的拓扑模型为线和节点,动态的模型为事件驱动模型。

四. 各自为政

上电之后,电路的每一部分都是活的。每一个节点都有自己的输入、处理逻辑和输出,每一个节点只关注自己的输入,旁若无人的进行处理,然后自顾自的输出。这就是数字电路所为并行性的特点。

五. 并行性建模

数字电路各个组成部分的并行性,并不需要对之进行建模的语言也必须是并行性语言,这是一个很大的误区。

Verilog是并行性语言吗?不是。甚至Verilog本身并不能编译运行,只能靠EDA对模型进行解释,然后仿真。

Verilog只是对数字电路的各个模块、模块内的几段逻辑进行建模而已:

描述每个模块的输入、处理逻辑、输出;

描述不同模块的输入、输出连接情况;

仅此而已。任何语言都可以对此进行建模。

本文从拓扑角度解析数字电路的基本构成,介绍值的流动过程及其事件驱动特性,并探讨数字电路的并行性和Verilog语言在建模中的应用。

本文从拓扑角度解析数字电路的基本构成,介绍值的流动过程及其事件驱动特性,并探讨数字电路的并行性和Verilog语言在建模中的应用。

828

828

1240

1240

3099

3099

2356

2356

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?