引言

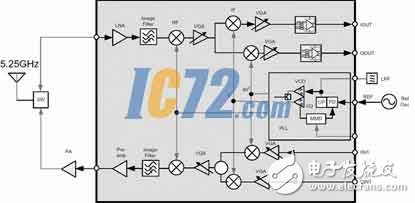

在当前通信市场的带动下,通信技术飞速向前发展,手持无线通信终端成为其中的热门应用之一。因此,单片集成的射频收发系统正受到越来越广泛的关注。典型的射频收发系统包括低噪声放大器(LNA)、混频器(Mixer)、滤波器、可变增益放大器,以及提供本振所需的频率综合器等单元模块,如图1 所示。对于工作在射频环境的电路系统,如2.4G 或5G 的WLAN 应用,系统中要包含射频前端的小信号噪声敏感电路、对基带低频大信号有高线性度要求的模块、发射端大电流的PA 模块、锁相环频率综合器中的数字块,以及非线性特性的VCO等各具特点的电路。众多的电路单元及其丰富的特点必然要求在这种系统的设计过程中有一个功能丰富且强大的设计平台。在综合比较后,本文选定了Cadence Virtuoso 全定制IC 设计工具。

本文详述了基于Cadence Virtuoso平台的单片射频收发集成电路设计流程,从行为仿真到系统规划,再到电路模块设计,最后进行版图设计与后仿真,强调了Virtuoso在射频IC设计中的关键作用。

本文详述了基于Cadence Virtuoso平台的单片射频收发集成电路设计流程,从行为仿真到系统规划,再到电路模块设计,最后进行版图设计与后仿真,强调了Virtuoso在射频IC设计中的关键作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

485

485

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?