开篇

编写高效的程序并不只在于算法的精巧,还应该考虑到计算机内部的组织结构,cpu微指令的执行,缓存的组织和工作原理等。

好的算法在实际中不见得有高效率,如果完全没有考虑缓存、微指令实现的话。

前两篇博文

局部性原理浅析 介绍了程序的局部性原理,如何写出局部性良好代码。

提高程序性能、何为缓存 讨论了存储器层次结构,计算机内部的存储结构、缓存的概念,简单的介绍了缓存的工作机制。

建议先阅读前两篇博文,虽然他们之间联系不大,在前面也有一些对本文的铺垫。而且,这是一个系列的文章。旨在优化程序性能。

这篇博文主要介绍的是缓存的组织、工作原理。拨开迷雾,让你更加清晰的认识缓存。

通用缓存结构

回顾

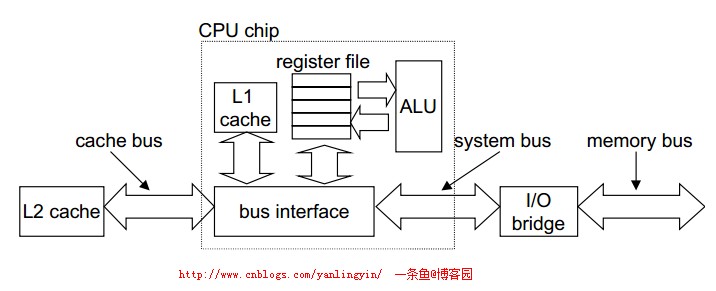

在提高程序性能、何为缓存中提到:早起的cpu存储层次只有三层,即cup的寄存器,DRAM主存和磁盘存储。因为寄存器和主存之间的访问时间开销差距很大,于是设计者在寄存器(一个时钟周期)和主存之间加入了L1缓存(2——4个时钟周期),后来由于L1缓存和主存之间的差距,又在主存和L1之间加入了L2缓存,当然后面还有L3缓存,,,等等。

在这里为了简单起见,假设CPU寄存器和主存之间只有一个L1缓存。

下图是高速缓存存储器的典型总线结构:

缓存结构

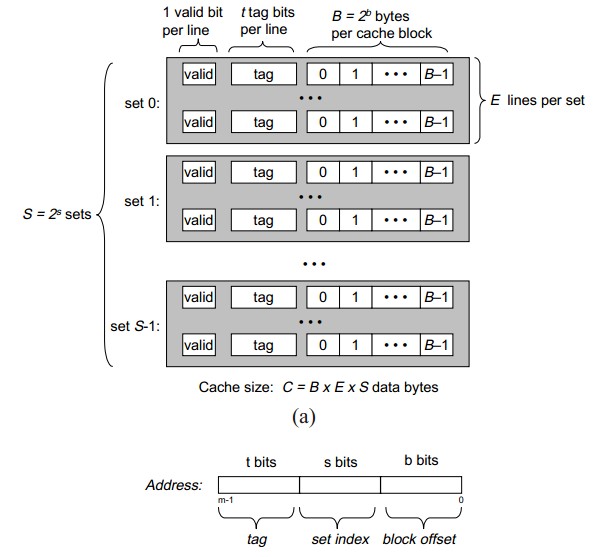

下图清晰的说明了通用缓存的组织结构:

可以看到,缓存内部是以组的形式组织的。图中的每一块代表一组,每组由一到多行组成(当然图中的是每组有多行)。

每一行包括

1 位标记位(valid bit)标明这行的信息是否有可用

t 位的标记,标明它是属于这一组的哪一行

剩下的空间是存储数据的数据的空间

可以看出在下面的图中把数据地址分为了三部分,左边 t 位是标记行号的,中间的 s 位标明组号,最后的 b 位则是数据块在行内的偏移量。

通常来说,缓存器可描述为(S; E; B; m)其中S为缓存中的组数,E为每组的行数,B为每行存储的字节数,m为缓存的地址位数。

所以缓存的容量为C=S

3181

3181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?