作者:因情语写

链接:https://proprogrammar.com/article/265

声明:请尊重原作者的劳动,如需转载请注明出处

一、概述

1、问题的提出

避免CPU“空等”现象

CPU和主存(DRAM)的速度差异

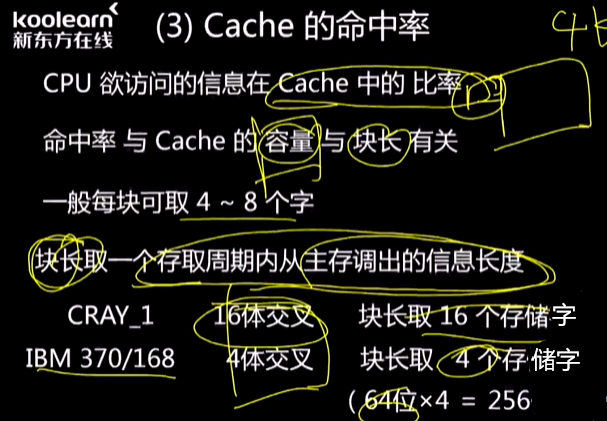

程序访问的局部性原理

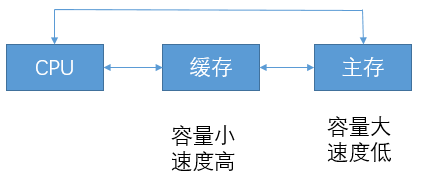

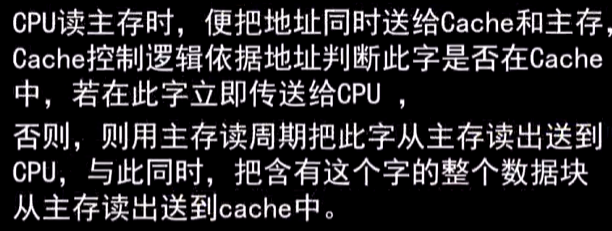

2、Cache的工作原理

从功能上看,是主存的缓冲存储器,由高速的SRAM组成。

Cache的设计依据

-CPU这次访问过的数据,下次有很大的可能也是访问附近的数据。

CPU与Cache之间的数据传送是以字为单位

主存与Cache之间的数据传送是以块为单位

主存称为块,Cache称为行,实质相同

3、Cache的基本结构

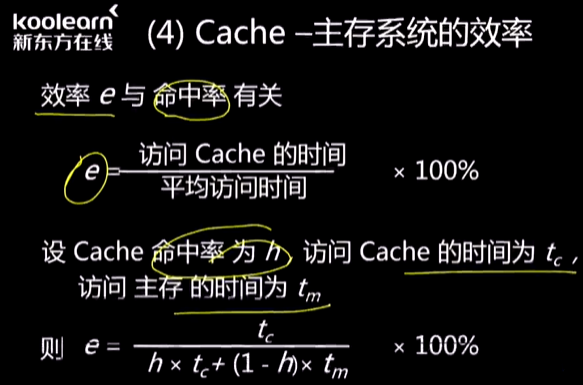

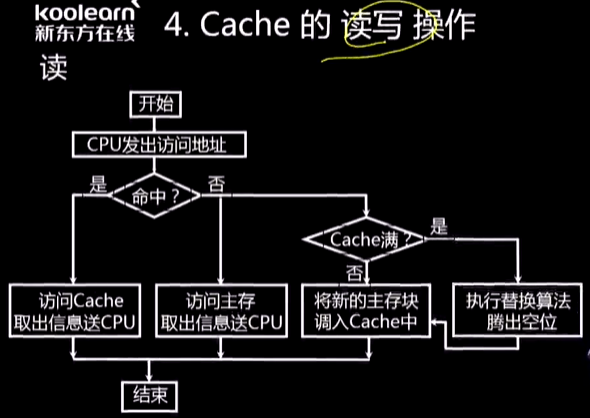

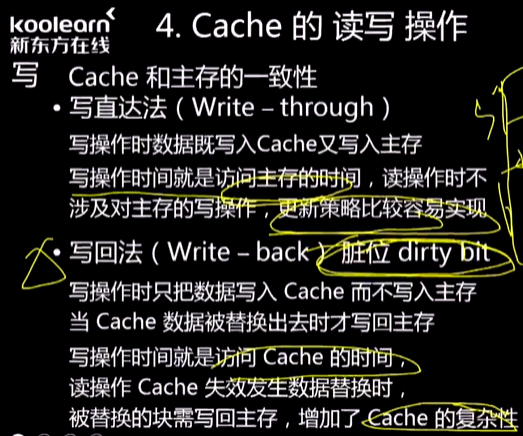

4、Cache的读写操作

5、Cache的改进

(1)增加Cache的级数

片载(片内)Cache

片外Cache

(2)统一缓存和分立缓存

指令Cache 数据Cache

与主存结构有关

与指令执行的控制方式有关 是否流水

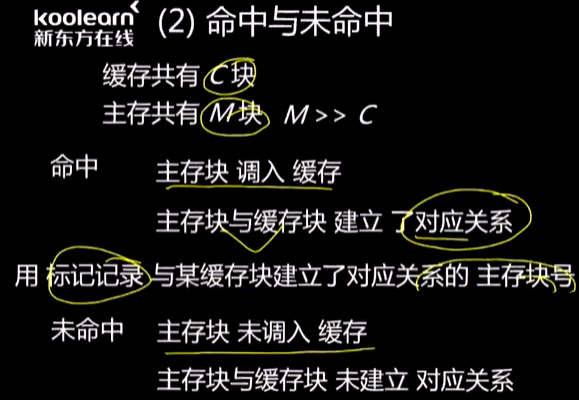

二、Cache-主存的地址映射

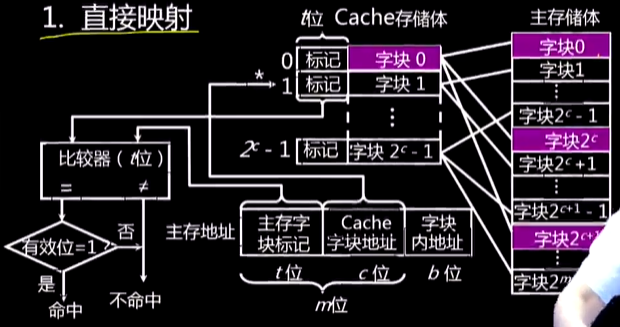

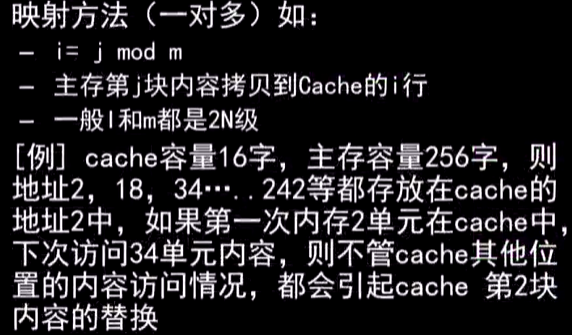

1、直接映射

i = j mod C

每个缓存块i可以和若干个主存块对应

每个主存块j只能和一个缓存块对应

这种对应关系是确定的 i = j mod C

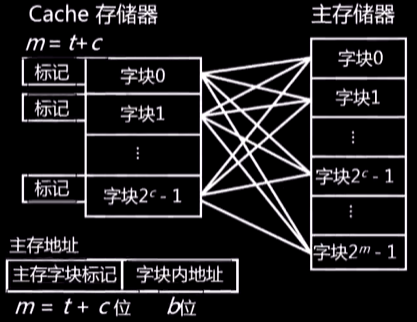

2、全相联映射

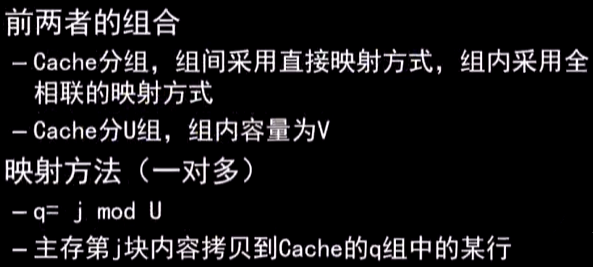

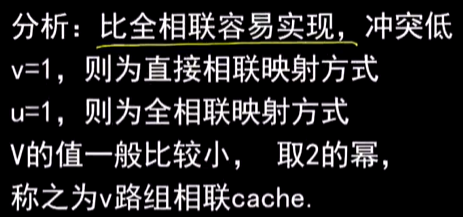

3、组相联映射

三、替换算法

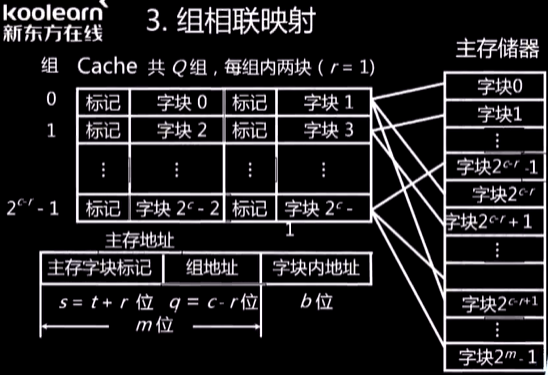

1、先进先出(FIFO)算法

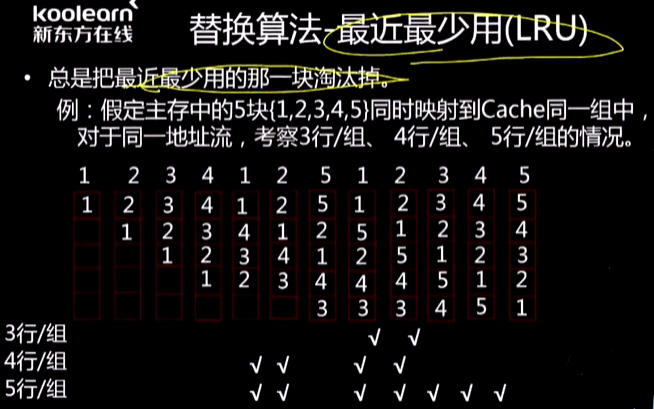

2、近期最少使用(LRU)算法

3、最不经常使用(LFU)算法

替换算法-先进先出(FIFO)

替换算法-最近最少用(LRU)

小结

直接 某一主存块 只能固定映射到某一缓存块

全相联 某一主存块 能映射到任一缓存块

组相联 某一主存块 只能映射到某一缓存组中的任一块

亲爱的读者:有时间可以点赞评论一下

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?