一、实验目的

1.掌握使用debug工具编写和调试汇编命令的方法。

2掌握1、2章所学的关于CPU、寄存器、内存和几条基础指令的用法。

二、实验内容

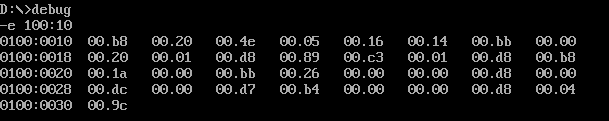

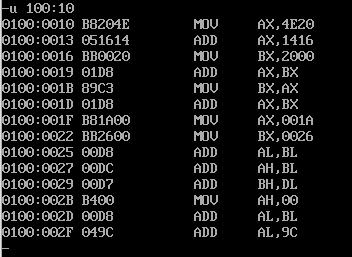

1、使用e命令将程序段写入内存。

然后我使用u命令调出查看,发现与书中的汇编指令一致。

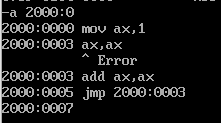

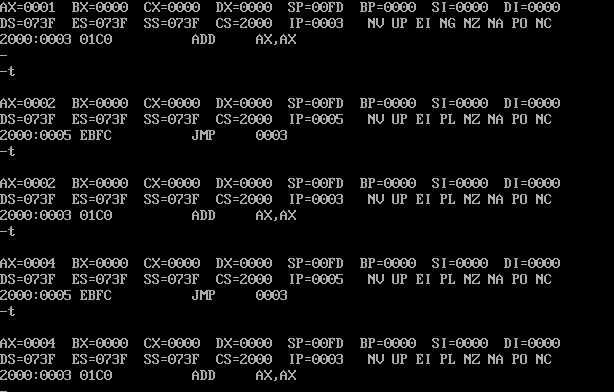

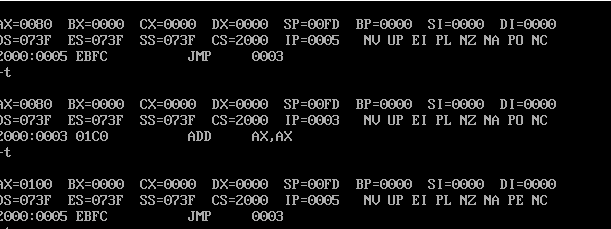

2.用书中的三条指令写入从2000:0开始的内存单元中,计算2的8次方。

由于我的输入失误,在输入的时候发生了错误,没有添加add指令,所幸对结果没有影响。

2进制中100是10进制的2的8次方即为256,结果正确。

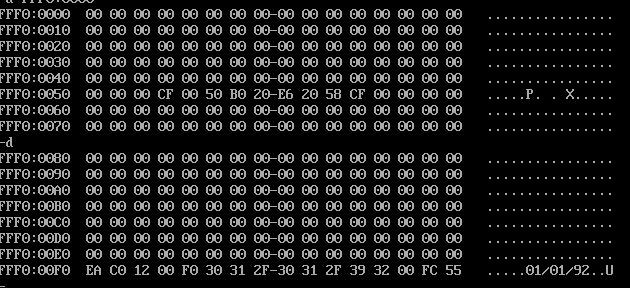

3.查看内存中的内容。

查找生产日期,我寻找了两次,在fff0:00f0上寻找到了日期。

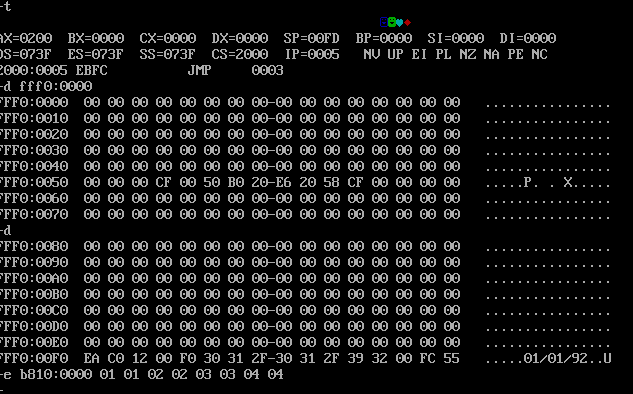

4.向内存从b8100h开始的单元中填数据。

可以发现在输入了书中的代码后,在我的界面上出现了4个图标,而当我改变地址是,他们会改变自己出现的位置,这几个代码其实代表的是图像出现的样子和颜色,地址则确定了他们出现的位置。

三、总结

在本次实验中,这是我们第一次使用debug环境来进行汇编代码的实现操作,在相比于课堂上的学习,实际操作更加能够让我充分了解汇编语言的使用。我在自己电脑上使用dosbox操作,界面无法放大,在操作观察和截图上不太方便。但还是学到了很多,之前光凭记忆无法理解的寄存器存储内容的变换,现在也能够理解了。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?