参考了 《Altera FPGA/CPLD 设计》高级篇, 关于状态机的推荐写法实现的功能是一样的但是编译使用的逻辑门如下图:

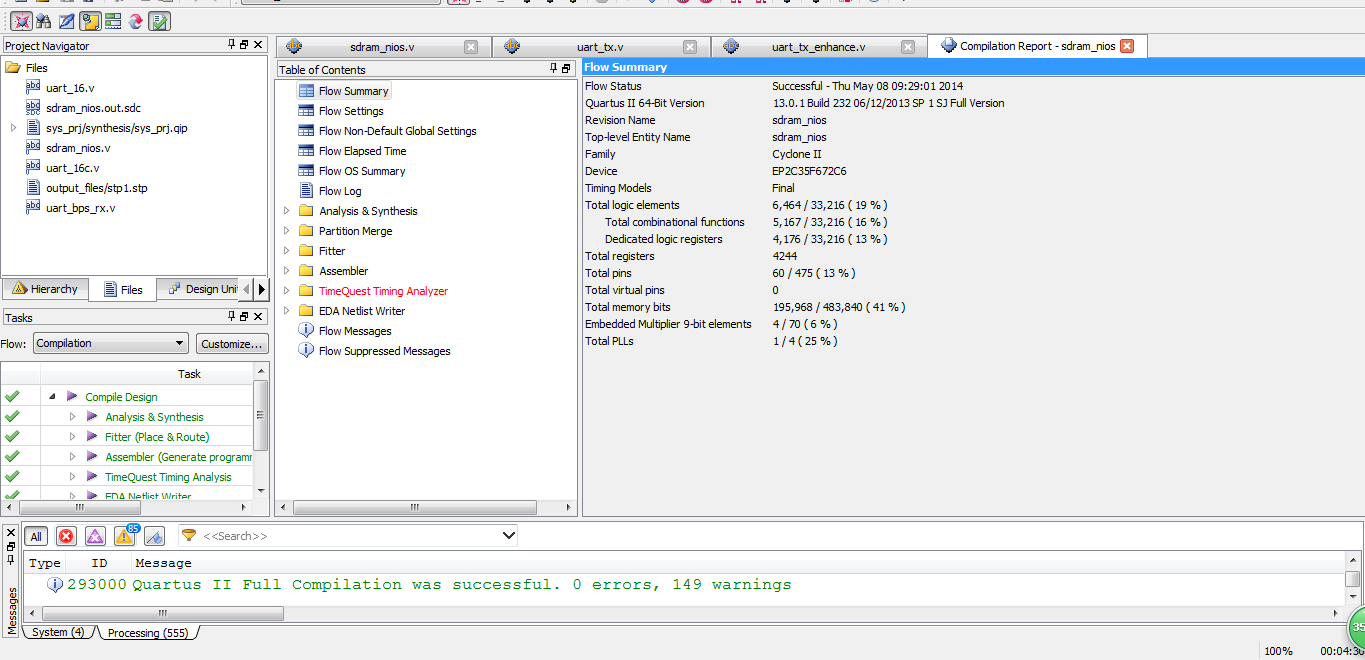

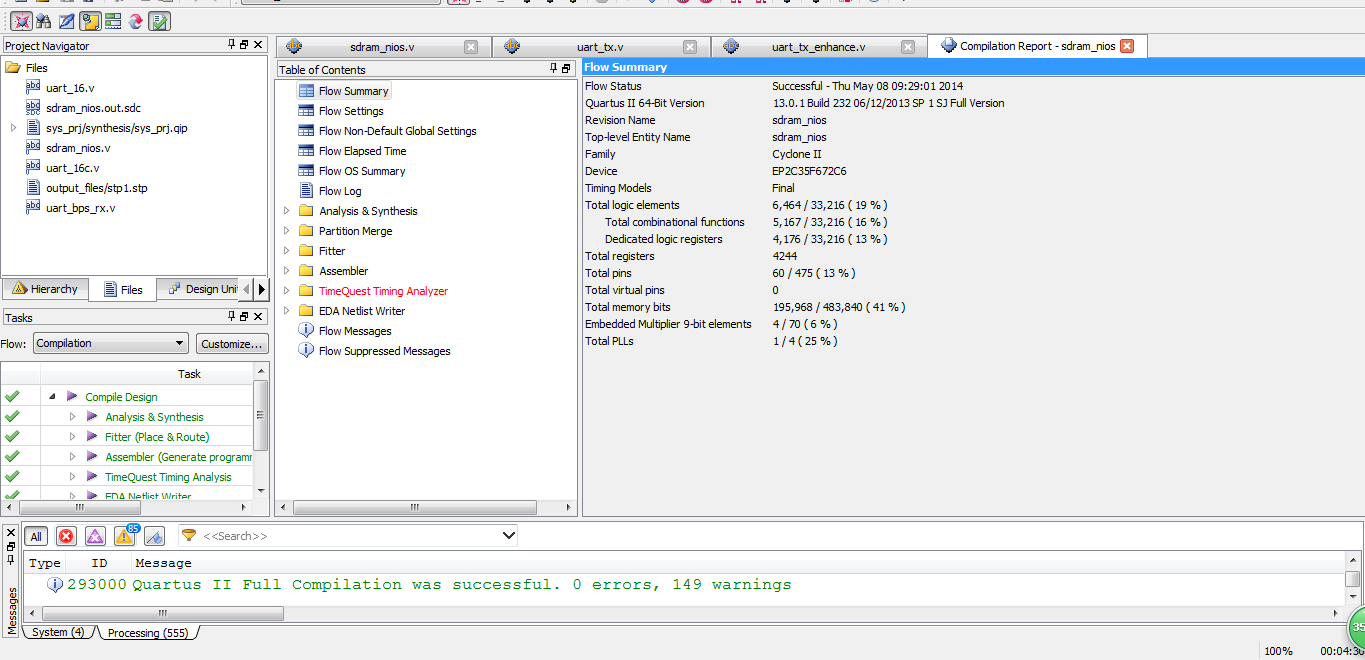

下图是我自己编的状态机需要的逻辑:

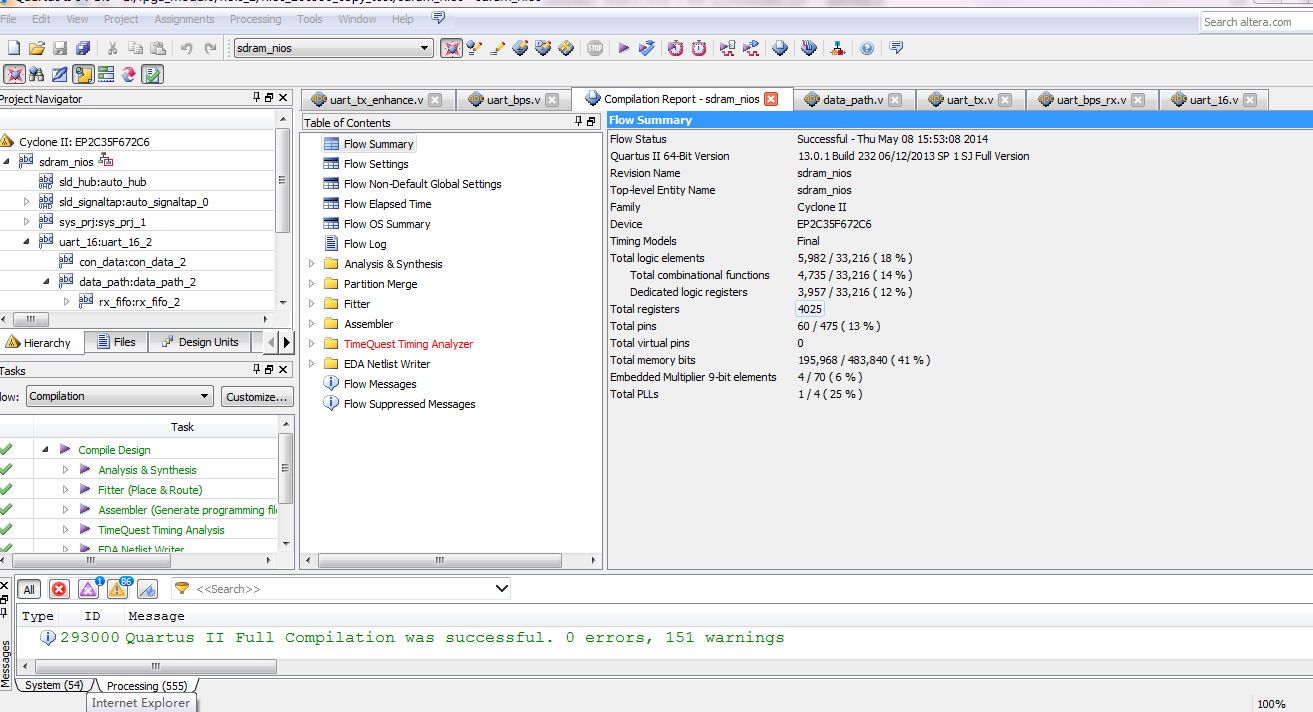

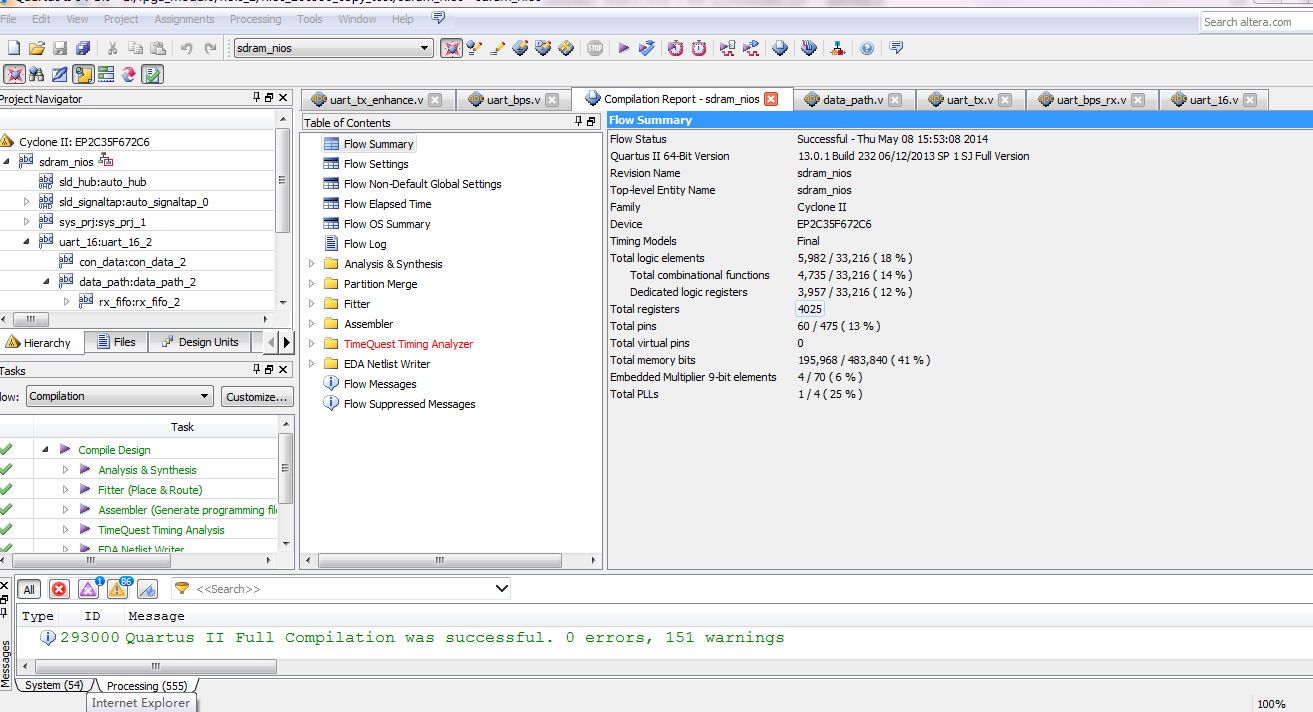

下图是使用推荐的有限状态机后,编译消耗的资源:

总结:推荐的有限状态机,分为2个always 块。 一个用于控制状态的转移,一个用于当前状态的操作。

本文通过对比两种状态机设计方法,展示了推荐的有限状态机如何有效减少逻辑门的使用,从而节省硬件资源。一种方法是在两个always块中实现状态转移与状态操作。

本文通过对比两种状态机设计方法,展示了推荐的有限状态机如何有效减少逻辑门的使用,从而节省硬件资源。一种方法是在两个always块中实现状态转移与状态操作。

参考了 《Altera FPGA/CPLD 设计》高级篇, 关于状态机的推荐写法实现的功能是一样的但是编译使用的逻辑门如下图:

下图是我自己编的状态机需要的逻辑:

下图是使用推荐的有限状态机后,编译消耗的资源:

总结:推荐的有限状态机,分为2个always 块。 一个用于控制状态的转移,一个用于当前状态的操作。

转载于:https://www.cnblogs.com/cornhill/p/3716396.html

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?