在进行工程调试的时候有时候需要对变量进行观察,SingnaTap II Logic Analyzer 只能对管脚进行观察,所以要观察内部的变量必须把内部的变量进行输出。一种方法是直接把变量定义成管脚通过signaltap II观察,一种是用显示器显示,另外一种是通过串口进行观察。本文主要写了串口发送的一些代码。

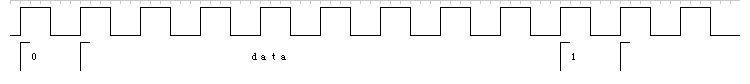

时序图:

起始位0 数据8bit 结束位1 一共10bit

输入50MHz通过megawizard 生成9600Hz比例系数为3/15625;

代码如下:

module RX232_IN(input clk_50,input [7:0] datain,output reg TX,input EN,output reg endtck,output clkout); wire clk9600; reg [7:0] temp1; reg [7:0] temp; reg [3:0] count=0; reg[1:0] num=0; alt_9600 M0(clk_50,clk9600); assign clkout=clk9600; always@(posedge clk9600) begin endtck<=1; case(num) 0:begin if(EN &endtck) begin num<=1;temp<=datain;end else num<=0; end 1:begin TX<=0;num<=2;temp1<=temp;end 2:begin count<=count+1;if(count<8) begin temp1<=temp1>>1;TX<=temp1[0];num<=2;end else begin endtck<=0;count<=0; num<=3;end end 3:begin TX<=1;endtck<=1;num<=0;end endcase end endmodule

验证代码:

module RX232(input clk_50,output TX,input EN,output endtck,output clk); wire [7:0] datain; assign datain=8'haa; RX232_IN M0(clk_50,datain,TX,EN,endtck,clk); endmodule

`timescale 1ns/1ns module testbench(); reg clk_50; reg EN; wire endtck; wire TX; RX232 M0(.clk_50(clk_50),.TX(TX),.EN(EN),.endtck(endtck)); initial begin clk_50=0;EN=0;#39 EN=1;end always begin #10 clk_50=!clk_50;end endmodule

串口通信模块设计

串口通信模块设计

本文介绍了一种基于FPGA的串口发送模块的设计方案,详细阐述了其工作原理及实现过程,并提供了完整的Verilog代码。该模块适用于工程调试中变量观察的需求。

本文介绍了一种基于FPGA的串口发送模块的设计方案,详细阐述了其工作原理及实现过程,并提供了完整的Verilog代码。该模块适用于工程调试中变量观察的需求。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?