到现在我还是不太理解SDRAM的时序设置,但是可能蒙对了。(呵呵)

开发环境: quartus II 13.0 板子: DE2 EP2C35F672C6N

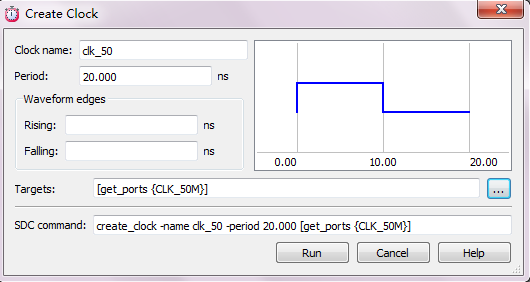

时序约束step 1:create clock: 50MHZ

时序约束step 2: virtual clock(原因:timequest不知道外接时钟的属性,即要实在的指出。并要对之约束)

时序约束step 3: set output delay , set input delay (这是最难的,个人认为)

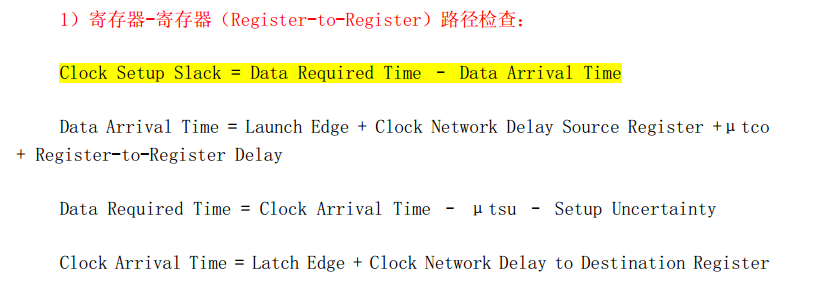

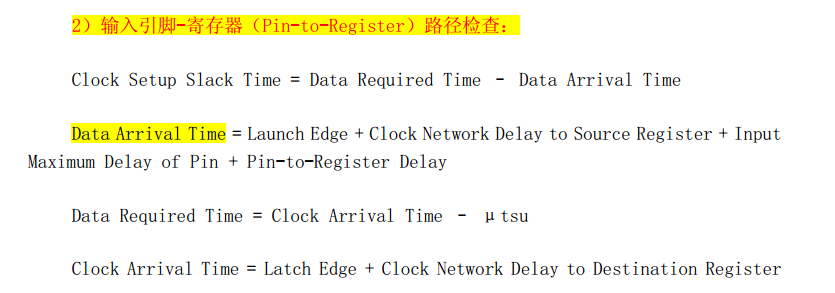

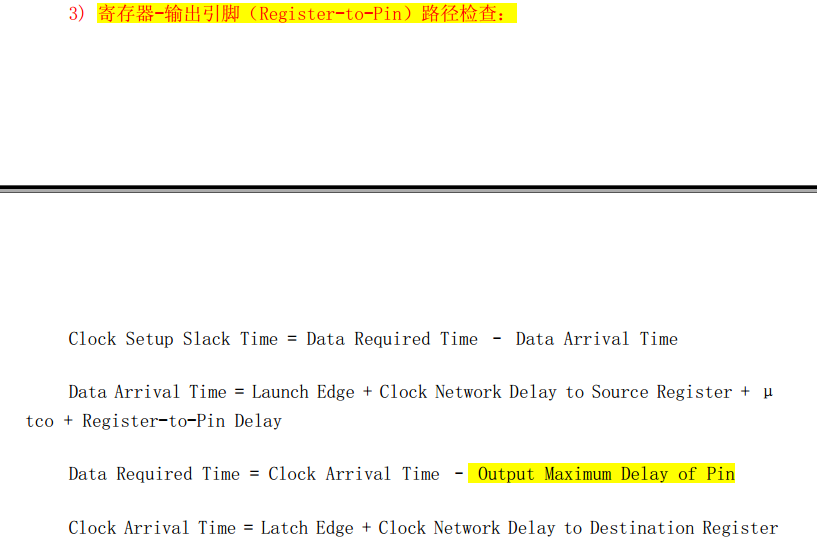

先理解: setuptime 有三类

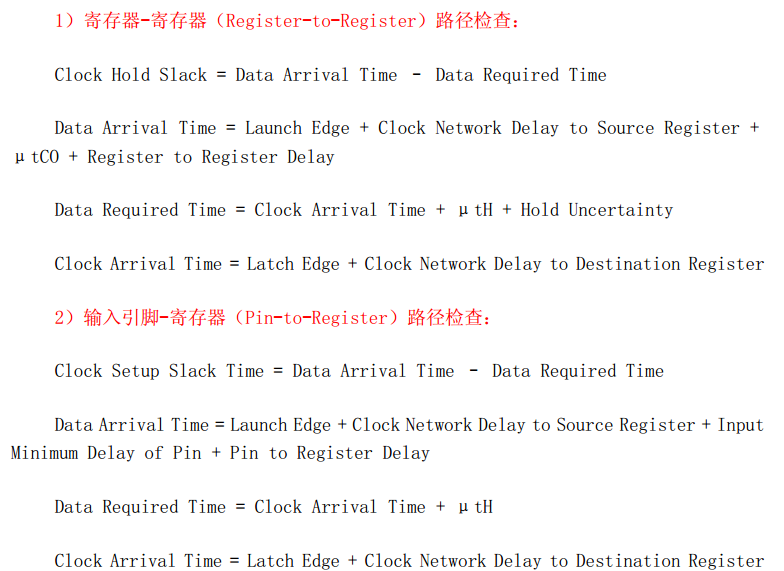

hold time :

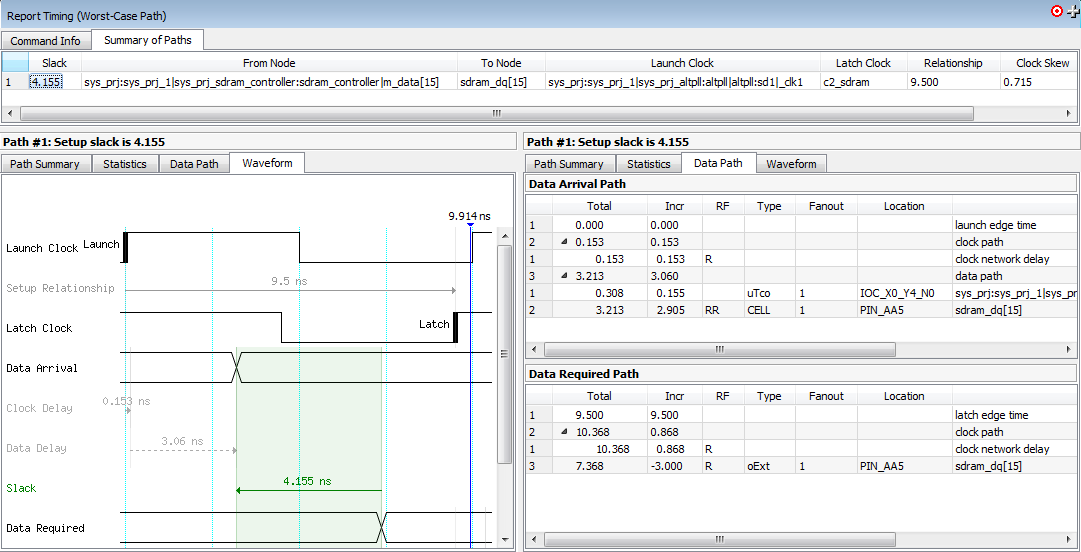

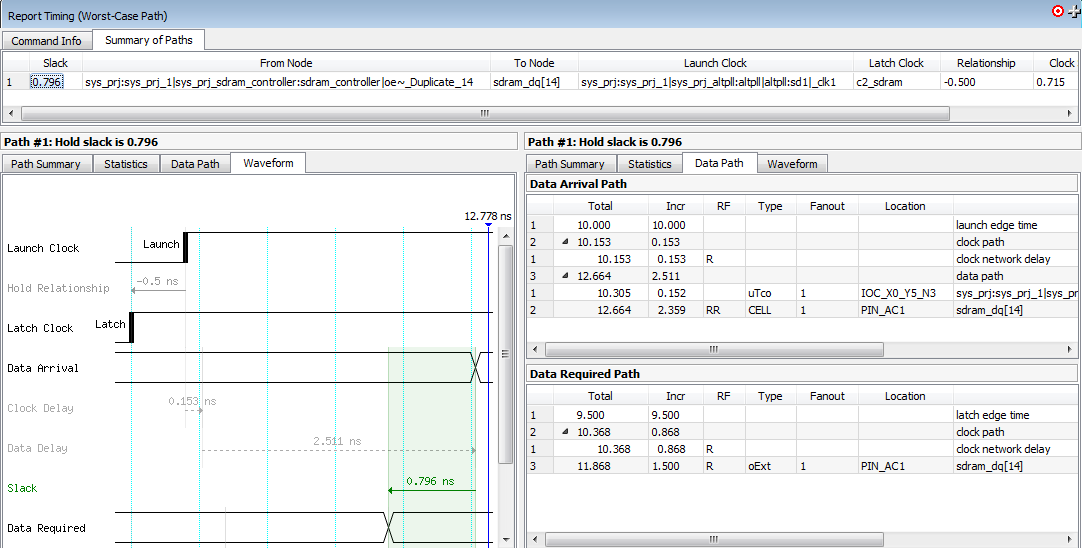

还要结合具体的分析如:(原因:有些延时是找不到的,如clock network delay to destionation register)最终确定output max delay , min delay。 当然,我觉得分析后猜猜也可以。

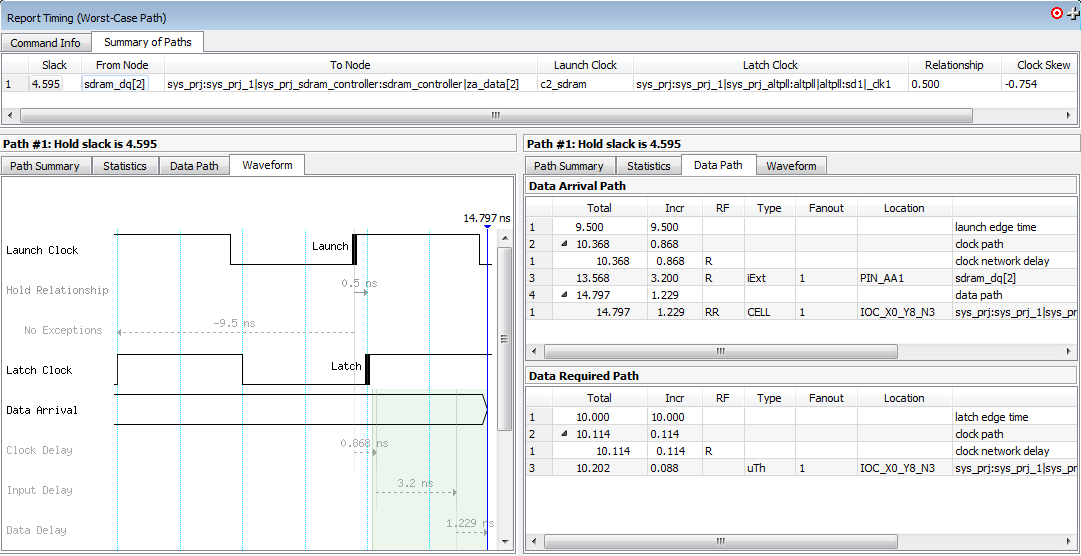

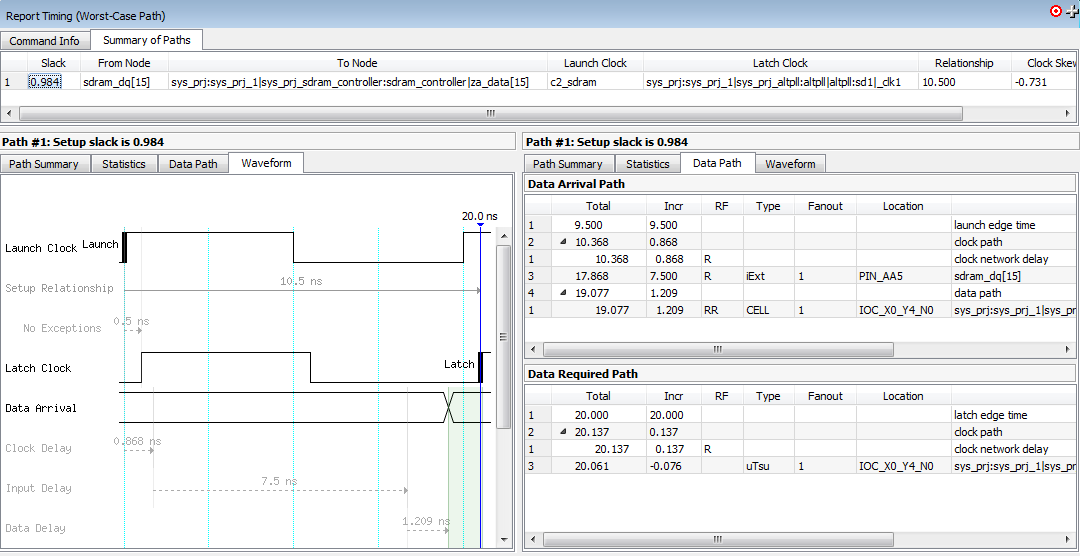

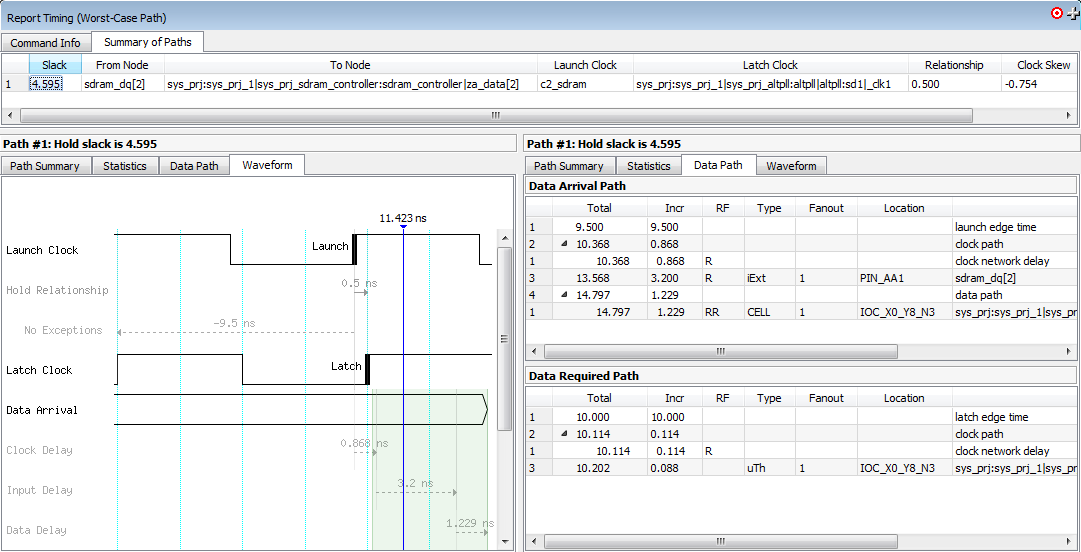

我是想写写这个图是如何分析的,但我现在也不是很懂(*^_^* )等到我能写的时候我再写写这个如何分析。

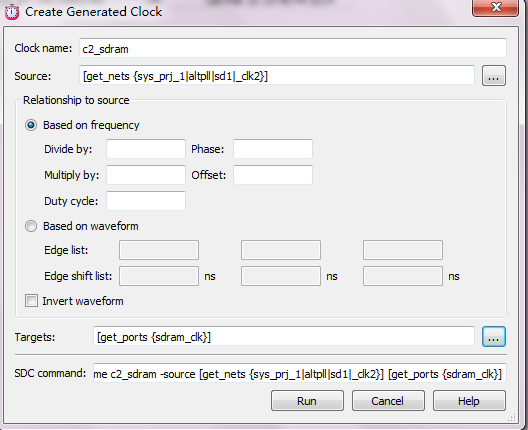

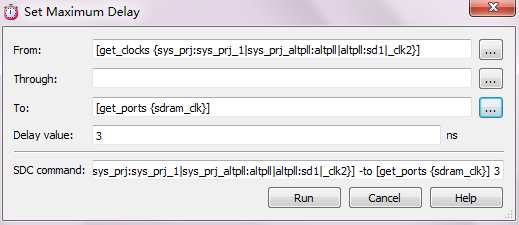

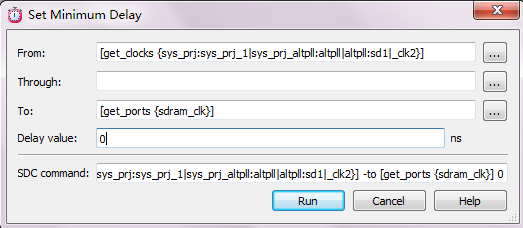

时序约束step 4: sdram_clk 即clk2的相移 这部分也是难点 先给出结果

如何分析:

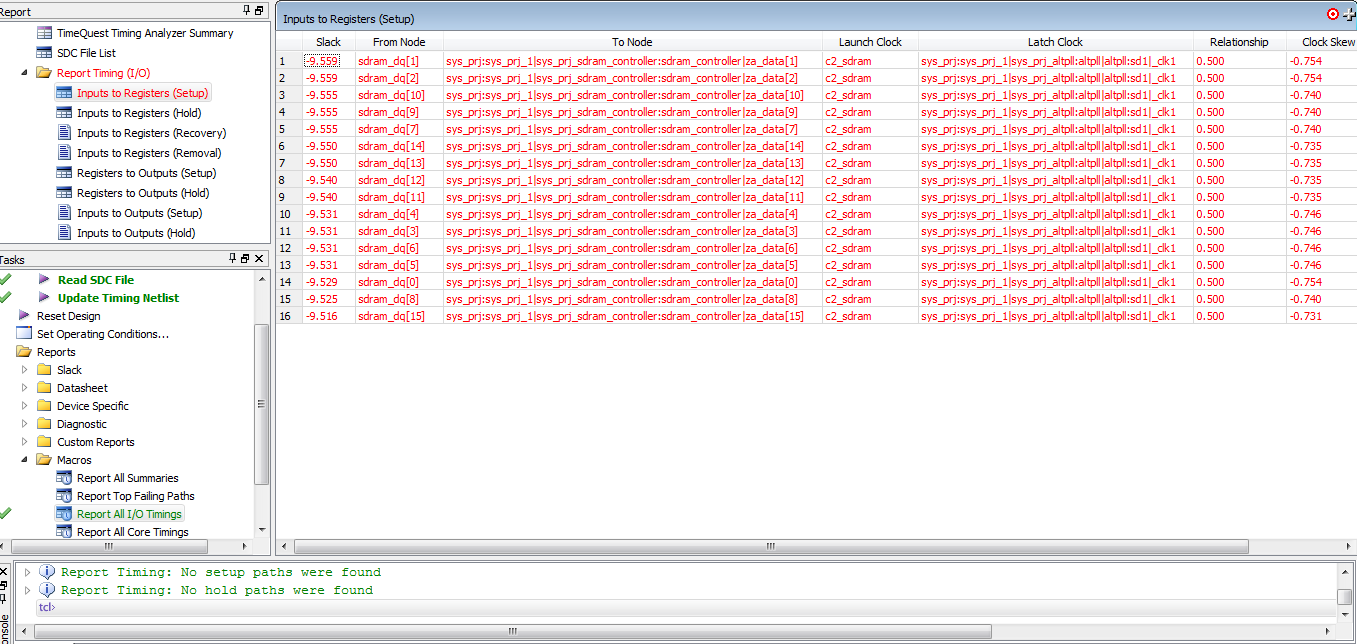

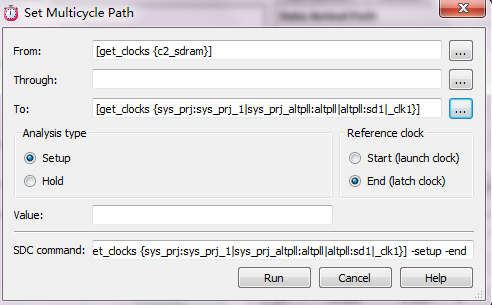

时序约束step 5:set multicycle 根据提示设置相关时钟的多周期

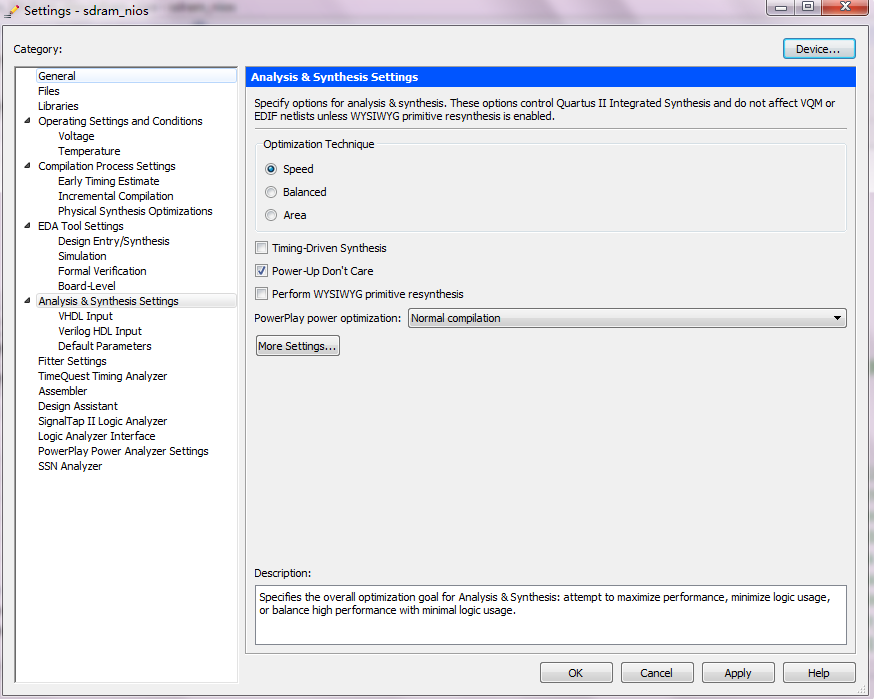

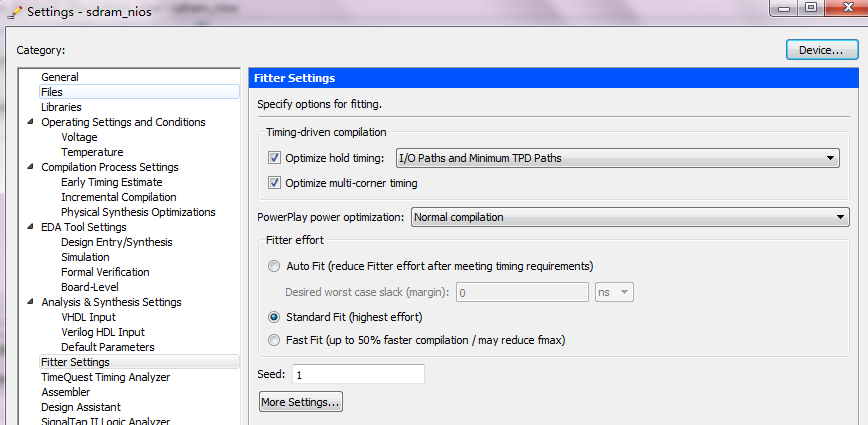

时序约束step 6:时序收敛的优化到此时,对于 sdram的时序约束应该说是结尾了,但是对于这个工程的时序收敛还是可以优化的。

SDRAM的时序和系统时序约束到此结束了。。。。。。。O(∩_∩)O

SDRAM时序设置详解:从入门到进阶

SDRAM时序设置详解:从入门到进阶

本文深入解析SDRAM时序设置的关键步骤,包括虚拟时钟、输出延迟、输入延迟等,旨在帮助开发者理解并优化SDRAM在Quartus II开发环境中的时序约束。

本文深入解析SDRAM时序设置的关键步骤,包括虚拟时钟、输出延迟、输入延迟等,旨在帮助开发者理解并优化SDRAM在Quartus II开发环境中的时序约束。

1564

1564

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?