在数字信号处理中往往都需要进行大量的数字运算,比如,数字信号的解调,需要采集大量的IQ数据对其进行解调运算。在实际的研究和学习中我们一般会在操作系统中利用丰富的软件给我们提供的便捷的计算工具进行计算(Matlab、Python等),这可以很方便的处理我们所研究的数字信号。然而,学过计算机原理或者汇编语言的同学会清楚,数据的运算的最终是在计算机硬件上来完成的,我们在操作系统层面的数据运算往往意味着需要进行大量的资源的调度。虽然现在的计算机的性能已经非常的强大,但是对于面向应用的产品来说,其处理器性能往往和计算机不能相提并论。通常,在通信、图像等数字信号处理中,会采用硬件芯片的方式进行数据运算(DSP、FPGA等),通过这种硬件芯片上进行数字信号运算,可以很好的提高运算效率,这也在工程应用中广为采用的一种方式。在这些处理器中往往各种数据都是通过整数形式存储(比如,通信中的IQ数值的存储)。实际上,我们需要进行运算的数据大多都是小数,那么,该怎么解决呢?一般的我们可以通过定点数这种方式来表示小数。

什么是定点数

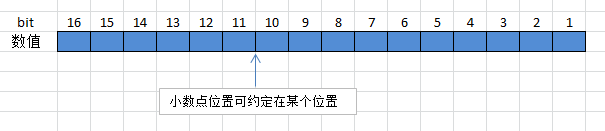

定点数英文名叫Fixed Point Number,其关键地方就在定和点这两个字上面,即在表示小数数据时,把小数点的位置已经约定好固定在某个位置。与之对应的是浮点数,其小数点的位置不是固定的,关于浮点数先不做展开。

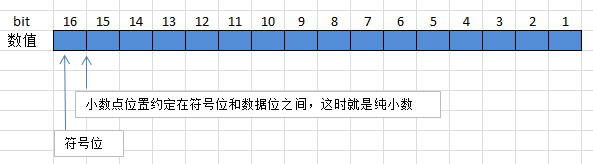

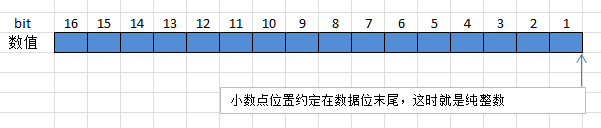

在定点数中,小数点可以将数据分为整数和小数部分,因此我们可以约定小数点在数据中的不同位置,就可以表示不同大小和精度的小数。例如,当小数点位置约定在符号位和数值位之间,就表示纯小数;当小数点约定在最末尾位置时,就可以表示纯整数。

如何描述定点数的这种规则呢?其实,我们可以使用两种方法来表示:

- Q来表示法

Qx,x表示小数的位数。 - S表示法

Sx.y,x表示整数位数,y表示小数位数。

我们知道在计算机中根据是否存在符号位可以分成无符号整数和有符号整数,当然,对于定点数也可以根据有无符号位分为:

- 无符号定点数:无符号位

- 有符号定点数:有符号位

无符号定点数

无符号定点数,数值在机器中字长的全部二进制位中没有符号位,全都是数值位。例如,小数1.2转换成16位的定数,小数点的位置约定在第14位和第15位之间。

x∗2n=1.2∗214=19660.8=19661 x*2^n = 1.2*2^{14} = 19660.8 = 19661 x∗2n=1.2∗214=19660.8=19661

本文介绍了定点数在数字信号处理中的重要性,特别是在硬件芯片上的高效运算。定点数是一种固定小数点位置的数字表示方法,包括无符号和有符号定点数,涉及原码、反码和补码的概念。通过Q表示法和S表示法来描述定点数的规则,并举例说明如何将小数转换为定点数。定点数在工程应用中的优势在于其运算效率高和节省存储资源。

本文介绍了定点数在数字信号处理中的重要性,特别是在硬件芯片上的高效运算。定点数是一种固定小数点位置的数字表示方法,包括无符号和有符号定点数,涉及原码、反码和补码的概念。通过Q表示法和S表示法来描述定点数的规则,并举例说明如何将小数转换为定点数。定点数在工程应用中的优势在于其运算效率高和节省存储资源。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

917

917