SPIBlock GuideV03.06

Section 1 介绍

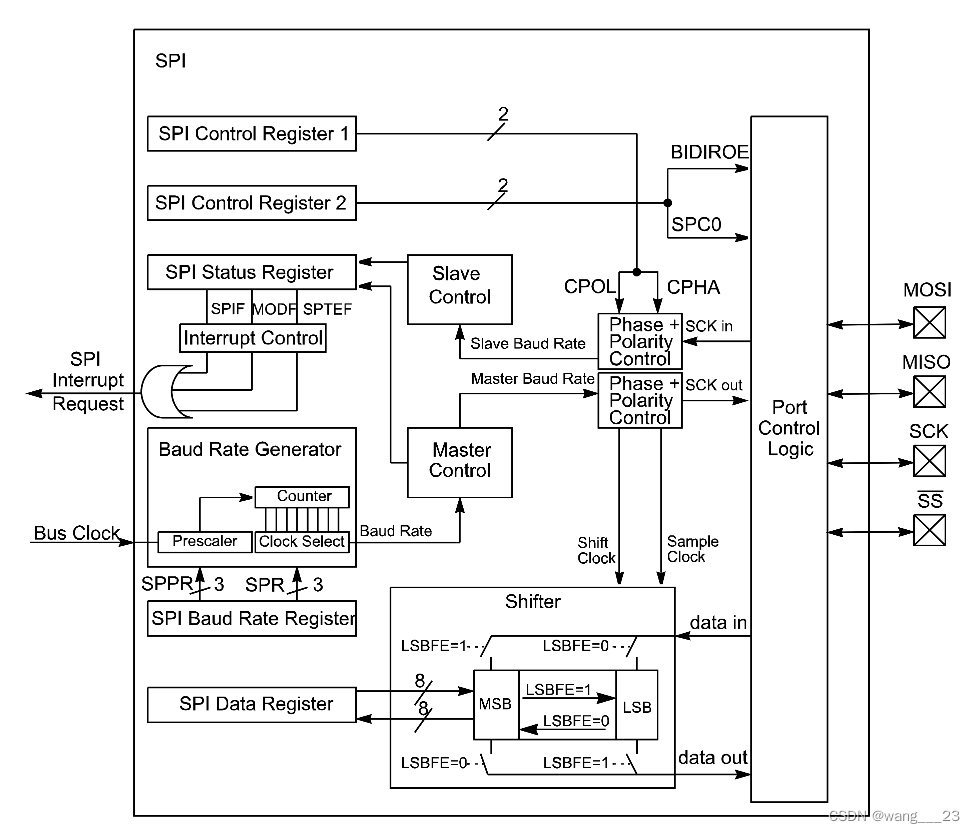

图给出了SPI架构的概述。SPI的主要部分是状态寄存器、控制寄存器和数据寄存器、移位逻辑、波特率发生器、主从控制逻辑和端口控制逻辑。

1.1 概述

SPI模块允许在MCU和外设之间进行双工、同步、串行通信设备。软件可以轮询SPI状态标志或SPI操作可以中断驱动。

1.2 Features

SPI包括以下特点:

主模式和从模式

双向模式

从机选择输出

具有CPU中断能力的模式错误标志

双缓冲数据寄存器

具有可编程极性和相位的串行时钟

在等待模式下控制SPI操作

1.3 Modes of Operation

SPI有运行、等待和停止三种模式。

运行模式

这是基本的操作方式。

等待模式

等待模式下的SPI操作是一种可配置的低功耗模式,由SPICR2寄存器中的SPISWAI位控制。在等待模式下,如果SPISWAI位被清除,SPI就像在运行模式下一样工作。如果SPISWAI位被设置,SPI进入功率保守状态,SPI时钟产生关闭。

如果SPI配置为master,则任何正在进行的传输都将停止,但在CPU进入Run Mode后将恢复。

如果SPI被配置为salve,则继续接收和传输字节,以便从站与主站保持同步。

停止模式

SPl在停止模式下处于非活动状态,以降低功耗。

如果SPl配置为master,则任何正在进行的传输都将停止,但在CPU进入Run Mode后将恢复传输。

如果SPI被配置为salve,则继续接收和传输字节,以便从站与主站保持同步。

这只是一个高层次的描述,对工作模式的详细描述包含在4.8低功耗模式选项中。

Section 2 外部信号描述

本节列出所有端口的名称和描述,包括连接或可能连接芯片的输入和输出。SPI模块共有4个外部引脚。

2.1 概述

本节列出所有端口的名称和描述,包括连接或可能连接芯片的输入和输出。SPI模块共有4个外部引脚。

2.2 信号详细描述

2.2.1 MOSI

该引脚用于在SPI模块配置为Master时将数据发送出去,并在配置为Slave时接收数据。

2.2.2 MISO

该引脚用于在SPI模块配置为Slave时将数据发送出去,并在配置为Master时接收数据。

2.2.3 SS

该引脚用于从SPI模块输出选择信号到另一个外设,当其配置为主设备时,数据传输将发生,当SPI配置为从设备时,它用作接收从设备选择信号的输入。

2.2.4 SCK

该引脚用于输出SPI传输数据的时钟或在Slave情况下接收时钟。

Section 3 内存MAP/寄存器 定义描述

本节提供了SPI使用的地址空间和寄存器的详细描述。

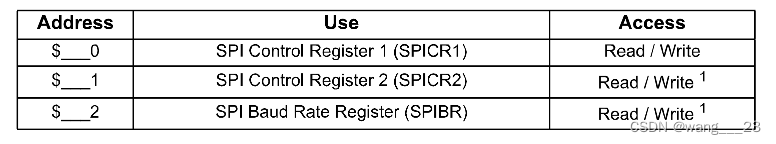

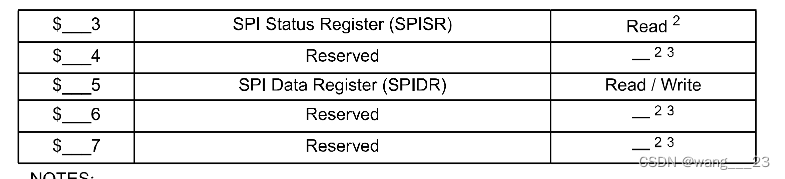

SPI的内存映射如下表所示。为每个寄存器列出的地址是一个基址和一个地址偏移量的总和。基址是在SoC级定义的,地址偏移量是在模块级定义的。从保留位读取将返回零,而向保留位写入则没有效果。

注:1. 某些位是不可写的。2. 对该寄存器的写入将被忽略。3.从这个寄存器读取返回全零。

3.1 寄存器描述

本节由按地址顺序排列的寄存器描述组成。每个描述包括一个标准的寄存器图和一个相关联的图号。寄存器位和域函数的详细信息按照寄存器图,按位顺序排列。

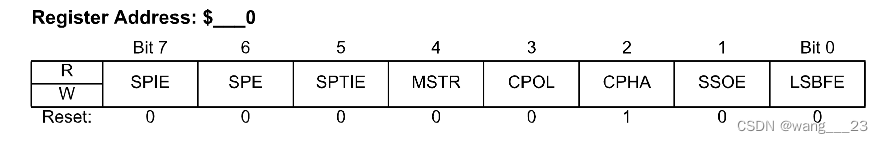

3.1.1 SPI Control Register 1

Read: anytime

Write: anytime

SPIE- SPI Interrupt Enable Bit

如果设置了SPIF或MODF状态标志,该位启用SPI中断请求。

1=SPI中断使能。

0=禁用SPI中断。

SPE-- SPI Systcm Enable Bit

该位启用SPI系统,并将SPI端口引脚专用于SPI系统功能。如果SPE被清除,SPI将被禁用并强制进入空闲状态,SPISR寄存器中的状态位被重置0 = SPI禁用(低功耗)。

1 =启用SPI,端口引脚专用于SPI功能。

0=禁用SPI(低功耗)。

本文围绕SPI模块展开,介绍其可在MCU和外设间进行双工、同步、串行通信,有主从模式。阐述了运行、等待和停止三种操作模式,描述了外部信号、内存MAP/寄存器定义。还说明了功能、波特率生成、特殊功能、错误条件及低功耗模式选项等内容。

本文围绕SPI模块展开,介绍其可在MCU和外设间进行双工、同步、串行通信,有主从模式。阐述了运行、等待和停止三种操作模式,描述了外部信号、内存MAP/寄存器定义。还说明了功能、波特率生成、特殊功能、错误条件及低功耗模式选项等内容。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

515

515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?