了解一款芯片,最基本的就是要了解它的寄存器。大家不要因为80386是32位处理器,就认为它的寄存器都是32位的。其实它的寄存器相当的复杂。不仅有32位的,还有16位的,48位的,乃至64位的。80386共有34个寄存器,可分为七类。它们分别是通用寄存器、指令指针和标志寄存器、段寄存器、系统地址寄存器、控制寄存器、调试和测试寄存器。以下是部分常用的寄存器:

一、通用寄存器(8个)

80386有8个32位的通用寄存器,这8个通用寄存器都是由8088/8086/80286的相应16位通用寄存器扩展成32位而得。名字分别是:EAX,EBX,ECX,EDX,ESI,EDI,EBP,ESP。每个寄存器可以掰成两个16位寄存器使用,也可以掰成4个8位寄存器使用。

二、指令指针和标志寄存器(2个)

80386的指令指针EIP是一个32位寄存器,是从8086的IP扩充而来。

80386的标志寄存器EFLAGS也是一个32位寄存器,其中只使用了15位,从8086的FLAGS寄存器扩展而来。如下图所示。

三、段寄存器(6个)

80386有6个段寄存器,分别是CS,DS,SS,ES,FS和GS,是16位寄存器。前4个段寄存器的名称与8088/8086相同,在实地址方式下使用方式也和8088/8086相同。80386又增加了FS与GS,主要为了减轻对DS段和ES段的压力。

四、控制寄存器(4个)

80386有4个32位控制寄存器(CR0、CR1、CR2和CR3)。它们的作用是保存全局性的机器状态。其中CR0的格式如下图所示。

CR0的低16位称为机器状态字MSW,其中:

PE 保护允许位。进入保护方式时PE=1。除复位外,不能被清除。实方式时PE=0。

PG 页式管理允许位。PG=1表示启用芯片内部的页式管理系统,否则PG=0。

其余的三个控制寄存器的作用是:CR1由Intel公司保留,CR2存放引起页故障的线性地址,CR3存放当前任务的页目录基地址(页目录基址寄存器)。

五、系统地址寄存器(4个)

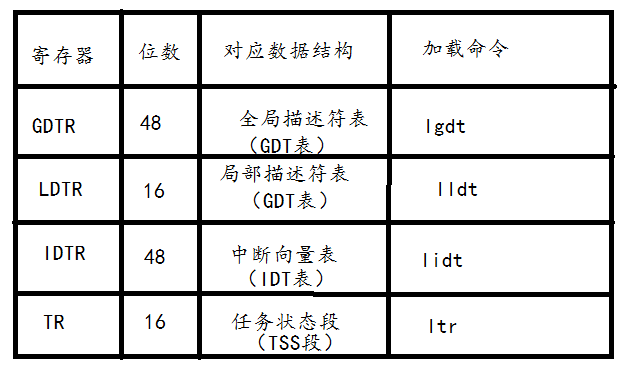

80386有4个系统地址寄存器,用来存储操作系统需要的保护信息和地址转换表信息、定义目前正在执行任务的环境、地址空间和中断向量空间。

GDTR 48位全局描述符表寄存器,用于保存全局描述符表的32位基地址和全局描述符表的16位界限(全局描述符表最大为216字节,共2^16/8=8K个全局描述符)。

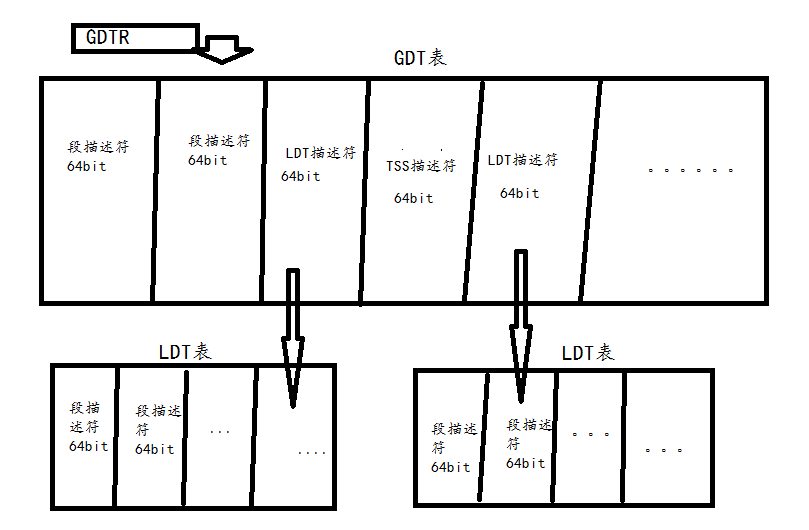

注:GDT表里面的每一项都表明一个段的信息,或者是一个LDT表的相关信息。其实一个LDT表也是一个段。所以也可以说GDT表的每一项都描述一个段。就像一个文件夹下面可以有文件,也可以有文件夹一样,GDT表里面既可以有段描述符,也可以有LDT的表。

IDTR 48位中断描述符表寄存器,用于保存中断描述符表的32位基地址和中断描述符表的16位界限(中断描述符表最大为216字节,共2^16/8=8K个中断描述符)。

LDTR 16位局部描述符表寄存器,用于保存局部描述符表的选择符。一旦16位的选择符(也叫选择子)放入LDTR,CPU会自动将选择符所指定的局部描述符装入64位的局部描述符寄存器中。

TR 16位任务状态段寄存器,用于保存任务状态段(TSS)的16位选择符。与LDTR类似,一旦16位的选择符放入TR,CPU会自动将该选择符所指定的任务描述符装入64位的任务描述符寄存器中。

注:TSS是一个段,所以在GDT中有对应的表项描述。

LDTR和TR寄存器是由16位选择字段和64位描述符寄存器组成。用来指定局部描述符表和任务状态段TSS在物理存储器中的位置和大小。64位描述符寄存器是自动装入的,程序员不可见。LDTR与TR只能在保护方式下使用,程序只能访问16位选择符寄存器。(注意区分描述符表寄存器与描述符寄存器)

可以看到IDTR也是48位的(大于32位),与GDTR位数一样,大于32位的结构自然就有4G内任意寻址的能力。所以理论上我们可以直接访问中断向量表,不需要通过选择子(16位结构)来间接寻找。所以IDT表可以与GDT表完全独立,不需要像LDT一样还要在GDT表建立相关表项。但是TSS段和LDT表两个结构就不行,他们的寄存器只有16位,不可能在4G内存中任意寻址,所以只能将其插入到GDT表中,然后借用GDT和自身的选择子的组合来间接寻址。

参考:http://mcit.xjtu.edu.cn/wlkj/wykj/ch2/ch2_4_1.htm

本文详细介绍了80386处理器的寄存器构成,包括通用寄存器、指令指针和标志寄存器、段寄存器、控制寄存器、系统地址寄存器等类别,以及各寄存器的功能和用途。

本文详细介绍了80386处理器的寄存器构成,包括通用寄存器、指令指针和标志寄存器、段寄存器、控制寄存器、系统地址寄存器等类别,以及各寄存器的功能和用途。

1766

1766