基于单电子晶体管的二进制与四进制低功耗选择电路的设计与实现

摘要

本文介绍了单电子晶体管(SET)低功耗算术 & 逻辑选择单元的性能分析。SET 是一种低功耗器件,可用于实现仅用 CMOS 电路几乎无法实现的新功能。设计并验证了高效的 SET 4:1 多路复用器,同时提出了四进制选择电路。此外,还验证了一位全加器、与门、或门和异或门。仿真使用了 SPICE、OrCAD 和 Matlab。与 CMOS 相比,单电子晶体管尺寸更小,运行速度更高,且功耗更低。

关键词

库仑阻塞,单电子晶体管,SPICE,互补金属氧化物半导体(CMOS)

I. 引言

A. 互补金属氧化物半导体(CMOS)技术的功耗限制

与功耗相关的能量和热问题现在在电子领域中处于核心地位系统设计。在高性能应用中,温度会影响集成密度、性能、可靠性、功耗和成本。对于电池供电嵌入式系统,能耗直接决定了系统使用寿命。历史上,功耗危机通过转向新技术得以解决,这些技术提高了每次操作的能量效率,从而提升了密度并最终提升了性能。功率和热问题是在20世纪60年代用半导体器件取代真空管以及在20世纪90年代用互补金属氧化物半导体(CMOS)取代双极结型晶体管(BJT)的主要动因之一。CMOS是当今主流的制造技术。随着集成电路(IC)集成度的进一步提高,将很快达到制造、功耗和热极限;可能很快就会迎来向一种截然不同的技术的过渡[8]。

B. 单电子晶体管

单电子晶体管是一种纳米器件,由于具有低功耗和尺寸可扩展性集成的优势,为未来的超大规模集成电路(ULSI)提供了巨大的潜力。

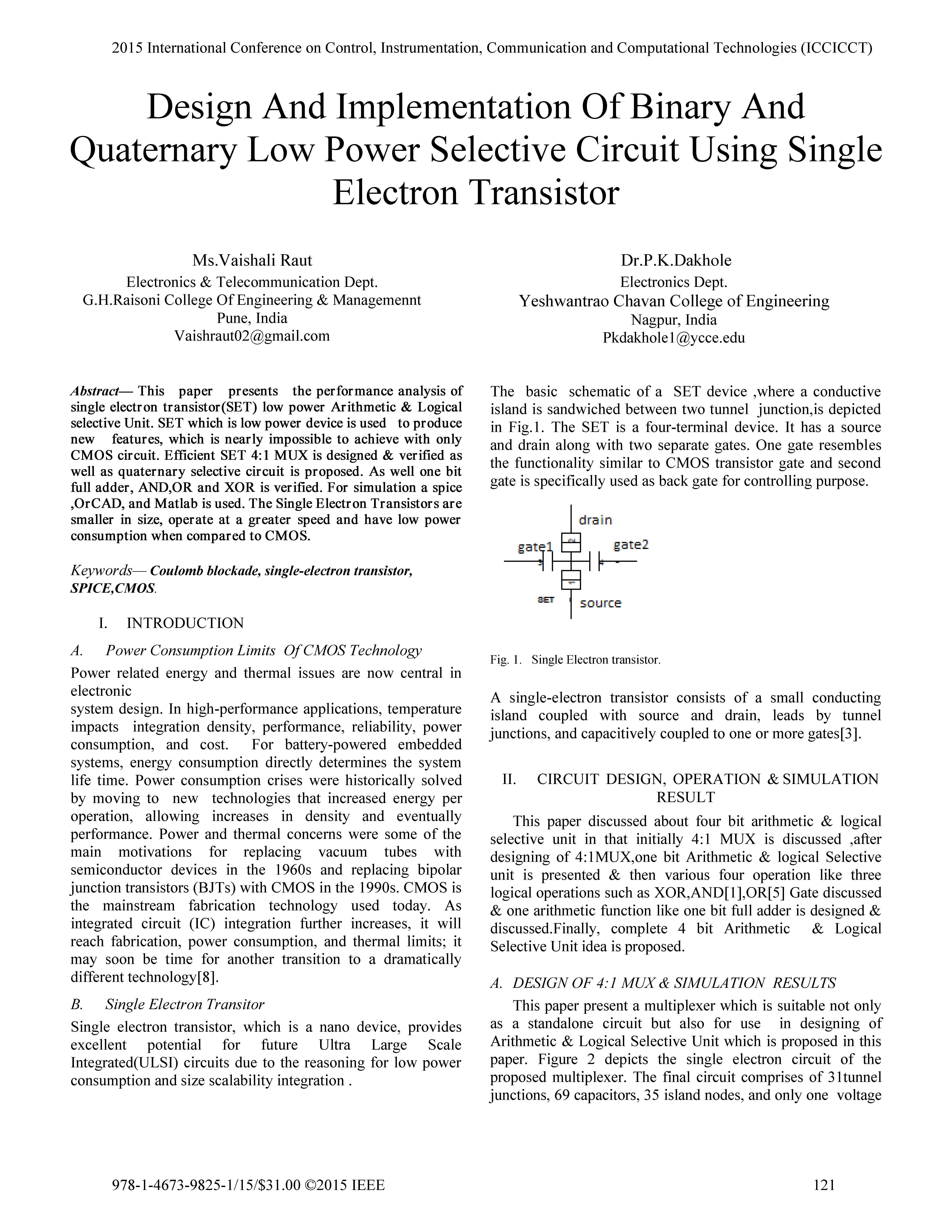

SET器件的基本原理图如图1所示,其中导电岛位于两个隧道结之间。SET是一种四端器件。It 具有源极和漏极,以及两个独立的栅极。其中一个栅极的功能类似于CMOS晶体管栅极,另一个栅极则专门用作背栅以实现控制功能。

单电子晶体管由一个小的导电岛组成,该导电岛通过隧道结与源极和漏极引线相连,并通过电容耦合与一个或多个栅极相连[3]。

II. 电路设计、操作与仿真结果

本文讨论了四位算术与逻辑选择单元,首先介绍了4:1 多路复用器,然后设计了4:1 MUX,接着提出了一位算术与逻辑选择单元,并讨论了多种四操作,包括三种逻辑操作:异或门、与门[I],或门[5] 门& 以及一个算术功能,即一位全加器的设计&和讨论。最后,提出了完整的4位算术& 逻辑选择单元的构想。

A. 设计 4:1 多路复用器 & 仿真结果

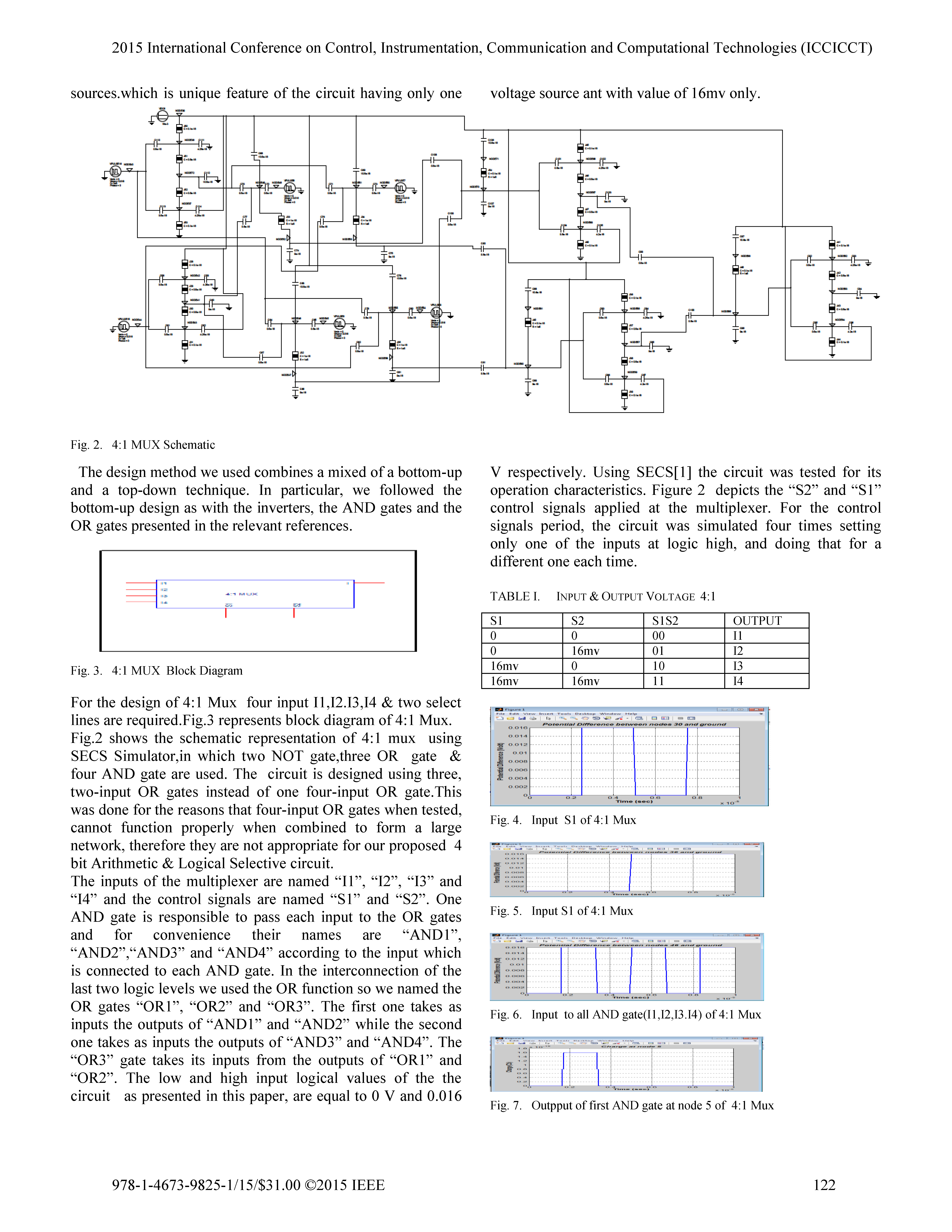

本文提出了一种多路复用器,它不仅适合作为独立电路,还可用于设计本文提出的算术& 逻辑选择单元。图2描绘了所提出的多路复用器的单电子电路。最终电路包含31个隧道结、69个电容器、35个岛节点以及仅一个电压源,这是该电路独有的特性,仅有一个电压源,其值仅为16毫伏。

我们采用的设计方法结合了自下而上和自上而下技术的混合方式。特别是,我们遵循了自下而上的设计方法,如相关参考文献中所述的反相器、与门和或门。

设计4:1多路复用器需要四个输入11、12、13、14和两条选择线。图3表示4:1多路复用器的框图。

图2显示了使用SECS仿真器实现的4:1多路复用器的原理图,其中使用了两个非门、三个或门和四个与门。该电路采用三个两输入或门来设计,而不是一个四输入或门。这样做的原因是,经过测试发现四输入或门在组合形成大型网络时无法正常工作,因此不适合用于我们提出的4位算术与逻辑选择电路。

多路复用器的输入命名为“11”、“12”、“13”和“14”,控制信号命名为“SI”和“S2”。每个输入通过一个与门传递到或门,为方便起见,这些与门根据所连接的输入分别命名为“ANDl”、“AND2”、“AND3”和“AND4”。在最后两级逻辑的互连中,我们使用了或函数,因此将或门命名为“ORl”、“OR2”和“OR3”。“ORl”接收“ ANDl”和“AND2”的输出作为输入,“OR2”接收“ AND3”和“AND4”的输出作为输入。“OR3”门的输入来自“ORl”和“OR2”的输出。本文中所述电路的低电平和高电平输入逻辑数值分别为0伏特和0.016伏特。

的输入)

的输入)

B. 一位算术 & 逻辑选择电路单元的设计

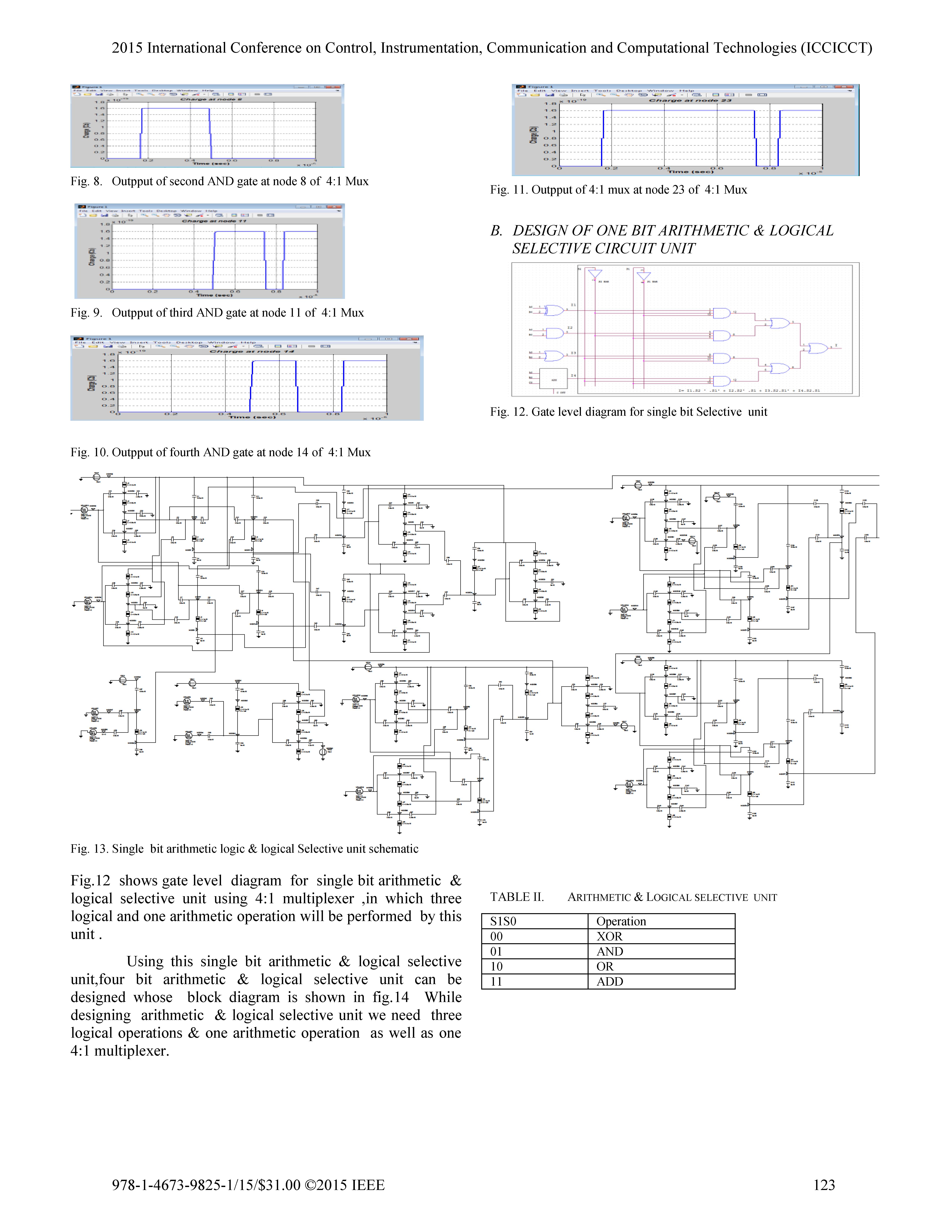

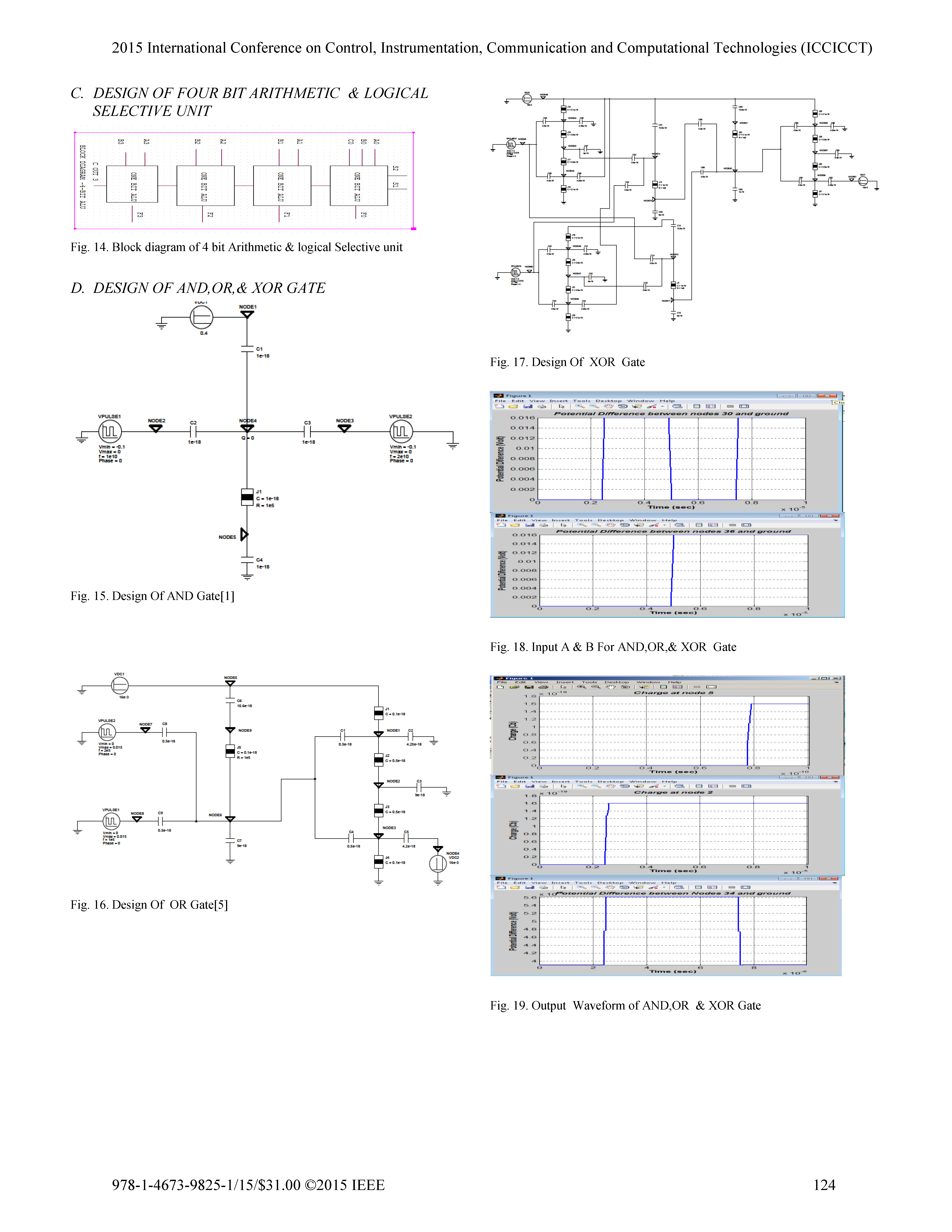

图12显示了使用4:1多路复用器的单比特算术与逻辑选择单元的门级电路图,该单元可执行三个逻辑和一个算术操作。

使用该单比特算术与逻辑选择单元,可以设计出四位算术与逻辑选择单元,其框图如图14所示。在设计算术 & 逻辑选择单元时,我们需要三种逻辑操作、一种算术操作以及一个4:1多路复用器。

| 操作 | S1 | S0 |

|---|---|---|

| XOR | 0 | 0 |

| AND | 0 | 1 |

| OR | 1 | 0 |

| ADD | 1 | 1 |

表 II. 算术 & 逻辑选择单元

C. 四位算术 & 逻辑选择单元的设计

D. 与、或、异或门设计

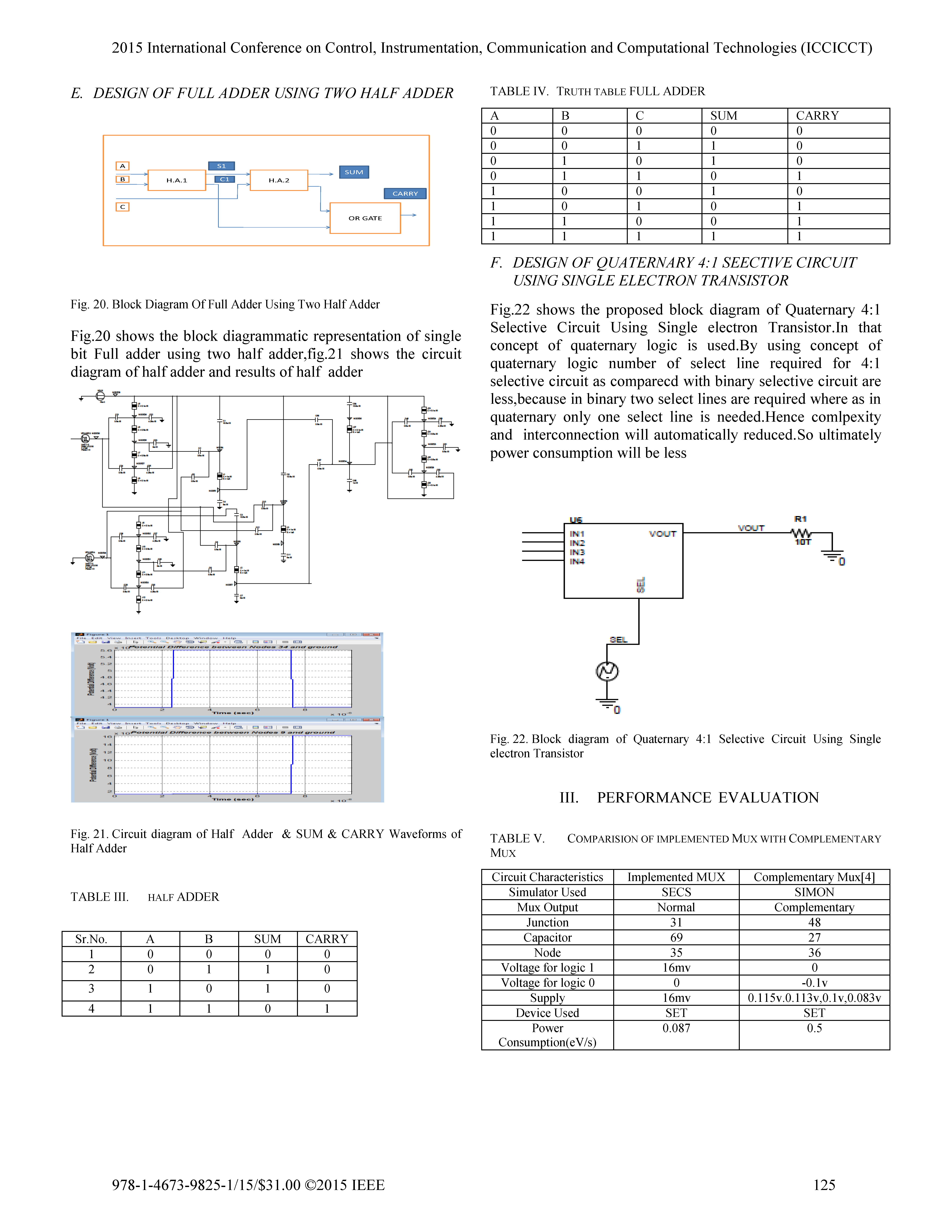

E. 使用两个半加器的全加器设计

图20展示了使用两个半加器构成的单比特全加器的框图表示,图21展示了半加器电路图和半加器结果。

| 序号 | A | B | SUM | 进位 |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 1 | 0 |

| 3 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 |

表 III. 半加器

| 序号 | A | B | C | SUM | 进位 |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 | 0 |

| 3 | 0 | 1 | 0 | 1 | 0 |

| 4 | 0 | 1 | 1 | 0 | 1 |

| 5 | 1 | 0 | 0 | 1 | 0 |

| 6 | 1 | 0 | 1 | 0 | 1 |

| 7 | 1 | 1 | 0 | 0 | 1 |

| 8 | 1 | 1 | 1 | 1 | 1 |

表 IV. 全加器真值表

F. 基于单电子晶体管的四进制4:1选择电路设计

图22展示了使用单电子晶体管的四进制4:1选择电路的 proposed 框图。该设计采用了四进制逻辑的概念。通过使用四进制逻辑,与二进制选择电路相比,4:1选择电路所需的选择线数量更少,因为在二进制中需要两条选择线,而在四进制中仅需一条选择线。因此,复杂性和互连数量将自动减少,最终功耗也会降低。

III. 性能评估

| 电路特性 | 已实现的多路复用器 | 互补多路复用器[4] |

|---|---|---|

| 使用的仿真器 | SECS | SIMON |

| 多路复用器输出 | 正常 | 互补 |

| 结点 | 35 | 48 |

| 电容器 | 69 | 27 |

| 逻辑1的电压 | 0.016 伏特 | 0.1 伏特 |

| 电源 | 16 mv | 0.115伏特、0.113伏特、0.1伏特、0.083伏特 |

| 使用的设备 | SET | SET |

| 功率消耗(e V/s) | 0.087 | 0.5 |

表 V. 实现的多路复用器与互补多路复用器比较

表V给出了4:1多路复用器的对比分析,其中所实现的 MUX所需的隧道结和节点数量更少。并且由于所实现的 MUX的功耗低于互补型MUX,因此如果将此MUX用于算术和逻辑选择电路,自然会需要更少的功率。

| 序号 | 频率 | 电源电压(直流伏) | 电路 | 功率(电子伏/秒) | 能量 |

|---|---|---|---|---|---|

| 1 | 1e5 | 0.016 | 与门 | 2.2e‐21 | 1.37e‐2 |

| 2 | 1e9 | 0.05 | 与门 | 2.5e‐19 | 1.56eO |

| 3 | 1e10 | 0.09 | 与门 | 2.5e‐19 | 1.56eO |

| 4 | 1e11 | 0.1 | 与门 | 2.5e‐19 | 1.56eO |

| 5 | 1e12 | 0.3 | 与门 | 2.1e‐19 | 1.31eO |

| 6 | 1e13 | 0.7 | 与门 | 2.5e‐19 | 1.56eO |

表 VI. 与门的频率、功率和电源电压分析参数

表VI给出了与门的参数分析,其中对与门在不同电源电压组合和频率下的表现进行了测试。图23显示了电源电压与频率之间的变化关系,表明二者之间存在线性关系;而图24显示了电源电压与功率之间的变化关系,随着电源电压的增加,电路的功耗并非呈线性变化,对于某些数值功耗上升,而对于某些数值则可能保持不变或下降,这种情况的发生是由于电容C4的值随频率以及电源电压的变化而变化所致。例如,在本例中,C4的数值分别为10.5e‐18、0.2e‐18、0.2e‐18、0.3e‐18、1e‐18、5.5e‐18,对应于表VI中所示的电源电压。

由此可以非常清楚地看出,如果我们对电容C4的数值进行一些调整,则可以控制功耗。利用这一概念,可以实现具有更低功耗的更大电路。

IV. 结论

本文提出了一种基于单电子晶体管的低功耗算术与逻辑选择单元的设计。本文提出了一种高效的4:1多路复用器,利用该多路复用器设计了单比特低功耗算术与逻辑选择单元;该高效的4:1多路复用器电路包含31个隧道结、69个电容器和35个岛屿,其功耗仅为0.087电子伏特/秒,电源电压仅为16毫伏,这是该设计的独特特点。因此,这种Four 比特算术与逻辑选择单元将具有低功耗的优势,该思路被提出。

5043

5043

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?