看上面这个图,对应起来一个个看每个字母、标签代表的是什么意思。二维码和条形编码扫出来是一串数字,二维码是厂家用来防伪的,只有一个对应的编码,条形码是厂家内部的物料编码。标号1是三星的Logo,标号2是生产地,标号3是物料编码,标号6是内存条的生成日期,标号7看下面的图片。

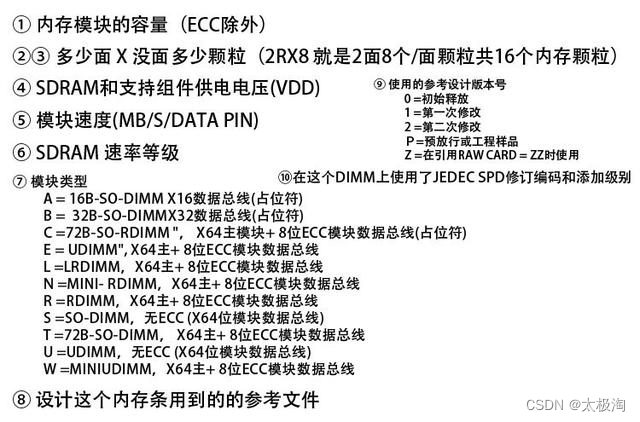

标号4根据JEDEC标准对照。“8GB 1Rx8 PC4-2400T-SA1-11”表示的就是这是8G的内存条,1面有8个颗粒这整个内存条共有8个颗粒,DDR4 速率标准2400(频率1200MHz)

标号4根据JEDEC标准对照。“8GB 1Rx8 PC4-2400T-SA1-11”表示的就是这是8G的内存条,1面有8个颗粒这整个内存条共有8个颗粒,DDR4 速率标准2400(频率1200MHz)

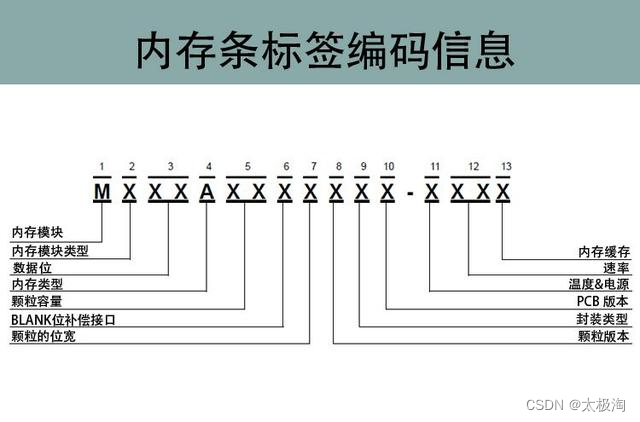

标号五与内存颗粒上面编码类似,每数位上表示的意思各不相同,第一个小标是固定的M就是内存。第四个小标也是不变的表示DDR4。

标号五与内存颗粒上面编码类似,每数位上表示的意思各不相同,第一个小标是固定的M就是内存。第四个小标也是不变的表示DDR4。

SODIMM相对DIMM外形上更小,大致是正常DIMM尺寸的一半,“x64”最多能支持的队列数、“260pin”针脚数260。

SODIMM相对DIMM外形上更小,大致是正常DIMM尺寸的一半,“x64”最多能支持的队列数、“260pin”针脚数260。

第五个小标表示每个颗粒的真实容量要与颗粒上面的编码容量区分开来。

第五个小标表示每个颗粒的真实容量要与颗粒上面的编码容量区分开来。

第9个小标是封装方式和第10个小标PCB的版本就不多说了。

第9个小标是封装方式和第10个小标PCB的版本就不多说了。

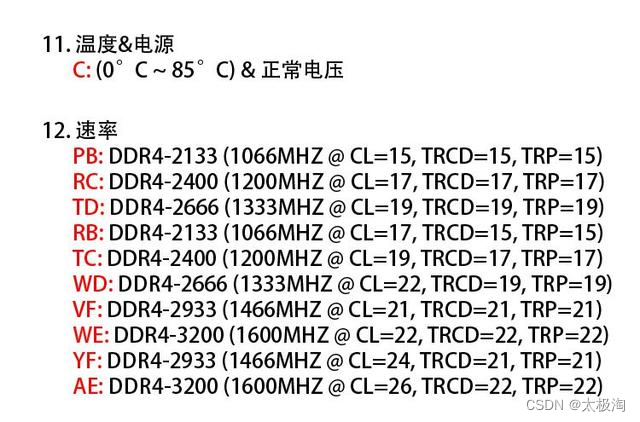

速率包括频率、CL内存读写操作前列地址控制器的潜伏时间(稳定操作系统)、tRCD行寻址至列寻址延迟时间(数值越小越好)、tRP内存行地址控制器预充电时间(数值越小读写速度就越快)。

速率包括频率、CL内存读写操作前列地址控制器的潜伏时间(稳定操作系统)、tRCD行寻址至列寻址延迟时间(数值越小越好)、tRP内存行地址控制器预充电时间(数值越小读写速度就越快)。

本文介绍了内存条上的各种标识,如二维码和条形码的作用,以及内存条的规格参数,如DDR4的频率、内存容量和颗粒数量。还提到了SODIMM的尺寸和针脚数,以及内存的性能指标,如CL、tRCD和tRP等。

本文介绍了内存条上的各种标识,如二维码和条形码的作用,以及内存条的规格参数,如DDR4的频率、内存容量和颗粒数量。还提到了SODIMM的尺寸和针脚数,以及内存的性能指标,如CL、tRCD和tRP等。

129

129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?