自制1000+晶体管阵列芯片

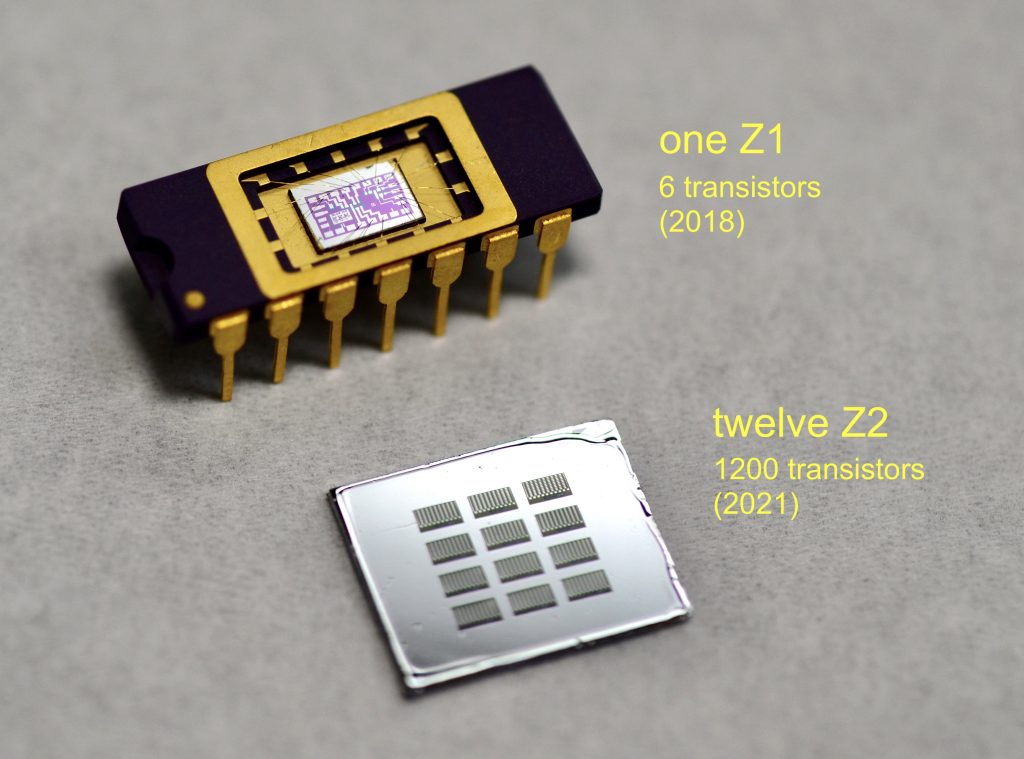

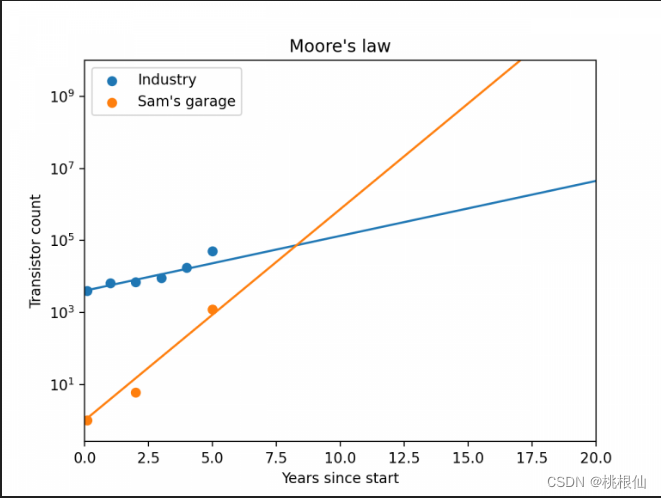

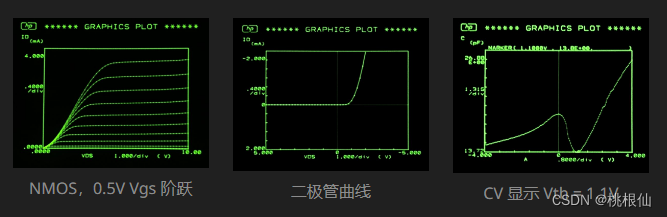

2018 年,我 在我的车库工厂制造了第一个光刻制造的集成电路。当我制作 Z1 放大器时,我是一名高中生,现在我是一名大四学生,所以业余硅工艺有一些早就应该改进的地方。 Z1 有 6 个晶体管,是开发所有工艺和设备的绝佳测试芯片 。Z2 在 10µm多晶硅栅极 工艺上具有 100 个晶体管——与英特尔的第一款处理器英特尔的第一款处理器 相同的技术。我的芯片是一个简单的 10×10 晶体管阵列,用于测试、表征和调整过程,但这是向更先进的 DIY 计算机芯片迈出的一大步。Intel 4004 有 2,200 个晶体管,而我现在已经在同一块硅片上制造了 1,200 个。

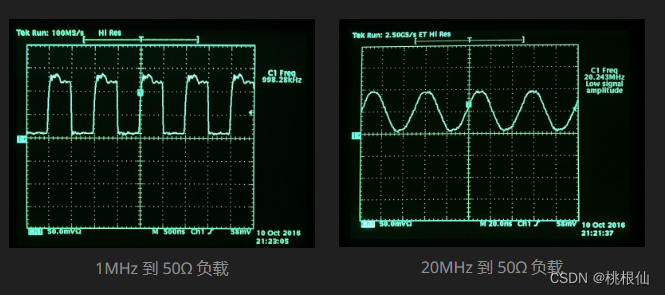

以前,我用金属栅工艺制造芯片。铝栅极与其下方的硅通道具有较大的功函数差异,从而导致高阈值电压(> 10V)。我在一些有趣的项目中使用了这些金属栅极晶体管,例如吉他失真踏板和

,环形振荡器 LED 闪光灯但由于高 Vth,这两个都需要一到两节 9V 电池来运行电路。通过切换到多晶硅栅极工艺,我获得了大量性能优势(自对准栅极意味着更低的重叠电容),包括更低的 Vth,这使得这些芯片与 2.5V 和 3.3V 逻辑电平兼容。新型 FET 具有出色的特性:

NMOS 电气特性:

Vth = 1.1 V

Vgs 最大值 = 8 V

Cgs = <0.9 pF

上升/下降时间 = <10 ns

开/关比 = 4.3e6

漏电流 = 932 pA (Vds=2.5V)

超低的漏电流让我特别惊讶。这个值在环境室内照明中上升了大约 100 倍。

NMOS,0.5V Vgs 阶跃

二极管曲线

CV 显示 Vth = 1.1V

现在我们知道,用不纯的化学物质、没有洁净室和自制设备可以制造出真正好的晶体管。当然,产量和工艺可重复性会降低。我将进行更多测试以收集有关 FET 属性的统计数据和可变性的数据,但它看起来不错!

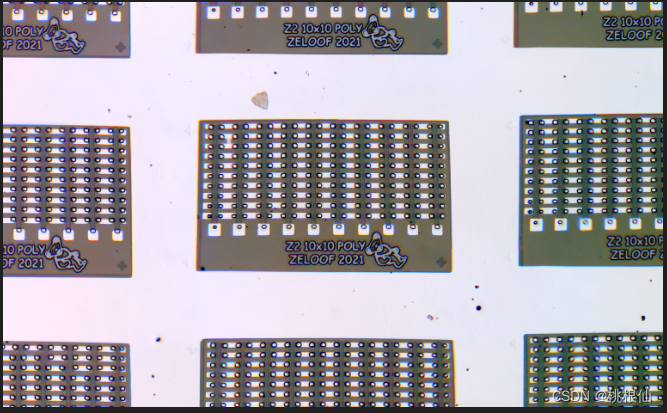

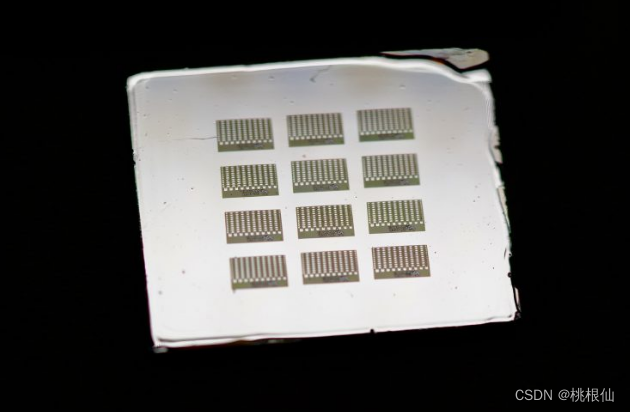

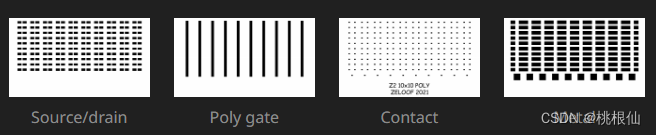

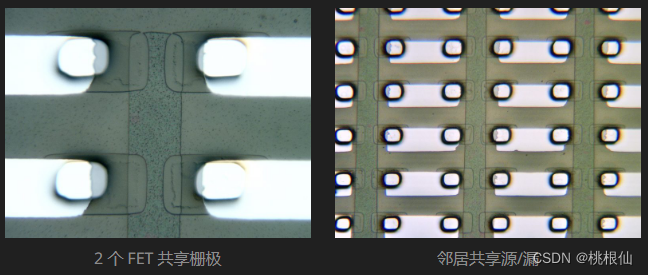

该芯片很小,大约是我之前 IC 芯片面积的四分之一(2.4mm^2),这使得它很难探测。每个芯片上都有一个简单的 10×10 N 通道 FET 阵列,这将为我提供大量特性数据。因为它是一个如此简单的设计,所以我可以使用 Photoshop 进行布局。10 个晶体管的列共享一个公共栅极连接,每行串联在一起,相邻的晶体管共享一个源极/漏极端子。它类似于 NAND 闪存,但我这样做只是为了保持金属焊盘足够大,以便我可以合理地探测它们,如果每个 FET 本身有 3 个焊盘,它们就会太小。

在将一块岩石浸入化学物质中一整天后,看到曲线追踪器上显示出良好的 FET 曲线,这种兴奋难以表达。

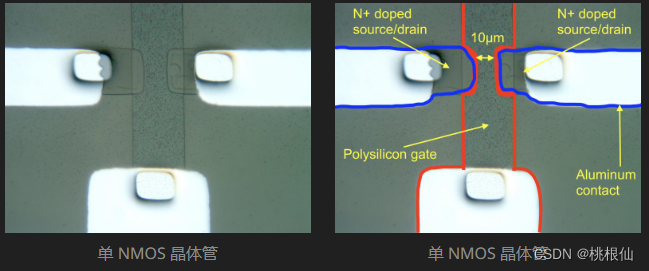

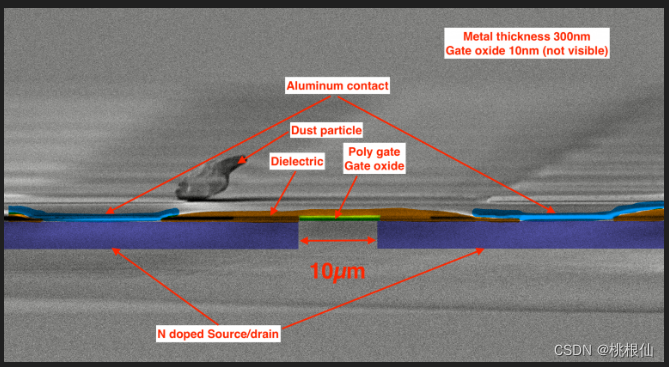

下面可以看到单个 10µm NMOS 晶体管,金属层有轻微的错位(左侧触点的一部分未被覆盖)。红色轮廓是多晶硅,蓝色是源极/漏极。

到目前为止,我已经制作了一个运算放大器(Z1)和一个类似内存的数组(Z2)。即使晶体管密度如此之低,也绝对有可能实现更有趣的电路。这个过程需要一些调整,但现在我能够始终如一地制造高质量的晶体管,我应该能够设计更复杂的数字和模拟电路。测试每个芯片非常繁琐,所以我试图自动化这个过程,然后我会发布更多数据。我已经制作了 15 个芯片(1,500 个晶体管),并且知道至少有一个功能齐全的芯片和至少两个“大部分功能”,这意味着大约 80% 的晶体管工作而不是 100%。还没有合适的产量数据。最常见的缺陷是漏极或源极与体硅通道短路,而不是像我的 Z1 工艺那样的泄漏或短路栅极。

我之前说过,栅极过去是用铝制成的,现在是硅,这使得芯片工作得更好。硅有我们关心的三种类型:非晶、多晶和单晶。从左到右,这些变得更具导电性,但也更难沉积。事实上,单晶硅是无法沉积的,你只能在与另一个单晶硅层接触的情况下生长它作为种子(外延)。由于栅极必须沉积在绝缘电介质的顶部,因此我们可以做到最好。无论如何,我们都可以对多晶硅进行大量掺杂以使其更具导电性。

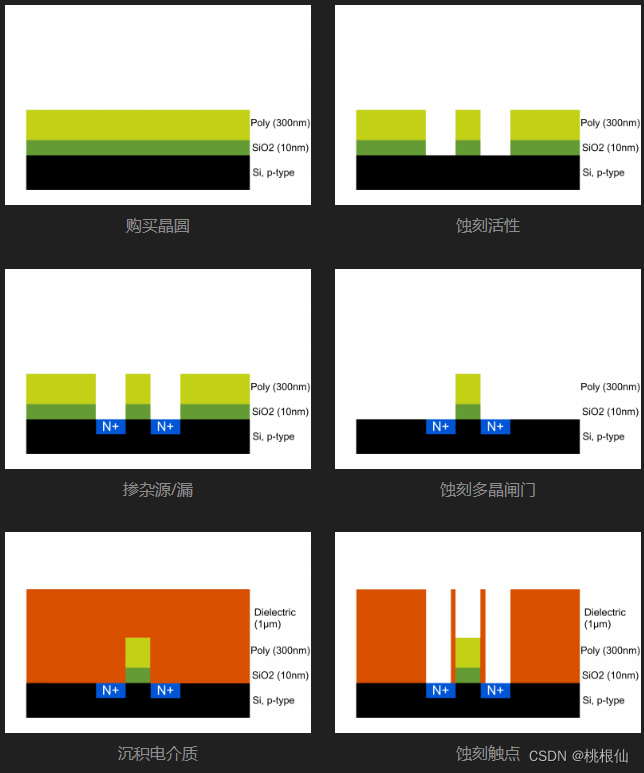

典型的自对准多晶硅栅极工艺需要硅烷(一种有毒且易爆的气体)来沉积多晶硅层。也可以通过溅射或蒸发非晶硅并用激光退火这种 DIY 硅工艺的一个主要主题是规避昂贵、困难或危险的步骤。所以,我想出了一个修改后的流程。这是标准自对准方法的一种变体,允许通过高温扩散而不是离子注入进行掺杂。效果是我可以从工厂购买已经沉积多晶硅的硅晶片,并将其图案化以制造晶体管,而不是在过程中途放置我自己的多晶硅。这是一个不错的短期解决方法,但最好使用上述激光退火方法设计多晶硅沉积工艺。

晶圆上已经沉积了各种材料,所以我只需要找到一个有一层薄薄的 SiO2(栅极氧化物,~10nm),然后是更厚的多晶硅(300nm)。我在 eBay 上以 45 美元的价格找到了很多 25 200 毫米(EPI、prime、[1-0-0]、p 型)晶圆,这基本上是终身供应,所以如果你想要一个,请给我发电子邮件。栅氧化层是最脆弱的层,在制造过程中需要格外小心。因为我买的晶圆上已经有很好的高质量氧化物,它被厚厚的多晶硅层盖住并保持清洁,我能够从工艺中消除所有腐蚀性的清洁化学品(硫酸等),并且仍然做得很好晶体管。下面列出了最低限度的工艺化学品和工具。

家用聚浇口工艺中使用的化学品:

-水

-酒精

-丙酮

-磷酸

-光刻胶

-显影剂(2% KOH)

-N型掺杂剂(filmtronics P509)

-HF (1%) 或 CF4/CHF3 RIE

-HNO3 用于多蚀刻或 SF6 RIE

家用聚浇口工艺使用的设备:

-电炉

-管式

-光刻设备-显微镜

-用于沉积金属的真空室

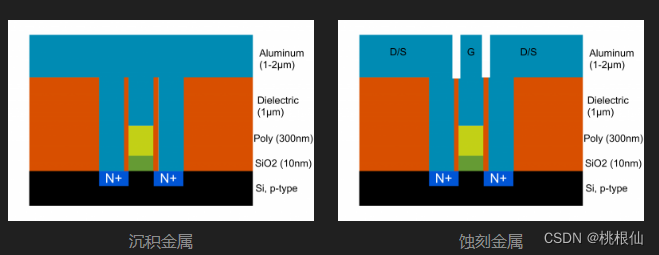

Z2“先栅极”工艺(类似于标准自对准工艺,但没有场氧化物):

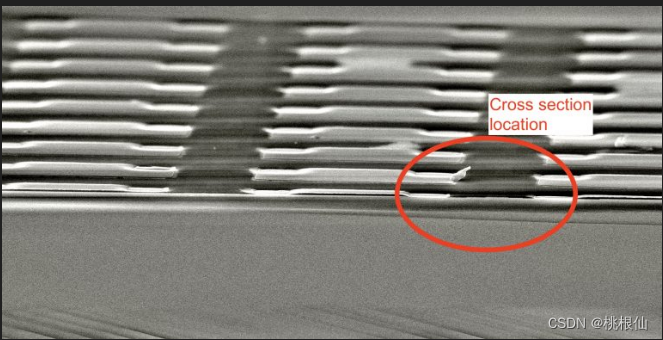

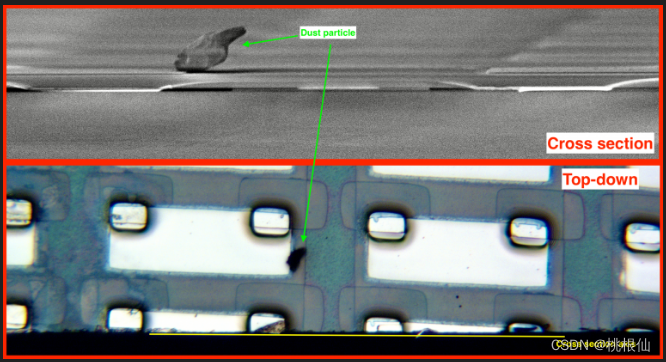

我将其中一个测试芯片折成两半(功能性 Z2,但层对齐不良且金属薄,约 300nm)并将其放入我的SEM中进行横截面:

…折断

在下面的红色圆圈中找到灰尘颗粒,使用它在接下来的横截面视图中确定方向。

NMOS 截面

因为我已经购买了上面有栅极氧化物和多晶硅的晶圆,所以我无法生长场氧化物。这些厚氧化层通常用于掩蔽掺杂剂,并且需要长时间的高温步骤,这会氧化我的所有多晶硅并且不会留下任何残留物。因此,我修改后的工艺使用了一个额外的掩膜步骤(“栅极”掩膜通常不会在自对准工艺中找到),这使我可以将多晶硅本身用作掺杂剂掩膜,并将硬烤光刻胶用作场电介质。这种替代处理产生了阶梯结构,您可以在上面 NMOS 横截面的橙色区域中看到。这里提到了这个过程的微妙之处。

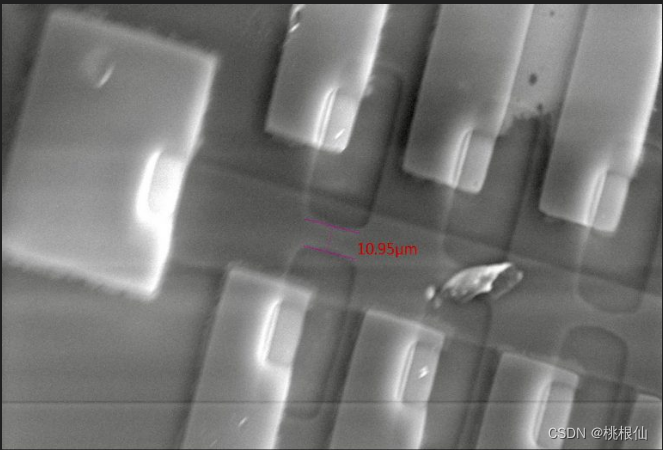

浇口长度测量

这个过程并不理想,我想进行一些更改,使其与 CMOS 兼容,但它简化了制造,并使用最少的工具集使其成为可能。理想情况下,1µm 介电层(橙色)是 CVD SiO2(可以在家中构建 TEOS 氧化物反应器),但我使用了光刻胶。大多数光刻胶可以在 250°C 左右烘烤以形成硬质永久介电层,这是 CVD 或 PECVD 氧化物的简单替代品。这里也可以使用旋涂玻璃/溶胶凝胶。SiO2 蚀刻是使用

由除锈剂或 RIE 制成的缓冲 HF 溶液进行的。

巨大的复合缝合模具图像:

一位大学生在他的车库实验室成功制造了拥有1,200个晶体管的集成电路,采用10微米多晶硅栅极工艺,与早期英特尔处理器相同技术。这一成就包括更低的阈值电压、超低漏电流和快速开关时间,标志着自制硅工艺的巨大提升。芯片设计包括一个10x10晶体管阵列,用于测试和表征,目标是迈向更复杂的DIY计算机芯片。尽管产量和工艺重复性仍有待提高,但这一创新表明在家庭条件下也能制造出高性能的晶体管。

一位大学生在他的车库实验室成功制造了拥有1,200个晶体管的集成电路,采用10微米多晶硅栅极工艺,与早期英特尔处理器相同技术。这一成就包括更低的阈值电压、超低漏电流和快速开关时间,标志着自制硅工艺的巨大提升。芯片设计包括一个10x10晶体管阵列,用于测试和表征,目标是迈向更复杂的DIY计算机芯片。尽管产量和工艺重复性仍有待提高,但这一创新表明在家庭条件下也能制造出高性能的晶体管。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?