FENCE.I指令及CAS指令集

一、FENCE.I指令

1、FENCE.I指令简介

FENCE.I 是 RISC-V 指令集架构中的一种 Fence 指令,用于同步指令缓存(Instruction Cache),用于保证内存操作的正确性和顺序性。具体来说,FENCE.I指令可以确保之前发出的所有对内存的读写操作都已经完成,并且将数据从处理器缓存中刷新到内存中,然后再继续执行后面的指令,这样确保处理器按照预期顺序执行指令。

FENCE.I 指令的格式如下:

fence.i

需要注意的是,FENCE.I 指令并不需要任何参数或者操作数,它只是一个空指令,用于指示处理器在此位置停顿一段时间,等待之前的内存操作完成。

在实际应用中,FENCE.I 指令通常会与其他指令一起使用,并由编译器插入到程序中。例如,在多核处理器或者共享内存系统中,为了避免数据竞争和内存一致性问题,程序员需要使用 FENCE.I指令来同步各个处理器之间的内存操作。具体来说,当一个处理器进行了对共享内存的写操作后,需要使用 FENCE.I

指令来确保该操作已经完成,并且其他处理器能够看到这个写操作的结果。类似地,当一个处理器进行了对共享内存的读操作后,也需要使用 FENCE.I指令来确保之前的写操作已经完成,并且可以读取到最新的数据。

需要注意的是,FENCE.I 指令只能同步内存操作,不能同步 I/O 操作。如果需要同步 I/O操作,需要使用 FENCE.IO 指令。同时,在使用 FENCE.I 指令时还需要注意指令的正确性和安全性,避免出现意外情况或者破坏程序稳定性。

在 RISC-V 中,FENCE.I指令是一种用于同步内存操作的指令,可以保证内存操作的正确性和顺序性。在多核处理器或者共享内存系统中,程序员需要使用 FENCE.I

指令来确保各个处理器之间的内存操作同步。

2、FENCE.I指令举例

下面通过一个例子来说明 FENCE.I

指令的作用。假设有两个处理器 P1 和 P2,它们共享一块内存区域 mem,P1 往该内存区域中写入了一个数据 x,而 P2需要读取这个数据并进行相应的处理。

在这种情况下,为了保证内存操作的正确性和顺序性,需要在P1 写入数据 x 后插入一个 FENCE.I 指令,以确保写操作已经完成,并将数据从处理器缓存刷新到内存中。然后在 P2 读取数据之前也需要插入一个

FENCE.I 指令,以确保之前的写操作已经完成,并且可以读取到最新的数据。

具体的代码实现如下:

// P1

mem[0] = x; // 写入数据 x

fence.i; // 插入 FENCE.I 指令

// P2

fence.i; // 插入 FENCE.I 指令

y = mem[0]; //

读取数据并进行相应的处理P1 将数据 x 写入内存区域 memory中,并插入一个 FENCE.I 指令;P2 读取数据并进行相应的处理之前也插入了一个 FENCE.I 指令。这样就可以确保 P2 能够读取到 P1写入的最新数据,并且避免了数据竞争和内存一致性问题的出现。

需要注意的是,实际应用中 FENCE.I指令的使用可能会更加复杂,具体要根据具体的场景和应用来确定。同时,在使用 FENCE.I

指令时还需要注意指令的正确性和安全性,避免出现意外情况或者破坏程序稳定性

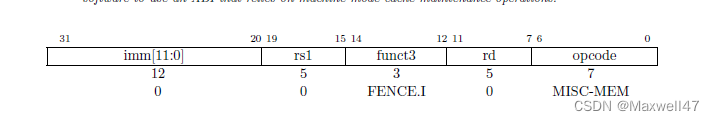

3、FENCE.I指令格式

FENCE.I 指令的编码为固定值,其中每一位的含义如下:

Bits [31:27]:固定为 0。

Bit [26]:固定为 1。

Bits [25:20]:固定为 0。

Bits [19:15]:固定为 1。

Bits [14:12]:固定为 0。

Bits [11:7]:固定为 0。

Bits [6:2]:固定为 0。

Bit [1]:固定为 0。

Bit [0]:固定为 0。

可以看出,FENCE.I指令的编码格式非常简单,其中,Bit[26] 置为 1 表示该指令是一条 Fence 指令,并且 Bits[19:15] 的值为 1表示该指令是用于同步指令缓存(ICache)的。

二、FENCE指令

2.1 指令字段解析

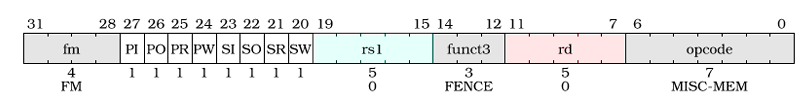

这张图是 RISC-V 架构中 FENCE 指令的 32 位指令编码格式(Instruction Encoding Format)。

FENCE 指令属于 RISC-V 的 MISC-MEM 指令集,它使用了 I-Type 指令格式的一种变体。您的这张图非常清晰地展示了标准 I-Type 格式中的 12 位立即数(imm[11:0])是如何被 FENCE 指令“重新利用”来编码其复杂参数的。

以下是对图中每个字段的详细分析,从右到左:

2.1.1. 基础识别字段 (Opcode, funct3)

opcode(bits 6:0): 值为0b0001111(MISC-MEM)。- 这是一个主操作码,它告诉 CPU 这是一条“内存杂项”指令。这个操作码由

FENCE,FENCE.I和CSR(控制状态寄存器)指令共享。

- 这是一个主操作码,它告诉 CPU 这是一条“内存杂项”指令。这个操作码由

funct3(bits 14:12): 值为0b000(FENCE)。- 这个 3 位的字段用于区分

MISC-MEM中的不同指令。 0b000代表FENCE。0b001代表FENCE.I(指令栅栏)。- 其他值用于

CSR指令。

- 这个 3 位的字段用于区分

2.2.2. 寄存器字段 (rd, rs1)

rd(bits 11:7): 目标寄存器。- 对于

FENCE指令,这个字段必须为 0(即x0寄存器)。FENCE指令不产生任何结果,也不需要写回寄存器。

- 对于

rs1(bits 19:15): 源寄存器 1。- 对于

FENCE指令,这个字段也必须为 0(即x0寄存器)。

- 对于

小结: 截至 bit 19,opcode=0b0001111, funct3=0b000, rd=0, rs1=0 这几个字段组合在一起,唯一地将这条指令标识为 FENCE。

2.2.3. FENCE 核心参数字段 (bits 31:20)

这 12 个 bit 在标准的 I-Type 格式中是 imm[11:0] 立即数字段。但在 FENCE 指令中,它们被赋予了特殊的含义,用于编码前驱(Predecessor)和后继(Successor)集合。

这完美地对应了我们之前讨论的 FENCE pred, succ 语法。

Successor Set (后继集合, bits 23:20)

这 4 个 bit 定义了 FENCE 指令之后的哪些操作需要被排序。

SW(bit 20): Successor Write (后继“内存写”)。SR(bit 21): Successor Read (后继“内存读”)。SO(bit 22): Successor Output (后继“I/O 写”)。SI(bit 23): Successor Input (后继“I/O 读”)。

Predecessor Set (前驱集合, bits 27:24)

这 4 个 bit 定义了 FENCE 指令之前的哪些操作需要被排序。

PW(bit 24): Predecessor Write (前驱“内存写”)。</

RISC-V中FENCE与CAS指令详解

RISC-V中FENCE与CAS指令详解

本文介绍了RISC-V指令集中的FENCE.I指令,用于同步指令缓存,确保内存操作的正确性和顺序性。在多核处理器或共享内存系统中,FENCE.I指令能防止数据竞争和内存一致性问题。文章通过实例解释了如何在编程中正确使用FENCE.I指令,并给出了指令的具体编码格式。

本文介绍了RISC-V指令集中的FENCE.I指令,用于同步指令缓存,确保内存操作的正确性和顺序性。在多核处理器或共享内存系统中,FENCE.I指令能防止数据竞争和内存一致性问题。文章通过实例解释了如何在编程中正确使用FENCE.I指令,并给出了指令的具体编码格式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1973

1973

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?