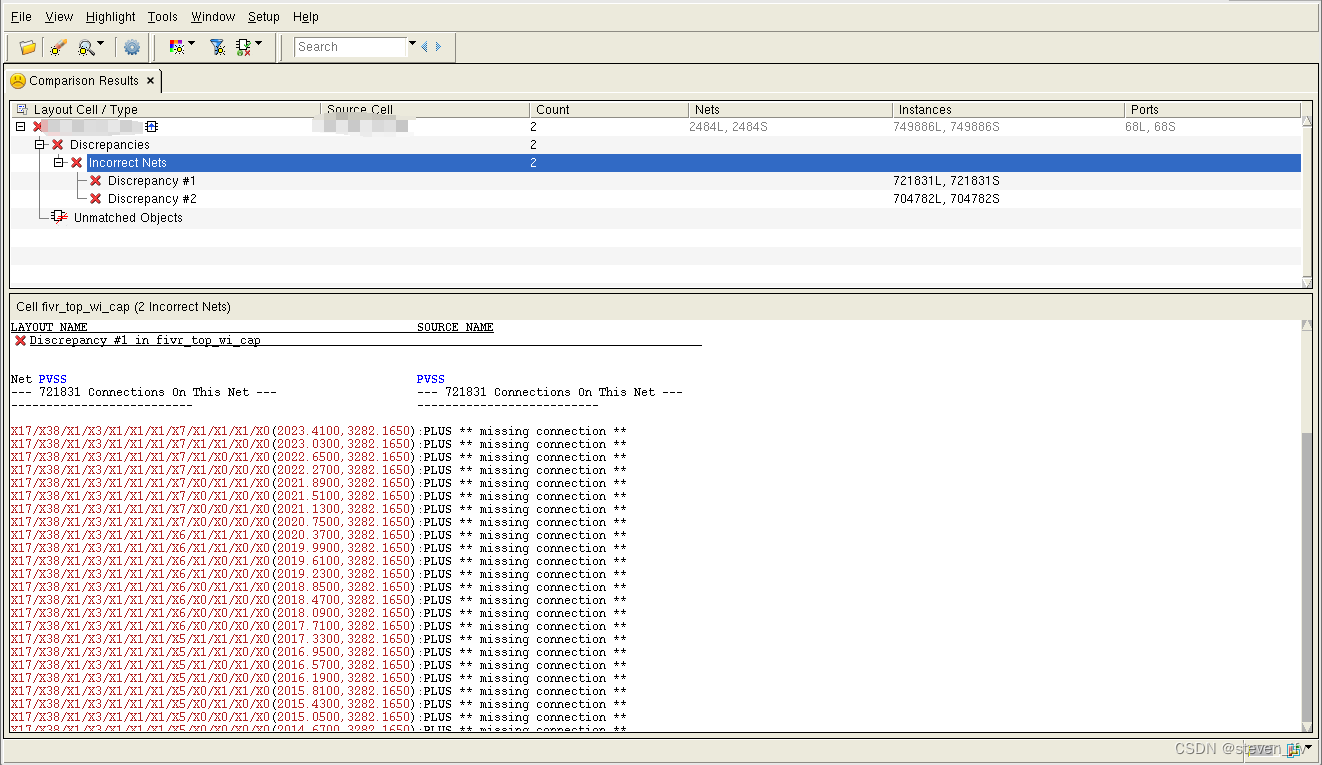

顶层加decap电容肉眼查没问题 但是报missing connection 找不到decap的vdd vss链接

解决方法是 net tracer算了一晚上发现顶层vddvss短路了 再去查电容链接

发现有组decap电容接反了 可能是moscap要区分正负 改掉后lvs通过

虽然lvs没报短路 但实际是大短路问题

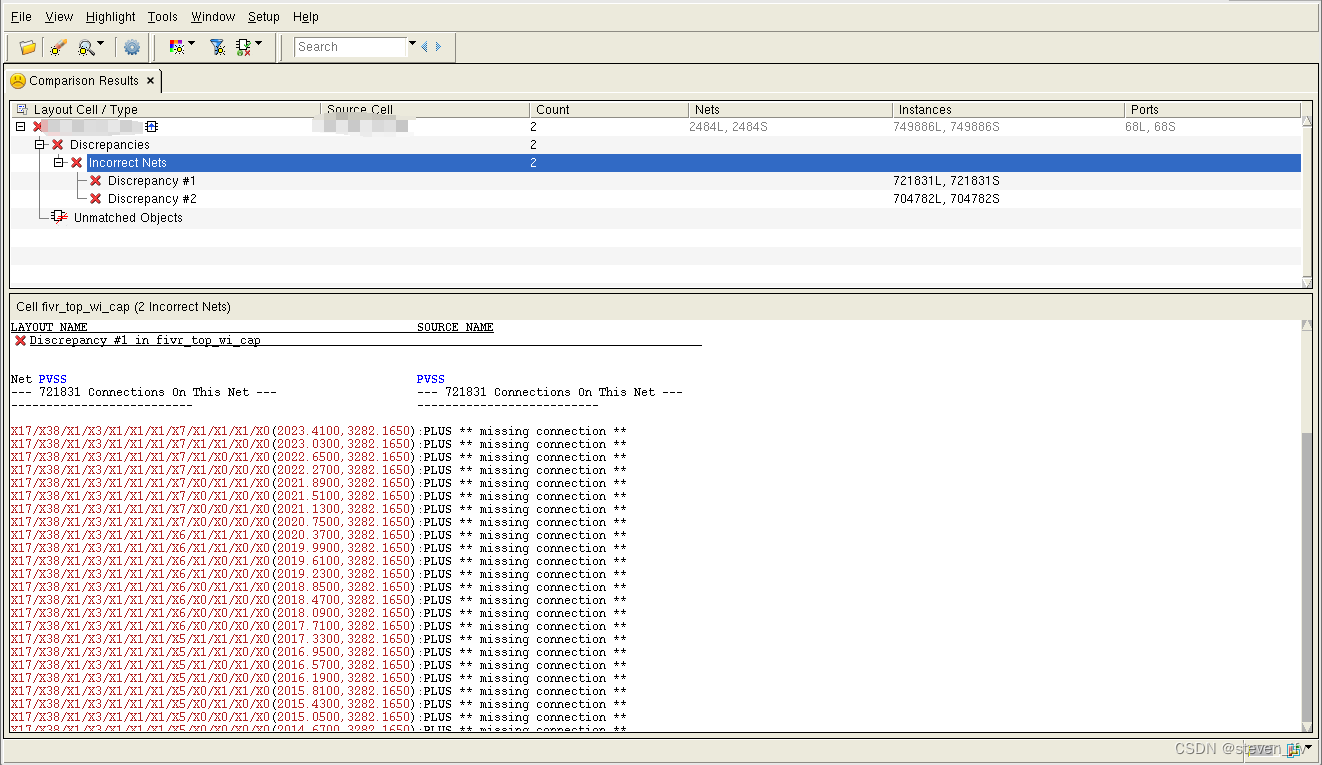

顶层加decap电容肉眼查没问题 但是报missing connection 找不到decap的vdd vss链接

解决方法是 net tracer算了一晚上发现顶层vddvss短路了 再去查电容链接

发现有组decap电容接反了 可能是moscap要区分正负 改掉后lvs通过

虽然lvs没报短路 但实际是大短路问题

2万+

2万+

3278

3278

2835

2835

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?