基于双栅三有源层沟道的 AMOLED像素电路用IGZO薄膜晶体管的设计与分析

1. 引言

透明非晶导电氧化物薄膜已被考虑用于多种应用领域,例如平板显示器背板中的开关元件。在透明导电氧化物(TCOs)中,作为薄膜晶体管(TFT)的有源沟道层,非晶铟镓锌氧化物(a‐IGZO)相比传统的非晶氧化物材料已变得更加流行。TFT器件的行为主要取决于沟道层,特别是在界面层1 nm至2 nm范围内的特性,而与所用衬底无关[1, 2],电子迁移率、电子浓度、态密度和界面电荷直接影响器件的场效应迁移率、ION/IOFF比、亚阈值摆幅和开启电压。a‐IGZO具有更宽的能带隙,可在可见光谱范围内提供良好的透过率,特殊的化学键合引发高场迁移率,并表现出改善的电学特性,如高的ION/IOFF比、增强的寿命、更好的透过率以及最佳的大面积均匀集成 [3, 4]。然而,有源层中铟(In)和镓(Ga)的含量决定了a‐IGZO基薄膜晶体管的电学性能。增加In含量可提高迁移率,但会导致关态电流不期望地增加,从而恶化亚阈值摆幅;相反,增加Ga含量会降低关态电流,改善亚阈值摆幅,但会削弱迁移率参数[5]。单有源层存在固有的局限性,因此其薄膜密度较低,为此已提出多层堆叠沟道结构的TFT以克服这些限制。金等人[6]首次引入的双层/双有源层结构旨在解决所有这些问题。从根本上讲,在双层/双有源层TFT中,高迁移率半导体与非晶氧化物半导体(AOS)的低载流子浓度相结合。这种方法有助于实现比单有源层沟道结构更高的迁移率和稳定性,因为前沟道和后沟道均具有较高的电荷陷阱密度和载流子浓度[7, 8]。

随后出现了其他几种双有源层组合,例如ITO/IGZO、IZO/IGZO、 IZO/ZTO和IZO/AIZTO等。然而,ITO/IGZO组合受到更多关注,原因在于其界面陷阱密度极小(dit),两层均具有更平滑的表面,且ITO与a‐IGZO之间形成同质结[9]。此外,基于固态能级标度,氧阴离子衍生的价带使得ITO和a‐IGZO薄膜几乎具有相等的电离势和相同的带隙[10]。对于厚度为 30 nm的低载流子浓度层,研究了典型厚度在3 nm至6 nm之间的高迁移率层以获得最佳结果[7, 11, 12]。在以往的研究中,采用双层有源沟道的单栅 a‐IGZO基TFT已报道实现了改善的电学特性[8, 9, 13]。但双栅(DG)结构中的a‐IGZO TFT由于可通过顶栅(TG)施加偏置来调控阈值电压,在电路设计中更具前景。在DG TFT中,主栅极和次栅极分别为底栅(BG)和顶栅(TG),它们分别从负电压到正电压逐渐增加BG终端的偏置。过去已有报道称,在器件中使用两个栅极可以加强对沟道和漏极的静电控制field do not affect or disrupt the channel. 此外,由于第二个栅极的存在,双栅结构降低了关态电流,从而提高了整体电流比 ION/IOFF,并改善了电学特性[14]。顶接触底栅结构通常在栅极与源漏导体之间设计有重叠,这会导致回踢电位、高噪声以及TFT显示阵列的延迟响应[15],,原因是器件中存在重叠电容[16, 17, 18]。

然而,可以通过在有源矩阵显示器中引入偏移来消除重叠电容,从而实现可忽略的回踢电压[19, 20,21],,但代价是漏极电流下降。

本文中,作者提出了一种新型双栅三有源层沟道(DG‐TAL)薄膜晶体管,并分析了其在不同栅极与源漏接触之间的重叠和偏移长度下的输出特性和转移特性fferent overlap and offset length between gate and S‐D contacts. 器件的电学参数已被报道,并探讨了其在AMOLED像素电路中的应用。本工作的组织如下:第2节描述了器件的设计规格和模拟参数;第3节讨论了所设计器件的结果并展示了电路应用;最后,第4节总结了本工作并提出了未来的研究方向。

2. 设计

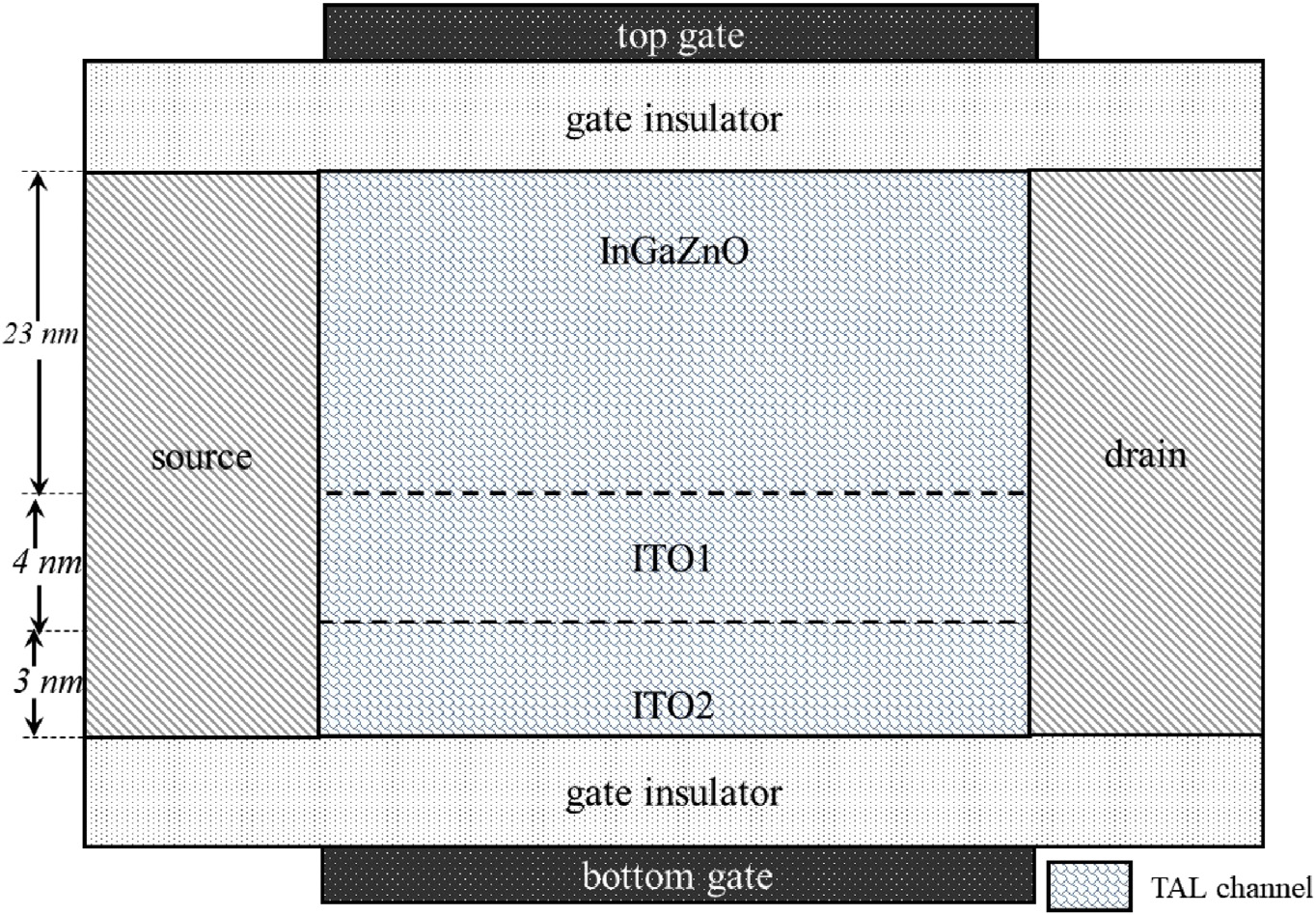

所提出的顶接触、底部栅极薄膜晶体管结构的示意图如图1所示。厚度为 130 nm的底栅绝缘层SiO2已沉积

位于重掺杂p型硅衬底上方。沉积了一层30纳米厚的有源层,由非晶铟镓锌氧化物(a‐IGZO)和锡掺杂氧化铟(ITO)组成,作为薄膜晶体管(TFT)的沟道,沟道长度保持为25毫米。该30纳米厚的有源沟道层由23纳米 a‐IGZO、4纳米ITO层‐1(ITO1)和3纳米ITO层‐2(ITO2)构成。其中,ITO2子层主要通过较低载流子浓度(3.63 × 10¹⁴ cm⁻³)与ITO1区分开来。层厚度和掺杂浓度提供了对器件特性的更好控制。有源沟道的第三子层由于具有较低的浓度,可提供更高的电荷陷阱密度,并提高沟道结构的迁移率。

为了形成双栅结构,另沉积了一层130纳米厚的SiO2作为顶栅绝缘层。同时,选择钼(Mo)金属接触用于顶栅和底栅偏压。

本仿真模型中使用的材料物理参数如表1所示。随后,态密度(DOS)分布被明确界定并调整,直至实现仿真收敛。探针位于介电层‐沟道界面附近,并与宽度方向对齐。图2展示了本研究中采用的IGZO和ITO的态密度(DOS)模型及模拟参数,这些参数改编自[24, 25, 26],如表2所示。

| 参数 | IGZO | ITO |

|---|---|---|

| 带隙(Eg) | 3.2电子伏特 | — |

| 态密度 电子有效质量 (me) [22, 23] | 0.34 | 0.30 |

| 电子带迁移率 (mp) | 15 cm²/V·s | 35 cm²/V·s |

| 空穴带迁移率 (mp) | 0.1 cm²/V·s | — |

| 电子亲和能 (c) | 4.16 电子伏特 | 4.16 电子伏特 |

| 载流子浓度 (N) | — |

3.63 × 10¹⁴ cm⁻³

3.63 × 10¹⁸ cm⁻³ |

| 参数 | IGZO | ITO |

|---|---|---|

| 峰值密度,施主带尾态 (ntd, cm⁻³/eV) | 1.55 × 10²⁰ | 1.55 × 10²⁰ |

| 峰值密度,受主带尾态(nta,cm⁻³/eV) | 1.21 × 10²⁰ | 2.20 × 10²⁰ |

| 乌尔巴赫能量(施主带尾)(w td ,meV) | 110 | 110 |

| 乌尔巴赫能量(受主带尾)(wta,meV) | 30 | 18 |

| 峰值能量(高斯施主)(Egd,eV) | 2.95 | — |

| 峰值能量(高斯受主)(Ega, eV) | 1.2 | — |

| 峰值密度(高斯施主)(ngd, cm⁻³/eV) | 1.6 × 10¹⁶ | — |

| 峰值密度(高斯受主)(nga, cm⁻³/eV) | 3.2 × 10¹⁷ | — |

| 衰减能量(高斯施主)(wg d, eV) | 0.1 | — |

| 衰减能量(高斯受主)(wg a,eV) | 0.1 | — |

| 界面陷阱密度 (dit, cm⁻³/eV) | 6.0 × 10¹¹ | 6.0 × 10¹⁰ |

3. 结果与讨论

已对双栅三有源层(DG TAL)沟道TFT进行仿真,以分析重叠和偏移长度对器件漏极电流的影响。仿真结果得到了沟道区域场分布的等高线图。图3 显示了在漏极电压VG(top gate) ¼ 0 V、栅极电压VG(bottom V、重叠长度为2毫米,偏移长度分别为1.5毫米和2.5毫米时的场分布情况。从图3可以看出,在栅极与源极/漏极(S/D)电极重叠区域,整个三层有源层(TAL)沟道均处于积累状态;而随着偏移长度增加至1.5毫米和2.5毫米,靠近S/D电极处的积累效应减弱。沿沟道长度方向,导电长度存在显著变化,这一点已清晰体现。

在底部栅极电压恒定时观察到该现象。因此,由于沟道区域偏移处的载流子积累减少,漏极电流降低,且随着偏移长度的增加,这一趋势更加明显。

由于薄膜晶体管(TFT)的性能由电流‐电压特性表征,因此从输出和转移特性曲线中进一步提取了电学参数,如下所示:

TAL‐TFT中的电场:(a) 重叠2毫米;(b) 偏移1.5毫米;(c) 偏移2.5毫米。)

TAL‐TFT中的电场:(a) 重叠2毫米;(b) 偏移1.5毫米;(c) 偏移2.5毫米。)

3.1. 输出特性

施加的栅极电压(VG)在漏极电压(ID)逐渐增加时改变漏极电流(VD)。因此,可得到对应于VG离散值的一系列曲线。图4(a)显示了重叠长度为 2 μm时DG‐TAL沟道TFT的输出特性,底部栅极偏置(VBG)为10伏特,顶栅偏压(VTG)以10伏特为增量,从 -20 V到 +20 V变化。

该图显示了有源区、夹断区和饱和区,以及符合典型晶体管理论的 promising 结果。操作揭示了仅存在微小漏极电流的事实。

存在于 VTG¼ 0V的重叠情况下,正的 VBG产生载流子并诱导形成导电沟道,沟道电导随正的 VTG增大而增加。然而,在另一种情况下,偏移结构在线性区产生更低的关态电流,但在较高的 VTG和 VD时饱和电流略有下降,如图 4 (b)所示。

3.2. 转移特性

用于描述薄膜晶体管(TFT)性能的参数是从转移特性中提取的。转移特性是在漏极电压固定的情况下,通过扫描栅极偏置获得的,所选的漏极电压可确保器件工作在饱和区(fixed drain voltage, selected to ensure that the device working in saturation region (VD VG- VTH)。图5 显示了双栅极偏置下具有重叠(2 μm)和偏移(1.5 μm)结构的器件的转移特性。从图5(a)中可以观察到,当栅极电压超过某一阈值电压后,漏极电流呈指数上升。随着阈值电压增加,沟道变宽,允许更多电荷在薄膜晶体管的源极和漏极之间通过,从而使电流增大。在电极之间存在偏移的情况下,如图5(b)所示,关态电流较低;而由于导电长度较大,重叠结构表现出更高的漏极电流。

3.3. 电学参数的提取

描述TFT性能的不同参数包括field-effect迁移率(mFE)、电流比(ION/IOFF)、阈值电压(VTH)以及亚阈值摆幅,这些参数均从I‐V特性曲线中提取。 mFE代表薄膜晶体管在器件工作线性区的漏极电流所确定的沟道迁移率,如 film中的公式(1)所示。

$$ ID ¼ mFE \cdot CDG \cdot \frac{W_{ch}}{L_{ch}} \cdot (VG - VTH) \cdot VDS \quad (1) $$

其中,Wch和Lch分别为薄膜晶体管(TFT)沟道的宽度和长度,CDG为单位面积栅极电容。

在双栅结构中,形成了两个电容区域,一个位于沟道与顶栅之间,另一个位于沟道与底部栅极之间,分别为CTG和CBG,其值取决于厚度。如果顶栅和底部栅极的介电层厚度分别为dTG和dBG,介电常数分别为 εTG和 εBG,则CTG ¼ εTG/dTG,且CBG ¼ εBG/dBG。双栅结构中的电容(CDG)无法直接确定,但可近似为CTG和CBG之和,因为这两个电容总体上是并联形成的[27]。因此,CDG ¼ CTG þ CBG。

亚阈值斜率(SS)如公式(2)所示,是MOS器件特性在转移特性线性部分的斜率[26]。

$$ SS ¼ \left( \frac{\partial \log ID}{\partial VG} \right)^{-1} \quad (2) $$

基于电容模型推导的双栅TAL薄膜晶体管结构的亚阈值摆幅参数[28]通过公式(3)计算。

$$ SS_y ¼ \frac{kT}{q} \ln 10 \cdot \left( 1 + \frac{CBI + CTI}{CBG + CTG} \right) \quad (3) $$

其中,k、T 和 q 分别为玻尔兹曼常数、温度和电子电荷,CBI 和 CTI 为底部和顶部沟道界面态电容。CBI 和 CTI 定义为 CBI ¼ q·NBIT 和 CTI ¼ q·NTIT,其中 NBIT 和 NTIT 表示底部和顶部界面陷阱态密度。平均界面陷阱态密度(NIT)可假定等于 NBIT 和 NTIT。

ION/IOFF是描述TFT开关效率的定量指标,表示在不同栅极电压下工作的最大电流与最小电流之比,可通过评估转移特性中的漏极电流来确定。DG TAL TFT在重叠和偏移结构下的提取参数以及与共面双栅TFT的比较结果列于表3中。相比之下,DG TAL TFT的结果显示,在双栅偏置VTH下,亚阈值摆幅在重叠结构中为0.28 V,在偏移结构中为0.06 V,显著更低;迁移率 mFE在重叠结构中高出3 cm²/Vs,且获得了相当的ION/IOFF,以及亚阈值摆幅(SS)。

3.4. 双栅极三有源层薄膜晶体管在AMOLED像素电路中的应用

在AMOLED像素电路中,a‐IGZO薄膜晶体管因其显著的优势(如高迁移率、稳定性和低温工艺)而备受关注。已提出采用双栅薄膜晶体管的AMOLED像素驱动电路,以克服单栅薄膜晶体管的电学不稳定性问题,这种不稳定在持续栅极偏压应力下会导致阈值电压漂移。VTH漂移会引起显著的有机发光二极管电流退化和亮度劣化。因此,过去已引入使用双栅薄膜晶体管的电路来实现阈值漂移补偿[29, 30, 31, 32]。a‐IGZO薄膜晶体管中的双栅结构表现出更优异的特性,包括高的ION电流、显著的亚阈值摆幅以及对阈值电压的良好控制。一种传统的像素电路采用双栅由两个薄膜晶体管(TFT)和一个电容器组成,如图6(a)[33]所示,其中一个为T1(开关薄膜晶体管),另一个为T2(驱动薄膜晶体管)。在编程间隔期间,T1导通与关断,电容器充电至数据电压水平。在其导通状态时,T2根据电容器(CSTO)电压向有机发光二极管提供恒定电流。如果电容器在编程间隔内未能完全充电,则会导致显示错误。因此,开关薄膜晶体管必须具有较高的ION/IOFF比,以实现更快的开关速度。由于所设计的偏移结构双栅极三有源层薄膜晶体管(DG‐TAL TFT)表现出较低的关态电流以及优异的电学参数,这将显著提升像素电路中电容器的充电性能。图6(b) 所示为采用双栅极三有源层薄膜晶体管(DG‐TAL TFT)的AMOLED像素电路,该电路包含两个双栅极三有源层薄膜晶体管(DG‐TAL TFT)和一个电容器,分别作为开关、驱动和存储元件。为了独立偏置顶栅以实现对阈值电压更好的控制,需要增加一条额外的控制线。因此,在所提出的AMOLED像素电路中,添加了一个包含一个电容器(CC)、一个顶栅三层有源层(TAL)薄膜晶体管和两条控制线的子电路,以实现对阈值电压的良好控制及补偿功能。

4. 结论

在具有双栅结构的非晶铟镓锌氧化物薄膜晶体管中,设计并仿真了三有源层沟道,以研究偏移长度对漏极电流的影响。所提出的双栅极三有源层薄膜晶体管在栅极与源漏(S/D)电极重叠长度为2毫米时,在顶栅、背栅和双栅偏置条件下分别表现出较高的场效应迁移率(mFE)12.79、13.82 和 16.08 cm²s/Vs。同时,当偏移长度为1.5毫米时,迁移率mFE分别降低至4.2、9.11 和 6.07 cm² s/V‐s。对所提出双栅结构的性能分析揭示了电极重叠与偏移对电学参数的影响。尽管由于器件沟道设计的原因亚阈值特性较差,但该双栅极三有源层薄膜晶体管仍表现出优异特性,且在双栅偏置条件下与先前报道的器件结构相当,因此适合作为开关晶体管被提出。最后,一种新颖的已提出使用双栅三有源层(DG TAL)沟道IGZO薄膜晶体管(TFT)的AMOLED像素电路。其他电学参数得到显著改善,有助于克服亮度衰减和VTH偏移补偿问题。未来可进一步优化该器件结构的亚阈值摆幅(SS)。此外,还可探索采用DG‐TAL TFT的电路在射频电路和薄膜天线电路设计中的性能分析film电路设计 [34, 35]。

66

66

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?