地址空间_RISC与CISC

ARM中怎么访问寄存器?就像访问内存一样

怎么访问寄存器?用指针:

unsigned int *p = 0x40010800; // p等于某个寄存器的地址

*p = val; // 写这个地址,也就是写这个寄存器

val = *p; // 读寄存器

int a;

unsigned int *p = &a; // p等于“a的地址”

*p = val; // 写这个地址,就是写a

val = *p; // 读这个地址,就是读a

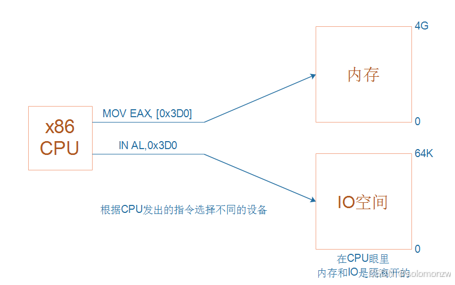

在ARM CPU看来,内存,IO的操作是一样的

在X86架构中内存和IO是分开的

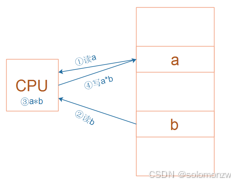

RISC

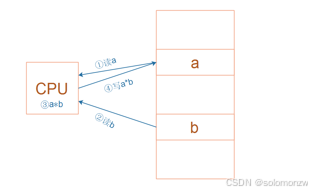

ARM芯片属于精简指令集计算机(RISC:Reduced Instruction Set Computing),它所用的指令比较简单,有如下特点:

① 对内存只有读、写指令

② 对于数据的运算是在CPU内部实现

③ 使用RISC指令的CPU复杂度小一点,易于设计

对于左图所示的乘法运算a = a * b,

在RISC中要使用4条汇编指令:

① 读内存a

② 读内存b

③ 计算a*b

④ 把结果写入内存

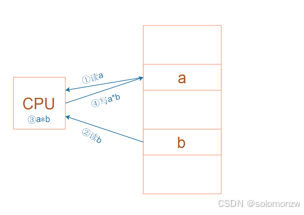

CISC

x86属于复杂指令集计算机(CISC:Complex Instruction Set Computing),

它所用的指令比较复杂,比如某些复杂的指令,它是通过“微程序”来实现的。

比如执行乘法指令时,实际上会去执行一个“微程序”,

在“微程序”里,

一样是去执行这4不操作:

① 读内存a

② 读内存b

③ 计算a*b

④ 把结果写入内存

但是对于程序员来说,

他看不到“微程序”,

他好像用一条指令就搞定了这一切!

RISC和CISC比较

CISC的指令能力强,单多数指令使用率低却增加了CPU的复杂度,指令是可变长格式;

RISC的指令大部分为单周期指令,指令长度固定,操作寄存器,对于内存只有Load/Store操作CISC支持多种寻址方式;

RISC支持的寻址方式CISC通过微程序控制技术实现;

RISC增加了通用寄存器,硬布线逻辑控制为主,采用流水线CISC的研制周期长RISC优化编译,有效支持高级语言

好的!我用生活化的比喻帮你理解CISC和RISC的区别:

CISC(复杂指令集)

👉 像一个瑞士军刀:

- 功能多(一条指令能完成复杂操作,比如直接操作内存数据),但很多功能不常用。

- 设计复杂(刀上各种小工具互相干扰,增加制造难度),研发周期长。

- 操作步骤不固定(指令长度可变,像不同大小的快递包裹,分拣起来麻烦)。

- 支持多种“找东西”方式(寻址方式),比如直接算地址、间接找地址等。

- 控制原理像“说明书”(微程序控制:用预先写好的代码解释复杂指令)。

典型代表:Intel的x86架构(家用电脑CPU)。

RISC(精简指令集)

👉 像一个高效流水线工厂:

- 只保留最常用的功能(指令简单,大部分1个时钟周期完成),比如操作寄存器,内存只能通过专门的Load/Store指令访问。

- 设计简单(指令长度固定,像统一规格的零件,流水线处理超快)。

- 支持少数高效的“找东西”方式(寻址方式少,比如直接算地址)。

- 控制原理像“自动化流水线”(硬布线逻辑:电路直接执行指令,速度快)。

- 编译器优化强(像智能流水线调度员,能帮高级语言生成高效代码)。

典型代表:ARM架构(手机/平板芯片)、RISC-V(新兴开源架构)。

对比总结

| 场景 | CISC | RISC |

|---|---|---|

| 指令复杂度 | 复杂,能直接操作内存 | 简单,只能操作寄存器 |

| 设计理念 | "多功能但笨重" | "少而精,追求速度" |

| 适用场景 | 传统PC(需要兼容复杂指令) | 移动设备、嵌入式(省电高效) |

| 现代发展 | 二者界限模糊(比如Intel也用流水线) |

打个比方:

CISC像老教授——知识渊博但反应慢;

RISC像体育生——专注几个动作,但速度爆发力强!

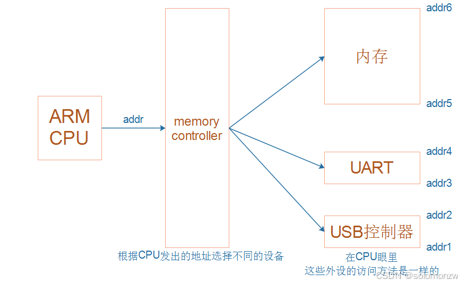

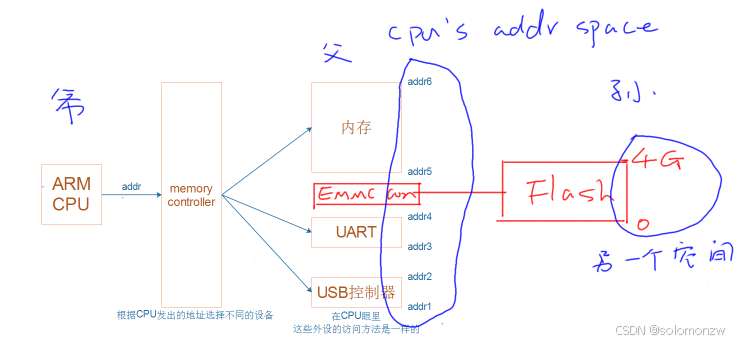

这张图描述了 CPU 与各种外设或存储器之间是如何通过“地址”联系起来的。可以把它理解成:

-

CPU 拥有一个统一的“地址空间”(图中右边标注了 0~4GB):

- 对 32 位 CPU 来说,所有的地址都在这 4GB 范围内。

- 不管是访问内存、访问 eMMC/Flash 还是访问其他外设(UART、USB 控制器),在 CPU 看来都是在读写某个“地址”。

-

内存控制器(Memory Controller) 就像一个“交通枢纽”或“分配中心”:

- 当 CPU 发出对某个地址的访问请求时,内存控制器会根据地址范围来决定,这次访问到底应该路由到内存、还是 eMMC、还是其他外设。

- 例如:

- 如果地址在某个区间(比如 0x8000_0000 ~ 0x8FFF_FFFF),就映射到内存;

- 如果地址在另一个区间(比如 0x9000_0000 ~ 0x9FFF_FFFF),就映射到 eMMC;

- 再比如 0x1000_0000 ~ 0x1000_FFFF 可能映射到 UART 寄存器;

- …等等。

-

eMMC / Flash / 外设(UART、USB 控制器) 只是在地址空间中占了一部分区域:

- CPU 通过读写对应地址,就能控制或获取这些外设的数据。

- 从 CPU 的角度看,它只是在访问一段内存地址;

- 实际上,访问请求被内存控制器转发给了真正的硬件(eMMC、UART、USB 等等)。

-

为什么说“父”是 CPU 的地址空间,“子”是 eMMC、Flash 等?

- 可以理解为:CPU 的地址线是“父级”,而各种硬件设备是“子级”。

- 这些硬件都挂在 CPU 的地址总线上,不同的地址段对应不同的硬件。

- CPU 只认地址,不直接知道具体是哪块硬件——由内存控制器来“做翻译”和“分配”。

通俗比喻

- 想象 CPU 是一个人,他只有一个“电话本(地址空间)”,里面记录了 0~4G 的号码(地址)。

- 内存控制器 像一个“电话总机”或“前台”,当 CPU 拨打某个号码(读写某个地址)时,前台决定把这通电话接到“内存”部门,还是“eMMC”部门,还是“UART”部门。

- 对 CPU 而言,他只知道“我在打某个号码”,并不知道背后是具体哪位接电话(哪块硬件响应)。

- 最终,不同号码对应了不同硬件,就像不同分机

- CPU 只有一套统一的 4GB 地址空间(因为是 32 位)。

- 内存控制器 负责把不同地址段映射到不同硬件(内存、eMMC、Flash、UART、USB 控制器等)。

- 对 CPU 来说,读写某个地址就是读写某块硬件;对硬件来说,只在特定地址段上做出响应。

- 这就是嵌入式系统中常见的“总线 + 地址映射”机制。

eMMC 就是一块把 Flash 存储和控制器封装在一起的“小硬盘”,系统只需用标准协议去读写它,既省空间又减少软件开发难度,广泛用于手机、平板等嵌入式设备。

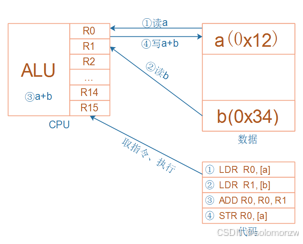

ARM内部寄存器

RISC

ARM芯片属于精简指令集计算机(RISC:Reduced Instruction Set Computing),它所用的指令比较简单,有如下特点:

① 对内存只有读、写指令

② 对于数据的运算是在CPU内部实现

③ 使用RISC指令的CPU复杂度小一点,易于设计

对于左图所示的乘法运算a = a * b,

在RISC中要使用4条汇编指令:

① 读内存a

② 读内存b

③ 计算a*b

④ 把结果写入内存

问题:在CPU内部,用什么来保存a、b、a*b ?

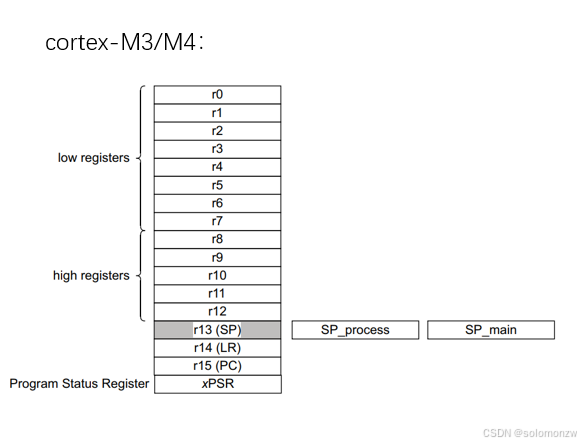

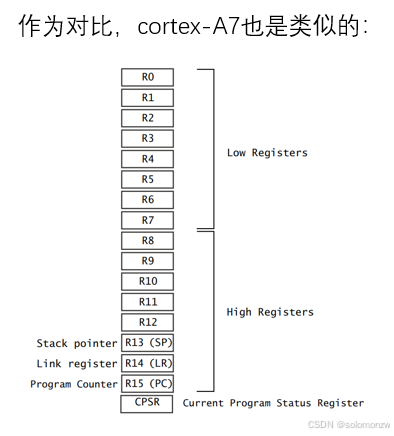

无论是cortex-M3/M4,还是cortex-A7,

CPU内部都有R0、R1、……、R15寄存器;

它们可以用来“暂存”数据。

对于R13、R14、R15,还另有用途:

R13:别名SP(Stack Pointer),栈指针

R14:别名LR(Link Register),用来保存返回地址

R15:别名PC(Program Counter),程序计数器,表示当前指令地址,写入新值即可跳转

M3/M4/A7 CPU内部寄存器

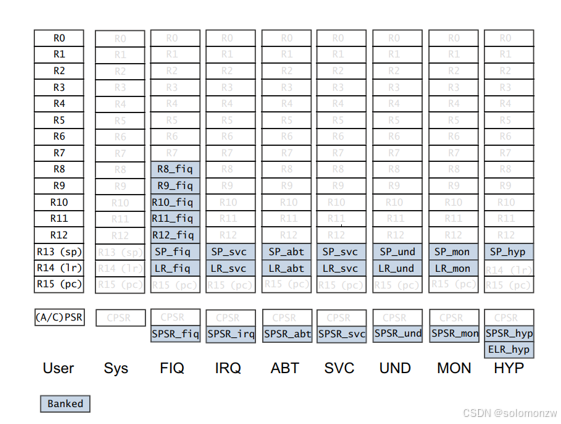

好的!我用生活化的比喻来解释这张图中的寄存器结构,保证你5分钟就能看懂:

1. 寄存器银行 = 快递柜 + 急救包

想象你的手机/电脑里有一个「超级快递柜」,柜子分成不同颜色的格子(对应不同处理器模式)。每个格子里的快递盒(寄存器)有的通用(比如R0-R7),有的专用(比如R15是程序计数器),还有的格子放了「急救包」(特殊寄存器CPSR/SPSR)。

2. 为什么要分这么多模式?

👉 就像你生活中不同场合用不同工具:

- 用户模式(User):日常搬砖模式,只能用普通快递盒(R0-R15),权限低。

- 中断模式(IRQ/FIQ):突然有紧急电话(比如你按了音量键),系统立刻切换到「中断快递柜」,用专属快递盒(R8_fiq/R9_fiq等),避免和日常搬砖的数据搞混。

- 超级用户模式(SVC):管理员模式,能调用高级权限(比如安装App)。

- 其他模式(ABT/UND等):类似「应急通道」,处理程序崩溃、未知指令等意外。

3. 重点看「FIQ快递柜」的特殊设计

快速中断模式(FIQ)的格子最特别:

- 专属快递盒:R8_fiq到R14_fiq,专门给紧急任务用。

- 不排队:普通中断(IRQ)要和其他程序抢快递盒,FIQ直接用自己的,响应速度更快。

- 类比:普通快递员要排队进小区,FIQ快递员有专属通道,随叫随到!

4. 底部的「急救包」是做什么的?

特殊寄存器CPSR和SPSR就像「急救包」:

- CPSR:记录当前状态(比如你是用户模式还是中断模式)。

- SPSR_xxx:每次切换模式时,把原来的状态存档(比如从用户模式切到IRQ模式,存档用户模式的CPSR到SPSR_irq)。

- 类比:你突然被叫去开会,先拍一张工位照片存档(SPSR),回来时按照片恢复现场。

终极总结

| 组件 | 生活比喻 | 作用 |

|---|---|---|

| R0-R12 | 通用快递盒 | 日常搬砖存数据 |

| R13(SP) | 临时货架管理员 | 记录当前货架(栈)的位置 |

| R14(LR) | 返程机票 | 记录执行完任务后要回哪里 |

| R15(PC) | 任务清单指针 | 指向下一条要执行的指令 |

| CPSR/SPSR | 工位状态存档照片 | 保存和恢复处理器状态 |

一句话理解:

处理器像一家快递公司,不同场景(模式)用不同的快递柜(寄存器),紧急任务(FIQ)有专属通道,急救包(CPSR)随时存档恢复现场,保证高效不乱套!

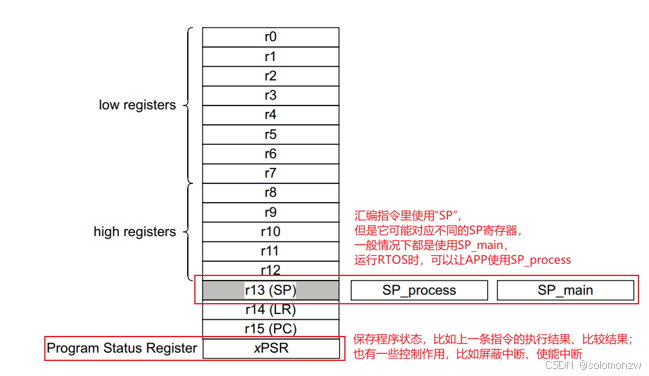

M3/M4比较两个数是,结果并保存在哪里

对于cortex-M3/M4,还要一个Program Status Register

M3/M4:xPSR实际上对应3个寄存器APSR/IPSR/EPSR

对于cortex-M3/M4来说,

xPSR实际上对应3个寄存器:

① APSR:Application PSR,应用PSR

② IPSR:Interrupt PSR,中断PSR

③ EPSR:Exectution PSR,执行PSR

这3个寄存器的含义如右图所示

这3个寄存器,可以单独访问:

MRS R0, APSR ;读APSR

MRS R0, IPSR ;读IPSR

MSR APSR, R0 ;写APSR

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1505

1505

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?