9 射频集成电路设计

1 引言

未来互联网,如今被称为“物联网(IoT)”,预计将发展成为一个基于标准通信协议的全球互联物体网络,其中每个物体都具有唯一可寻址性。通过唯一的地址标识,包括计算机、传感器、射频识别(RFID)标签或手机在内的任何物体都将能够动态地接入网络,并高效协作以完成各种任务。预计在未来几年内,将有数十亿台设备连接到全球网络。这也引发了人们对通信网络不断增长的能耗足迹可持续性的担忧。

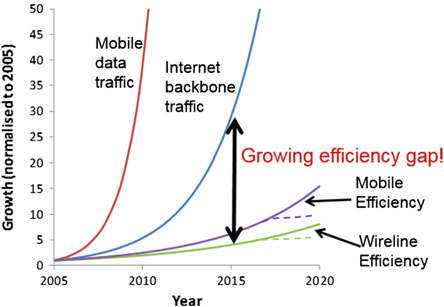

图1展示了我们在努力实现互联网和信息与通信技术可持续发展过程中所面临的挑战[1]。该图显示,移动流量和互联网骨干网的每年增长分别为108%和34%。而有线网络和移动网络在能效提升方面的趋势仅为每年15%和20%。我们看到,流量增长远远超过了能效改进的速度。这一差距被称为“能效差距”。除非能够弥补这一差距,否则在物联网时代的到来之际,互联网和信息与通信技术的长期可持续性将无法实现。科学家和研究者已从器件级和电路级开发并集成了绿色技术,以应对这一挑战[2, 3]。

作为物联网生态系统中的主要成员之一,射频识别设备与信用卡或产品标签上的条形码或磁条具有相同的作用,即为该物体提供一个唯一标识符。考虑到射频识别设备的数量和成本,我们需要优化其功耗,简化其架构,并在保持卓越性能以满足所有设计规格的同时,尽可能减小芯片尺寸。在其射频收发器上应用新技术是最基本的方法之一。

2 射频识别接收机的射频架构示例

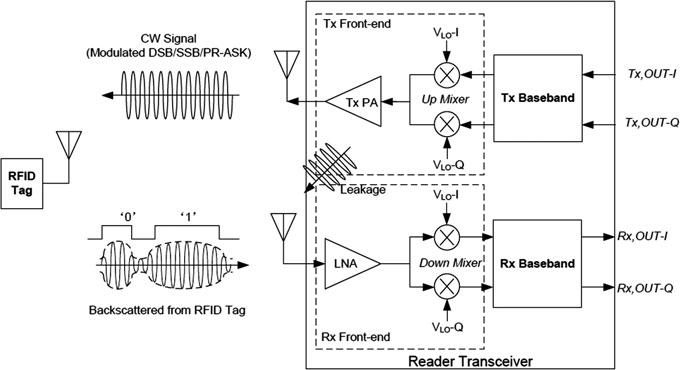

在所有射频接收器架构拓扑中,直接转换接收机(也称为同相检波接收机或零中频接收机)因仅需一个混频级即可实现信号转换,被广泛应用于低功耗应用中。由于混频器通常占据接收机前端’功耗的最大比例,较少的混频级意味着更低的功耗。图2展示了典型射频应用中的直接转换架构拓扑。为克服混频边带镜像问题,许多近期的射频接收器采用了具有频率调制结构的同相/正交(I/O)转换。

本次讨论中,我们以该拓扑结构为例用于射频识别接收机设计,以在功耗、线性度、噪声和灵敏度之间提供良好的折衷。

随着晶体管尺寸进入深亚微米区域,不仅难以维持制造精度,还给射频设计工程师准确仿真和预测器件性能带来了挑战。使用复杂的设计模型会带来显著的时序和开发成本。包含有限漏源电导(gds)效应的模型能够在保持纳米级设计实际简化模型的同时,显著提高仿真精度。这是因为对于低功耗深纳米级CMOS器件而言,输出电导已不再能相对于跨导(gm)忽略不计。我们在所提出的射频模拟前端设计中考虑了gds的影响,包括低噪声放大器(LNA)、正交混频器以及压控振荡器(VCO)。

3 射频识别接收机低噪声放大器设计示例

作为接收机前端链路中的第一个模块,低噪声放大器(LNA)决定了接收机的噪声系数(NF),换句话说,它反映了系统的灵敏度和误码率。针对不同的应用,存在多种类型的低噪声放大器,如窄带、多频带和宽带LNA。射频识别(RFID)应用通常基于指定频率,因此,在我们的射频识别读写器设计示例中,采用了一个在特定频率上调谐的窄带低噪声放大器。若干优化已经针对窄带低噪声放大器在功耗、噪声和阻抗匹配方面的技术进行了开发[5, 6]。一种提出的增强型功率受限同时噪声与输入匹配技术(PCSNIM)被用作示例,以演示如何在极低的功耗和电源条件下同时实现阻抗匹配和最小噪声匹配[4]。

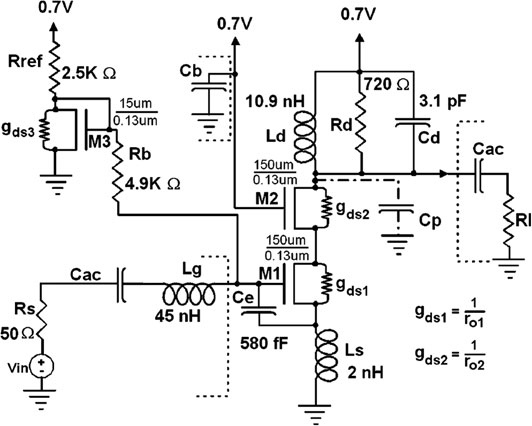

图3显示了基于增强型PCSNIM技术的超高频(UHF)射频识别低噪声放大器的电路图。M1与Ls构成输入级电感源退化放大器器件,通过考虑栅极输入产生一个无噪声电阻分量,以实现与源电阻的匹配。Lg是用于共轭复数输入电抗匹配的外部电感。Ce是便于低功耗设计匹配的外部电容。对于低功耗深纳米级CMOS器件,有限输出电导(gds= 1/ro)与MOS器件并联显示。Ld、Rd和Cd构成工作频率处调谐的输出谐振电路,且Ld和Cd的相对值被仔细选择,以防止漏极寄生电容使M2的谐振电路失谐。输入端和输出端的Cac为交流耦合电容,而Cb是共源共栅器件M2栅极上的交流接地电容。M3与Rref共同控制通过折叠式共源共栅的偏置电流,而较大的Rb确保电流镜器件M3栅极处的噪声和任何交流信号拾取大部分与M1栅极处的射频输入解耦。

| CMOS工艺 (nm) | 隔离 S11(dB) | 电压增益 S21 (dB) | NF (dB) | 线性度 输入三阶截点/1分贝压缩点 (dBm) | PDC (mW) | 电源电压 (V) | FOM | |

|---|---|---|---|---|---|---|---|---|

| 本工作 [4] | 130 | −30 | 17 | 2.2 | −11.5/−16.1 | 0.85 | 0.7 | 12.66 |

| [7] | 250 | −18 | 12 | 1.35 | −4/−15 | 2 | 1.25 | 5.45 |

| [8] | 350 | −11 | 13.4 | 3.2 | 10.8/1/4 | 33 | 3.0 | 1.299 |

| [9] | 180 | N/A | 15 | 2.9 | N/A/−15 | 4.32 | 1.8 | 1.37 |

表1 所提出的特高频射频识别低噪声放大器性能总结及其与其他方案的比较

如表1[5]中的比较所示。PDC是LNA的直流功耗。该品质因数清楚地表明了所提出的射频识别低噪声放大器设计相较于其他设计的优势。

FOM[mW⁻¹] = |Gain| / (NF − 1) × PDC⁻¹/²[mW]

4 射频识别接收机混频器设计示例

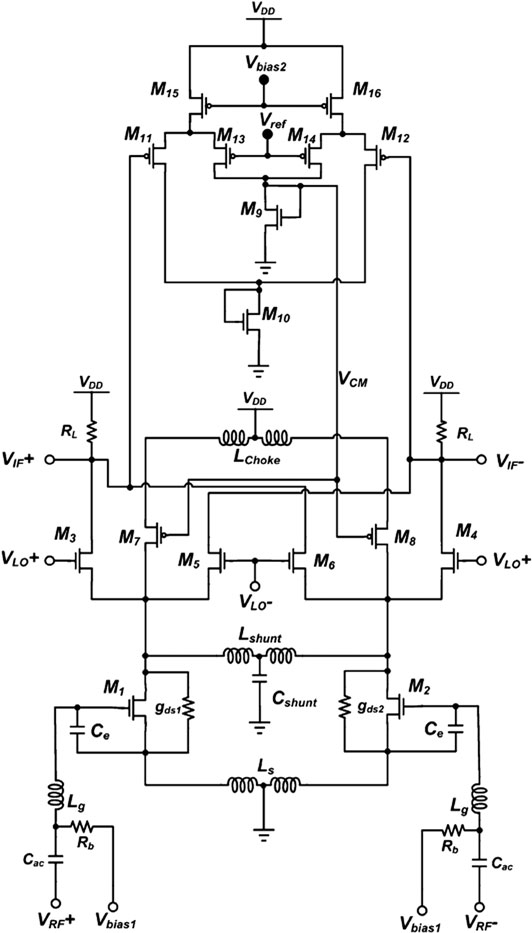

混频器用于在射频(RF)和中频(IF)频谱之间转换基带信息,是任何射频前端的关键组成部分。由于具有高度集成、低成本以及简单的基带架构,直接转换接收机(DCR)架构在物联网(IoT)应用设计中备受青睐。双平衡混频器特别适用于直接转换接收机,因其具有较低的射频和本振泄漏,以及较高的本振到中频隔离度。为了优化功耗、闪烁噪声、热噪声、转换增益和线性度之间的整体性能,已探索了多种技术。电流分流技术通过最小化流过开关器件的直流电流,降低了开关级对闪烁噪声的贡献[10]。然而,泄放电流源的缺点是增加了尾部电容,这不仅降低了共模抑制能力(导致非线性),还间接加剧了闪烁噪声。另一方面,在该拓扑结构中,由于电流源(pMOS器件)的漏极具有高输出阻抗,大部分射频信号电流被迫流入开关对的低阻抗源支路。然而,由于有限的gds效应,在纳米级CMOS工艺中信号泄漏至电流分流器的程度更高,需进一步改进以提升转换增益。从热噪声预算的角度来看,跨导器占据了其中相当大的比例。采用电感退化合并式低噪声放大器作为跨导器器件,可显著降低该噪声。

一种采用新型电感退化电流分流器件和谐振尾部电容调谐技术以及匹配输入的改进型混频器

本次报告提出了一种用于RFID读取器接收机的合并式LNA/跨导器级。同时还实现了共模互调反馈,以提高针对直流电平(器件过驱动)扰动的线性度。

9 射频集成电路设计

5 射频识别接收器中压控振荡器设计的一个实例

任何射频前端中的压控振荡器都会消耗其功率预算的相当大一部分。因此,在压控振荡器设计中,平衡功耗、调谐范围、调谐增益和相位噪声之间的权衡至关重要。此外,为调制和解调中的镜像抑制而设计正交压控振荡器(QVCO)时,必须考虑正交误差以及其与相位噪声和其他性能参数之间可能的折衷。正交误差可能导致下变频后的基带混频器输出中残留镜像信号。目前有多种QVCO设计技术,其中最著名的方法是利用两个LC压控振荡器的交叉和直接耦合[15]。耦合和偏置技术在实现低相位噪声和低正交误差的LC正交压控振荡器(LC‐QVCO)中起主导作用。

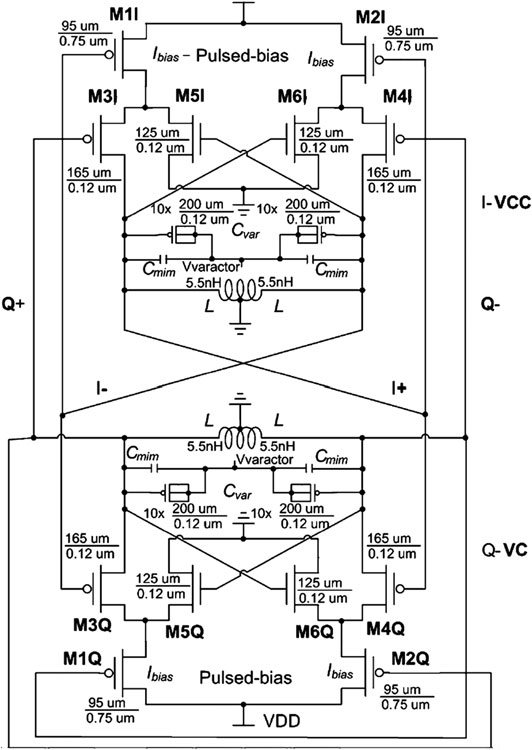

图5展示了我们RFID设计中用于两个正交耦合LC压控振荡器的改进型LC正交压控振荡器架构,该架构采用了改进的耦合和偏置技术[16]。端口I+、I−以及Q+、Q−分别为I路压控振荡器和Q路压控振荡器的正交输出及其互补信号。为了提高正交压控振荡器信号的频谱纯度,引入了变压器耦合,但其代价是在特高频应用中占用较大的硅面积。因此,在本设计示例中,采用pMOS折叠共源共栅结构为正交信号生成提供相互输入激励。与并联正交耦合相比,使用共源共栅拓扑的串联耦合降低了正交压控振荡器的相位噪声。

此外,由于折叠式共源共栅中的pMOS器件具有较低的热载流子引起的漏极电流噪声,进一步提升了相位噪声性能。LC谐振槽采用接地中心抽头电感,以在混合信号应用中实现电源噪声抑制和线性度改善。此外,由于采用中心接地方式,电感线圈产生的衬底泄漏电流也有所减少。这还使得正交压控振荡器相比采用电源中心抽头或浮空线圈的其他拓扑结构更不易发生自谐振。

压控振荡器核心正反馈nMOS锁存器的尾电流源被取消,从而提供了额外的电压裕度。因此,该设计可在高度缩放的供电电压下仍能实现振荡。为共源共栅耦合拓扑提供偏置的pMOS电流源相较于nMOS偏置电流源具有更低的漏极电流噪声,因其本身噪声特性更优。为进一步降低pMOS电流源的噪声,本设计中采用通过互补交叉耦合的脉冲偏置技术,以释放nSi‐SiO界面处被俘获的载流子。通过在积累区和强反型区之间脉冲切换MOSFET过驱动状态,可释放强反型期间被俘获的载流子,从而降低噪声。耗尽型pMOS(D‐PMOS)器件被用作变容二极管,因其在此工作区域具有近似线性的单调电容‐电压(C–V)特性。多个器件并联连接以增大组合C–V调谐范围。此外,还将小值金属‐绝缘体‐金属(MIM)电容与D‐PMOS阵列并联,以进一步提高整体变容二极管线性度。图1还显示了D‐PMOS变容二极管的直流连接极性,其栅极连接至直流地,而源极、漏极和体端短接并连接至一个可变的正电压。在此拓扑结构中,M5和M6构成VCO的核心反馈锁存器件,而M3和M4则是相应的耦合pMOS器件。流入LC谐振槽的电流仅来自pMOS耦合器件的漏极电流。由于只有一组偏置晶体管从供电电压消耗漏极电流,因此与传统交叉耦合再生电路相比,工作供电电压和功耗可显著降低。

调谐会改变总等效电容(Cov_eq),该电容由槽电容(Cvar)以及耦合pMOS器件的漏极与地之间所呈现的电容组成。在大信号操作下,由于无尾电流接地的nMOS锁存电路中,pMOS共源共栅器件和交叉耦合的nMOS器件被交替脉冲驱动进入积累区(关断)和强反型区(导通的三极管区),从而也降低了这些器件的闪烁噪声贡献。pMOS偏置器件和nMOS锁存器件的有限跨导ds同样对pMOS耦合器件起到跨导退化作用,导致其跨导降低,进而进一步减小了它们对相位噪声的白噪声贡献。此外,在该结构中,耦合器件和再生器件在直流工作时基本是并联的,但在交流(大信号非线性)工作时形成共源共栅结构,从而使该结构兼具低相位噪声和低正交误差[10]的优点。

此外,由于持续振荡仅发生在负阻的平均幅度等于LC谐振槽并联电阻的频率上,因此该电路不会出现双模振荡。

| 技术工艺 (nm) | 调谐范围 (%) | 相位噪声 (dBc/Hz) @1 MHz | DC功率 (mW) | 电源电压 (V) |

|---|---|---|---|---|

| 本研究 [16] | 130 | 8% | −130 | 2.5 |

| [17] | 180 | 4.6% | −111 | 2.2 |

| [18] | 180 | N/A | −124 | 8.7 |

| [19] | 130 | N/A | −118 | 3.7 |

| [20] | 130 | N/A | −112 | 4.8 |

表3 所提出的特高频射频识别正交压控振荡器性能与其他混频器设计的比较总结

在仅消耗2.5毫瓦功率的情况下,载波频率偏移1兆赫兹处的单边带相位噪声为−130 dBc/Hz,与近期发表的设计相比,该性能具有很强的竞争力。

6 射频识别接收机接收器设计总结

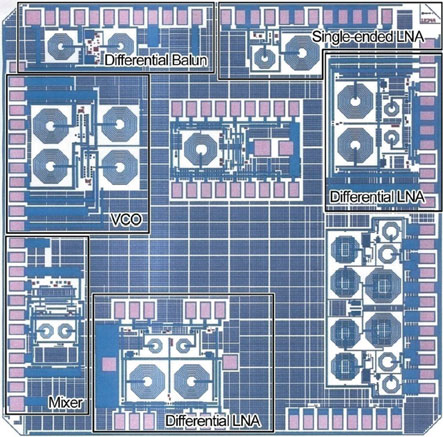

基于IBM 130纳米CMOS工艺,提出了一种用于物联网射频识别应用的完整射频接收器前端。图6显示了所提出的射频前端的完整布局图,包括单端LNA、差分LNA、低噪声放大器合并混频器、正交压控振荡器和差分巴伦。

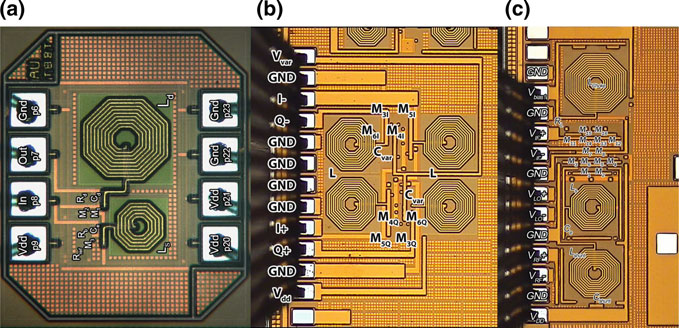

每个组件的芯片图如图7所示。整个接收机在1.2伏特供电电压下消耗的功率小于9毫瓦。

365

365

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?